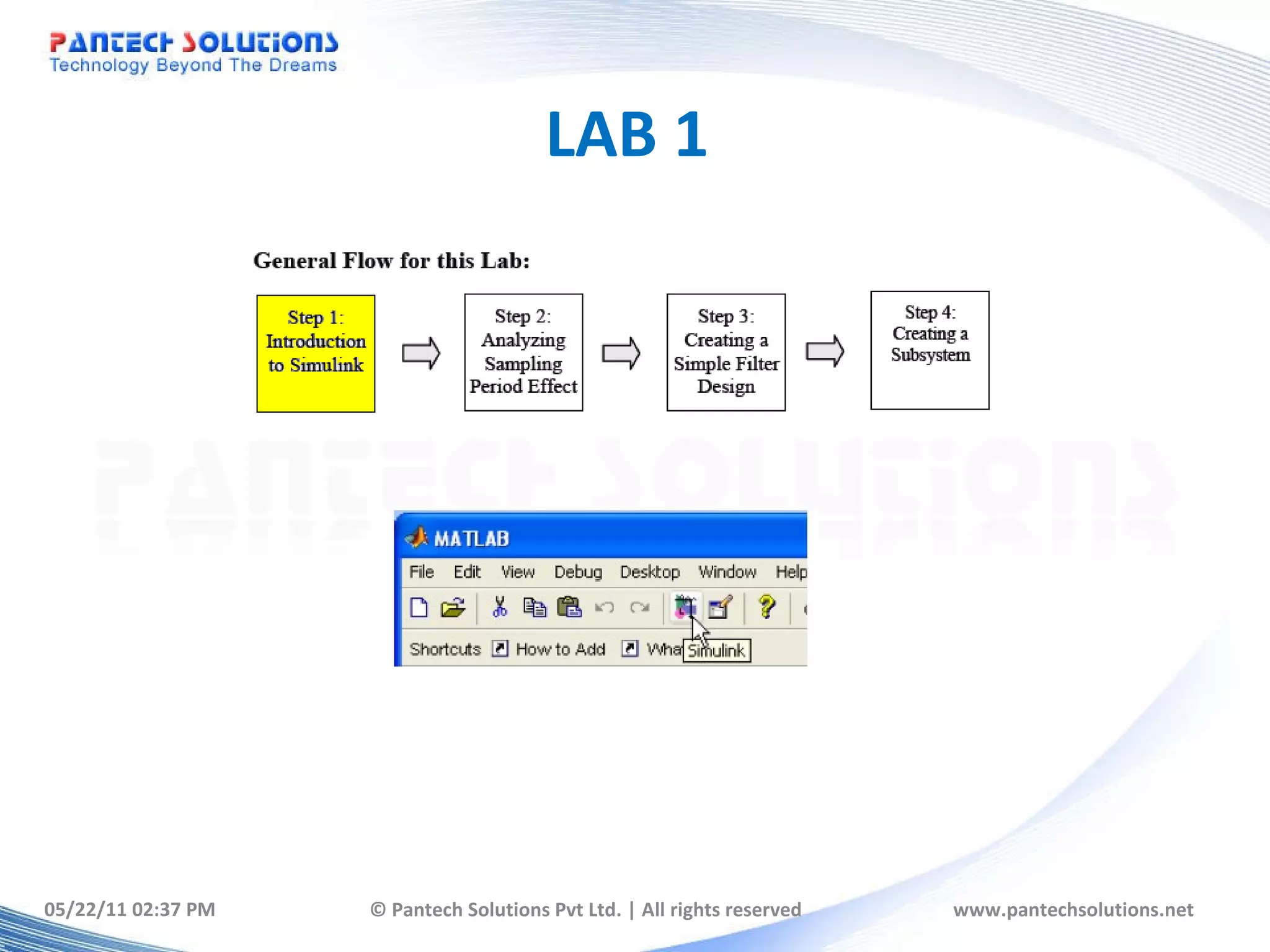

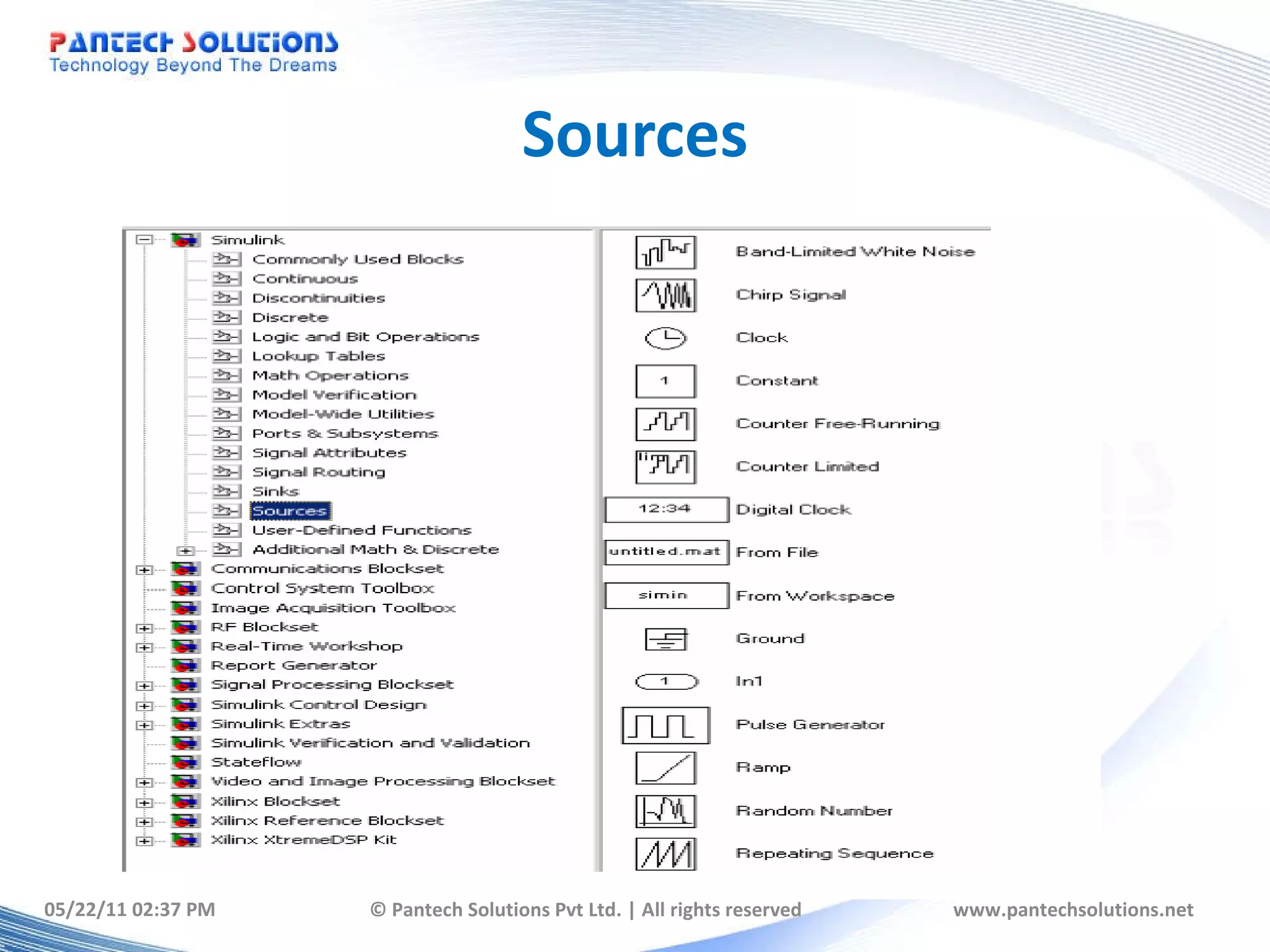

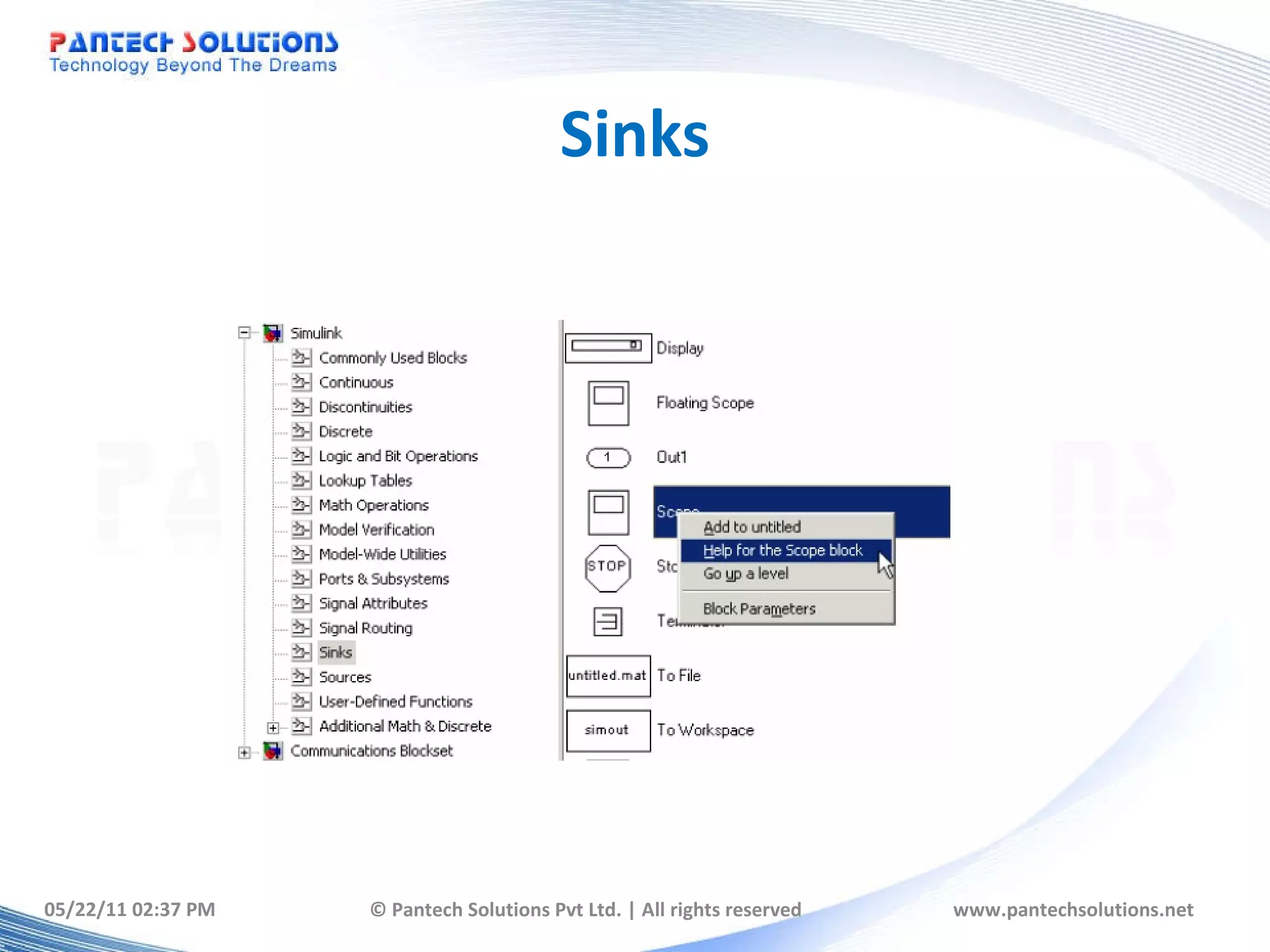

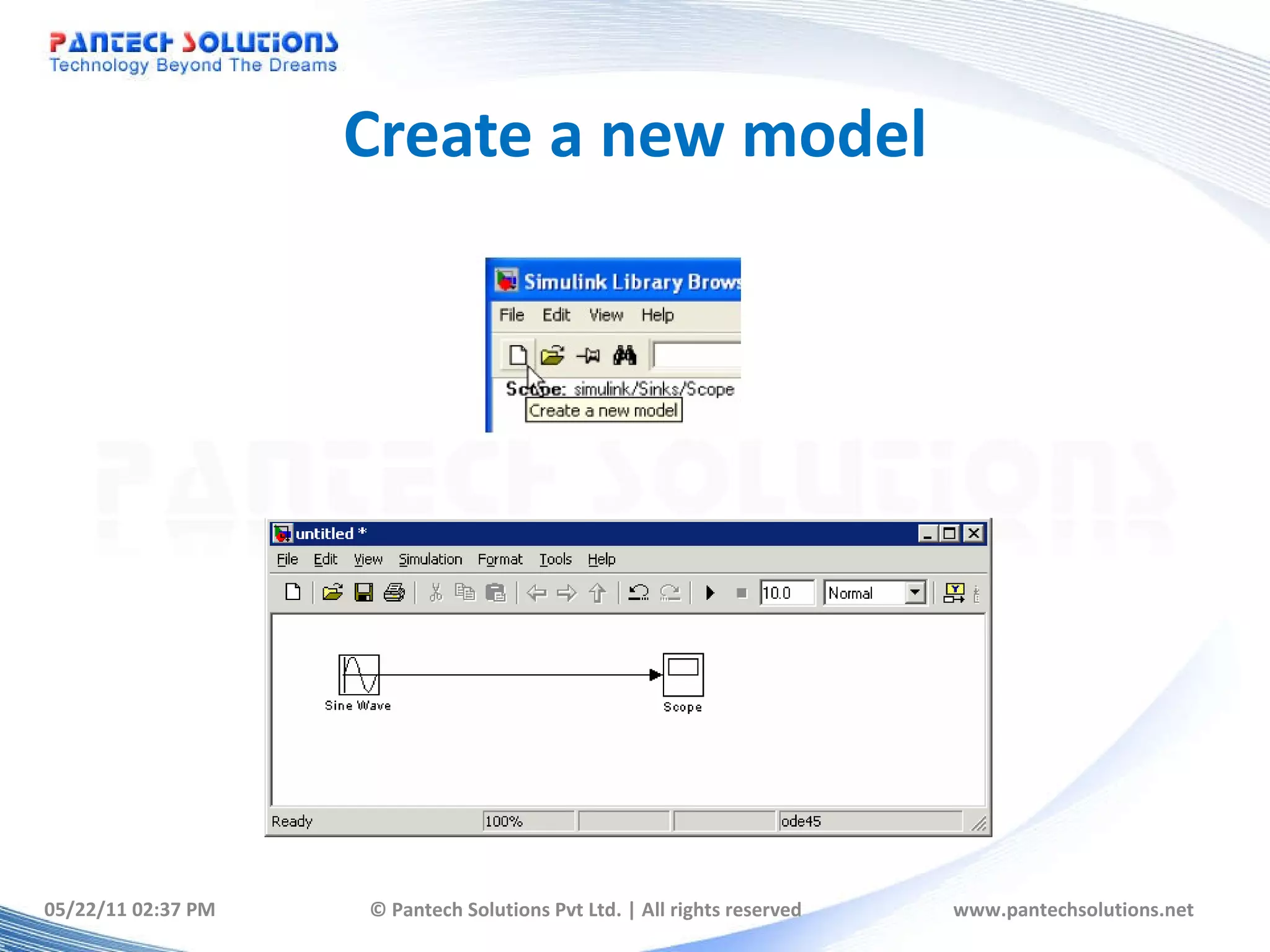

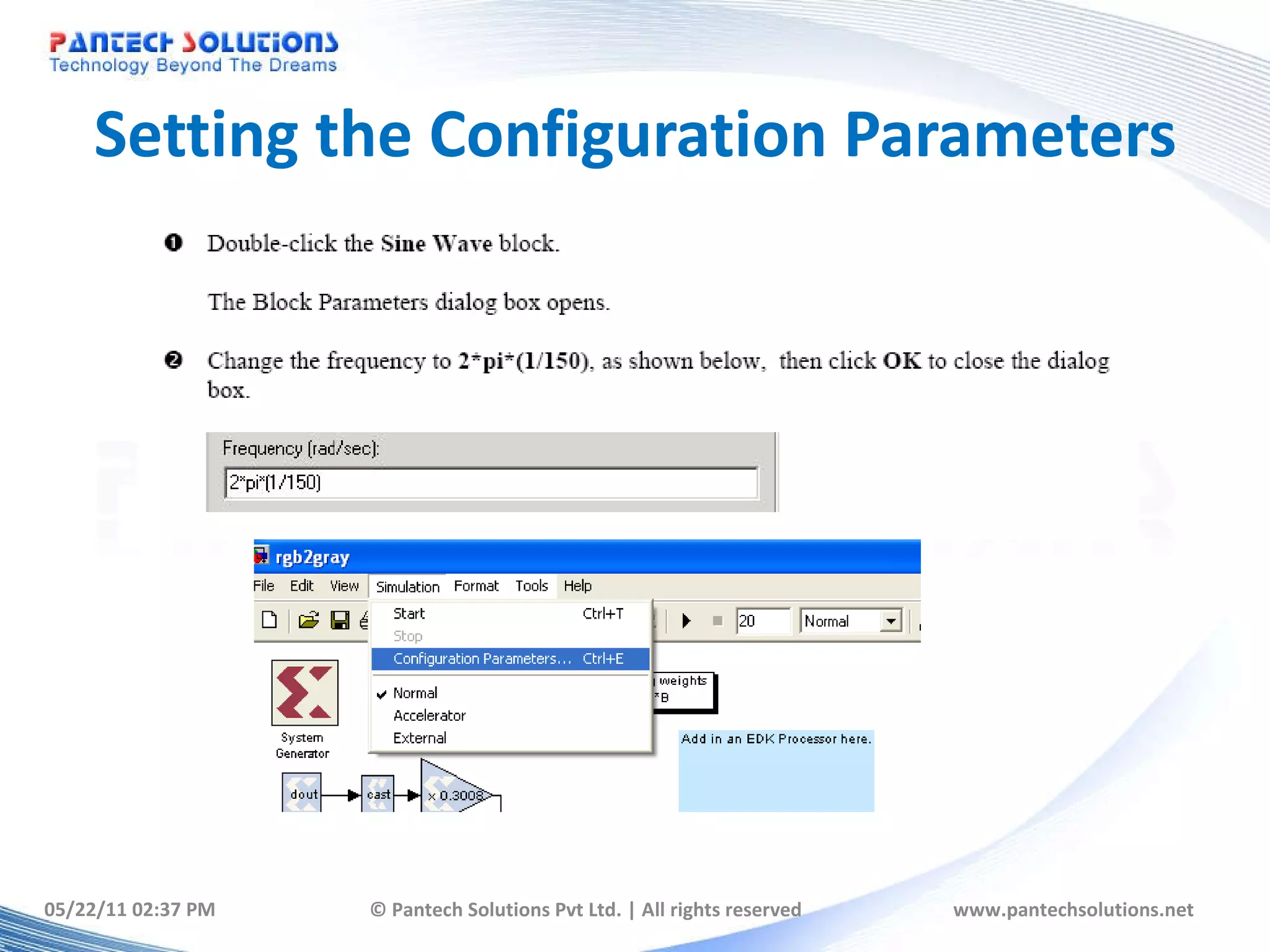

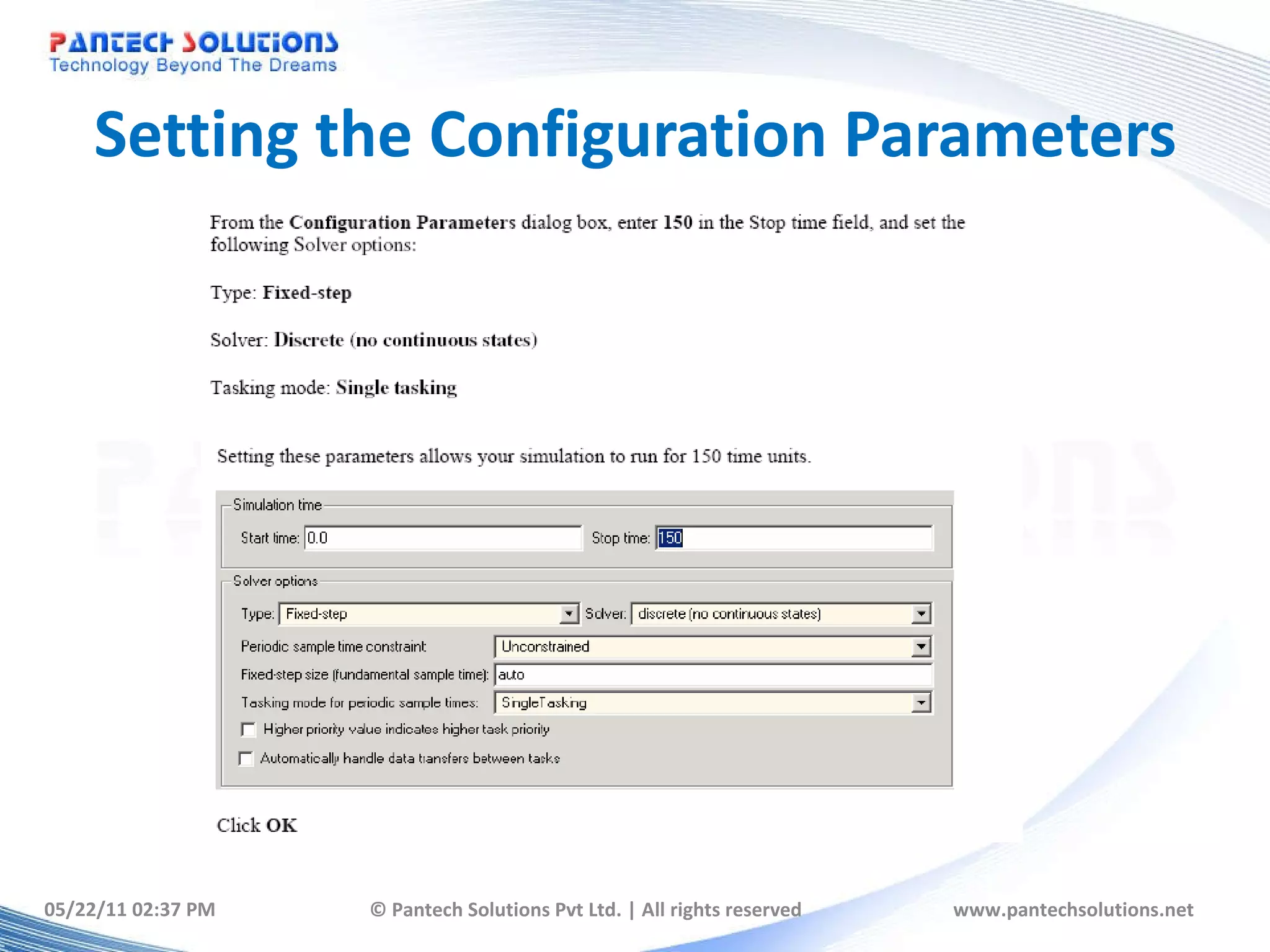

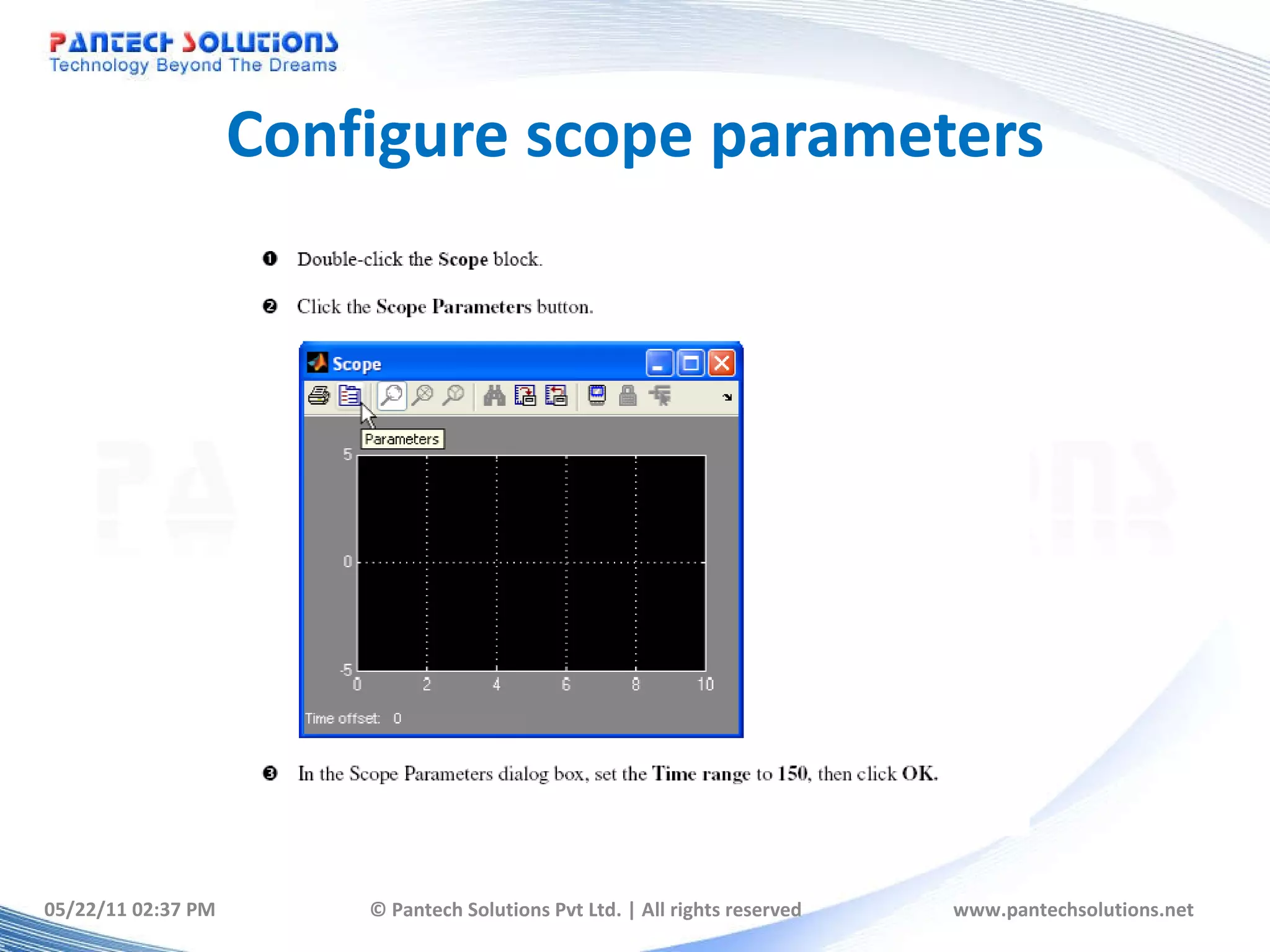

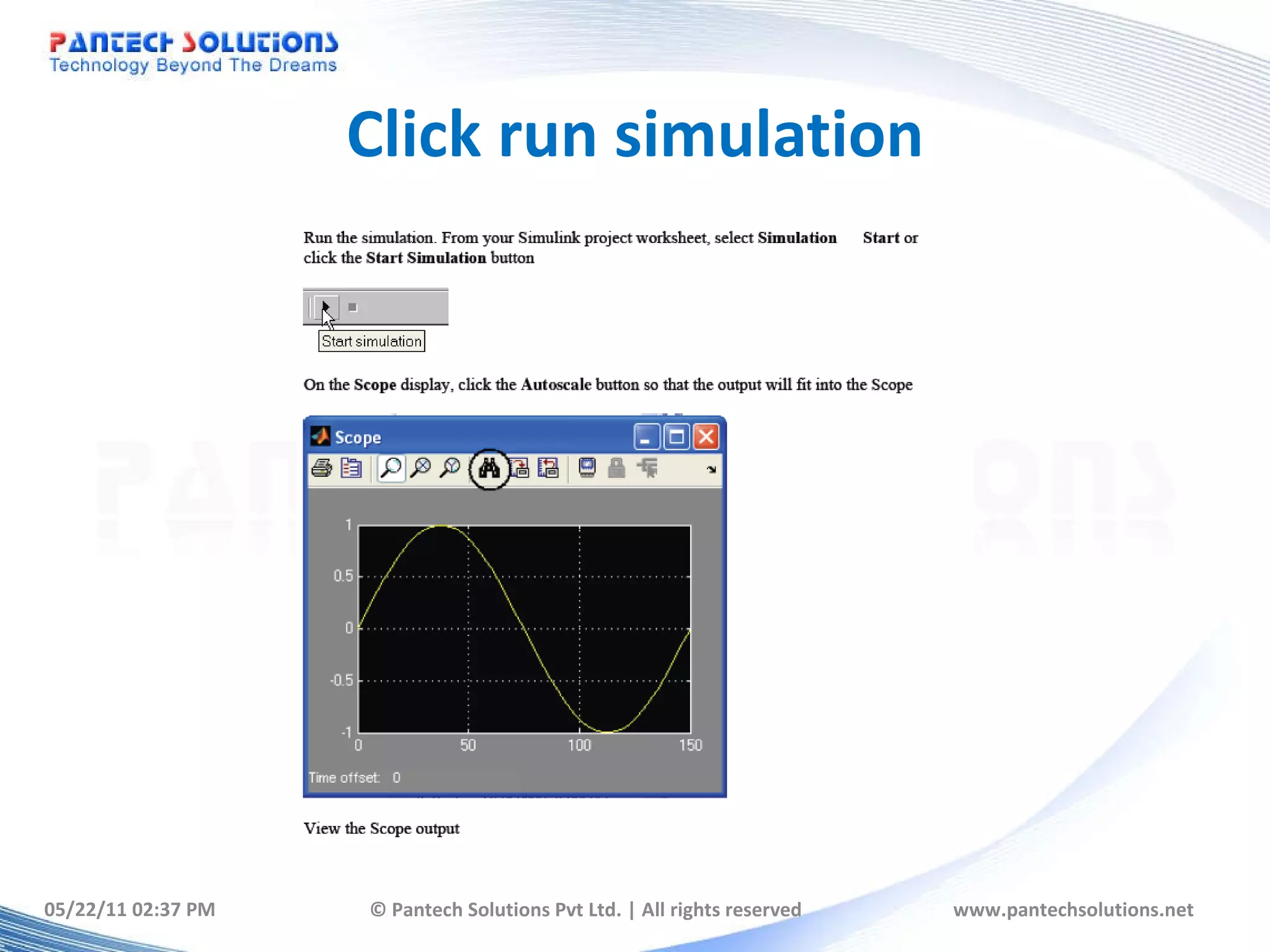

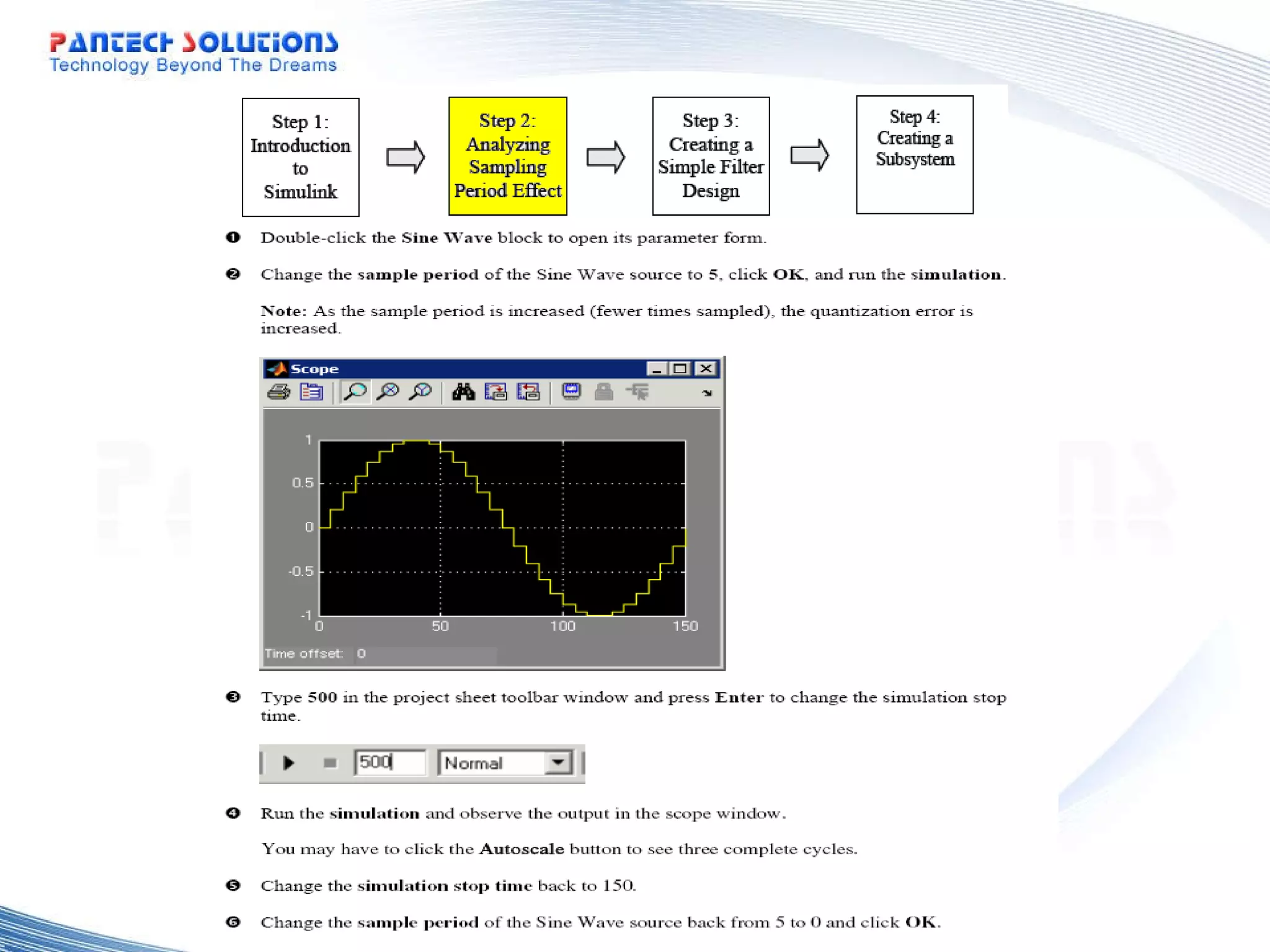

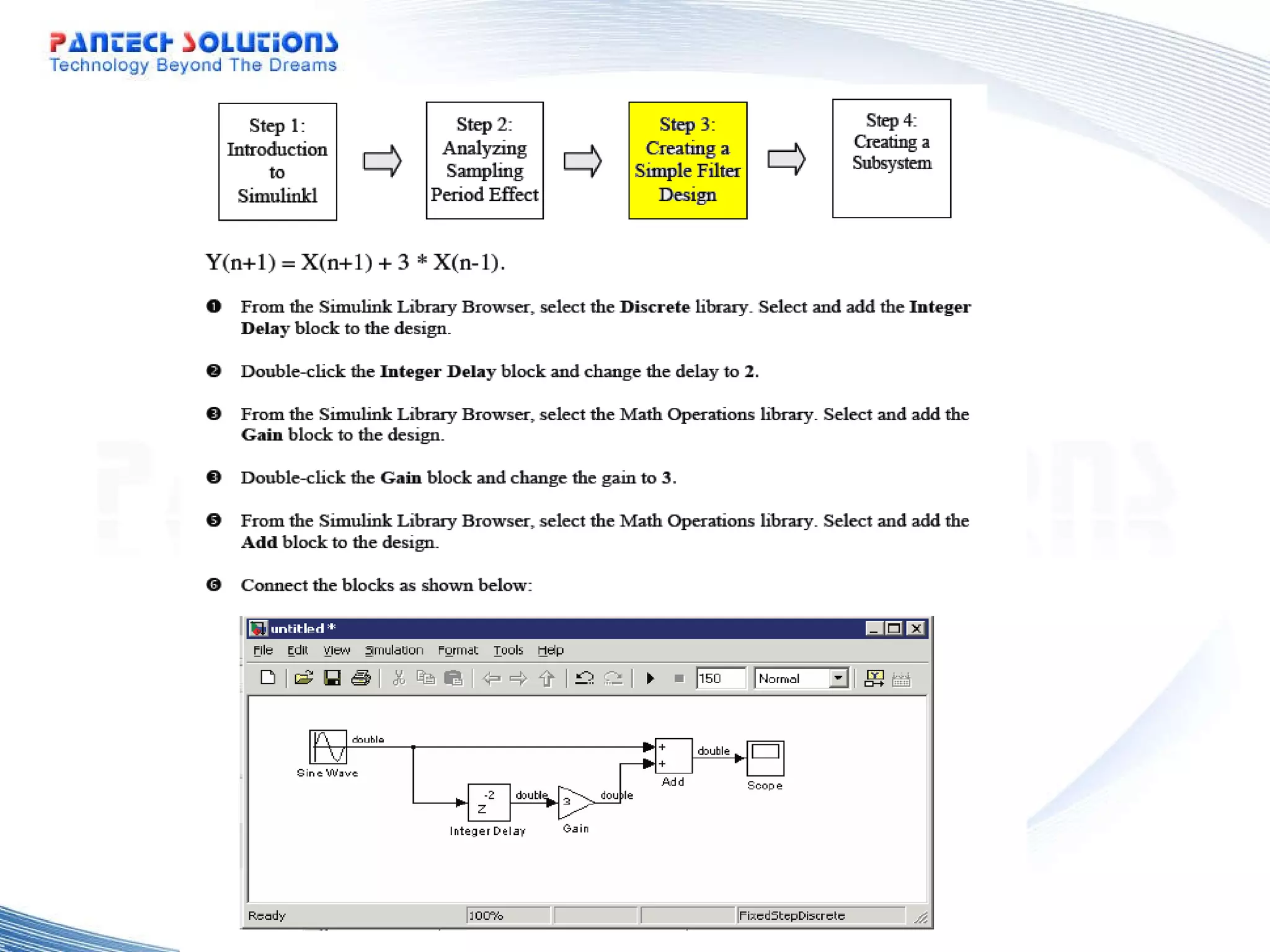

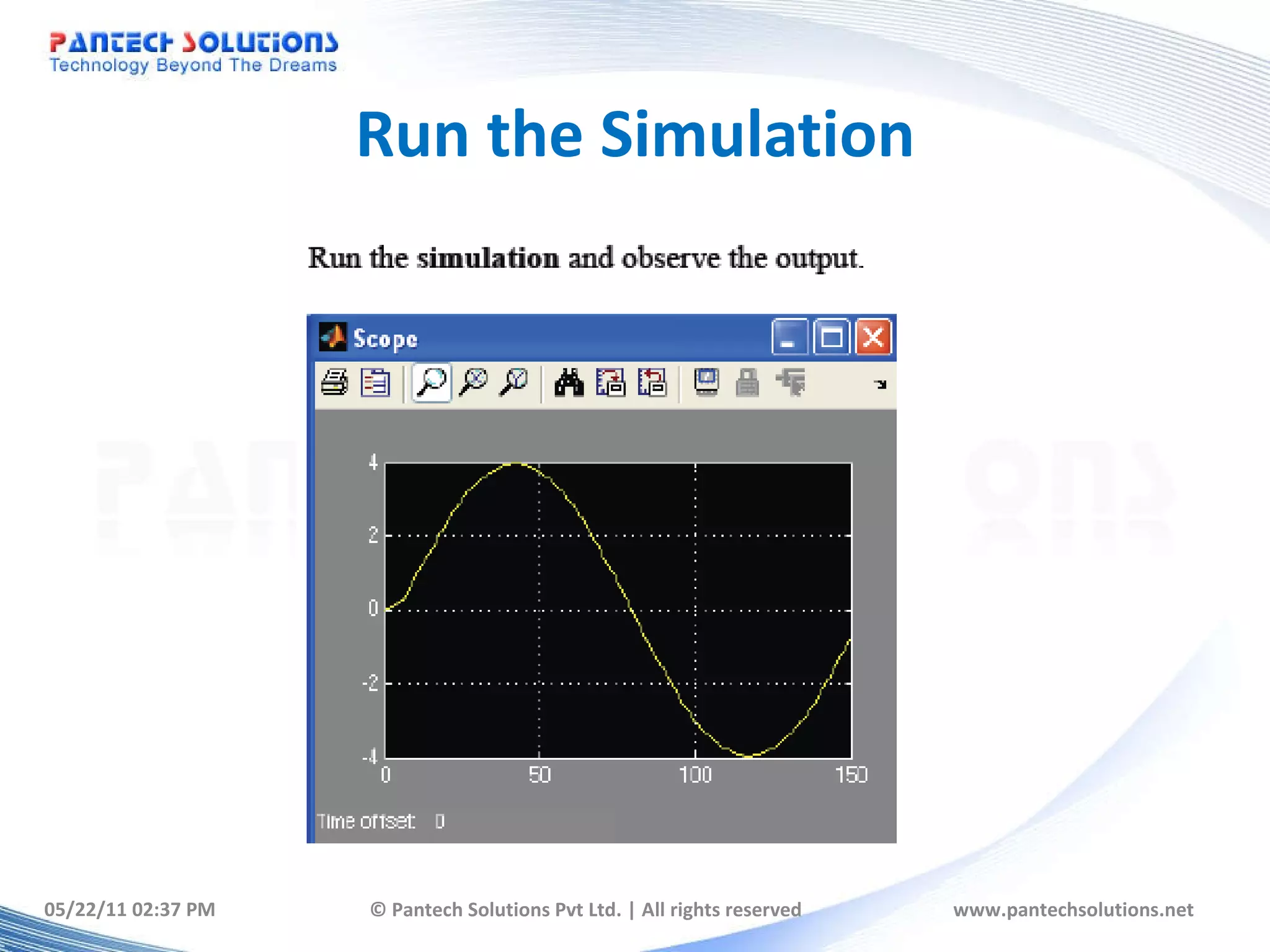

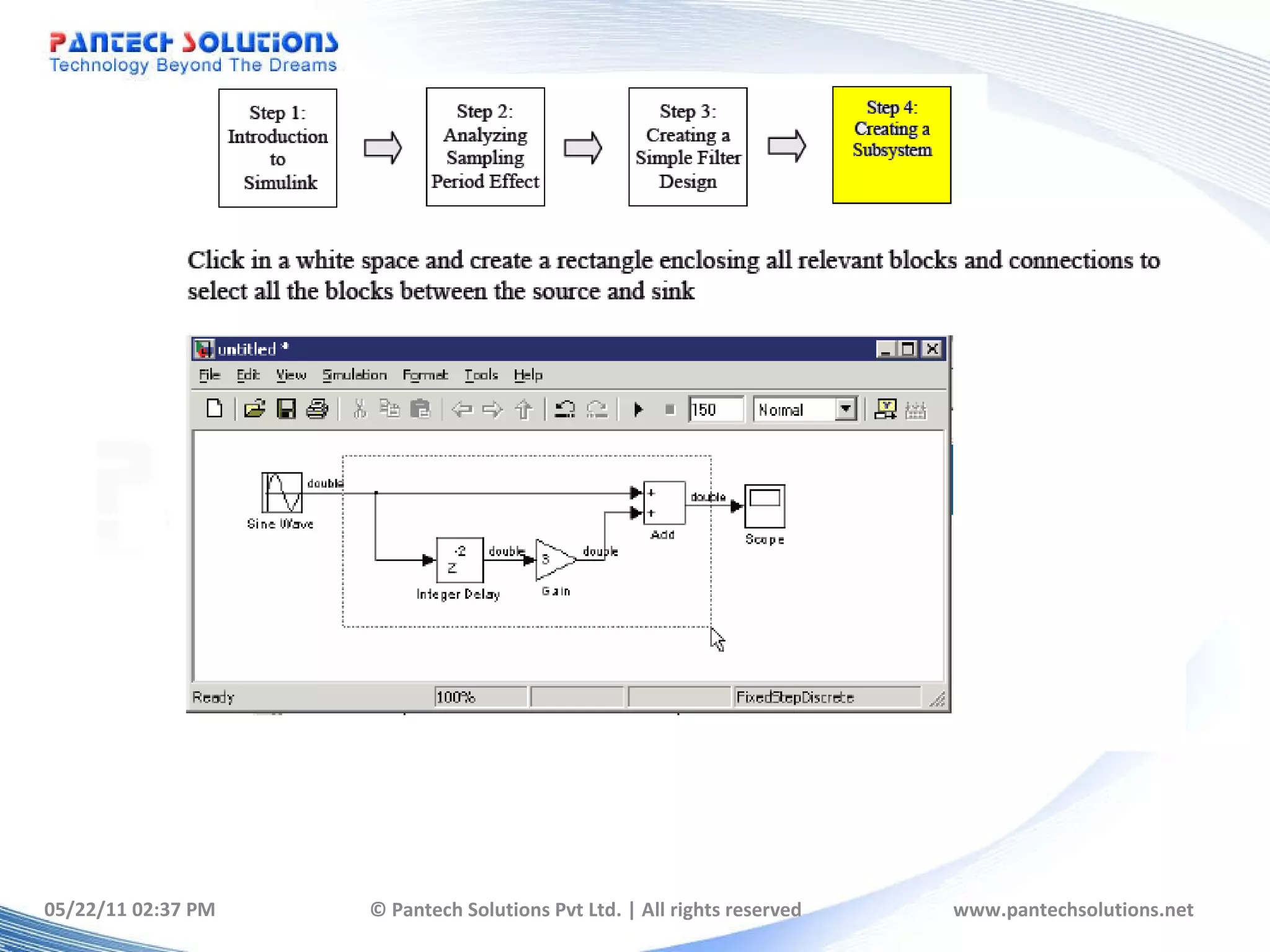

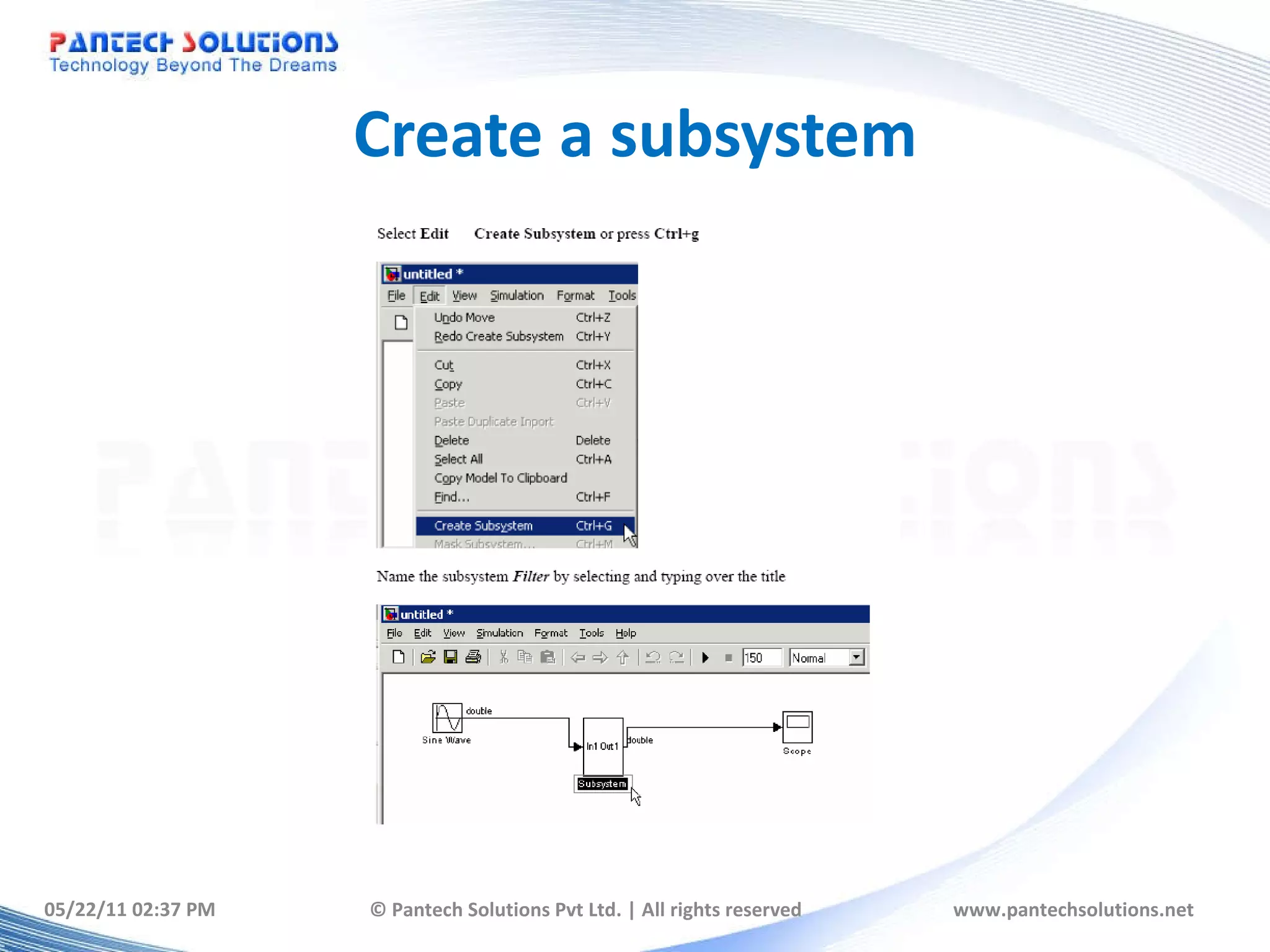

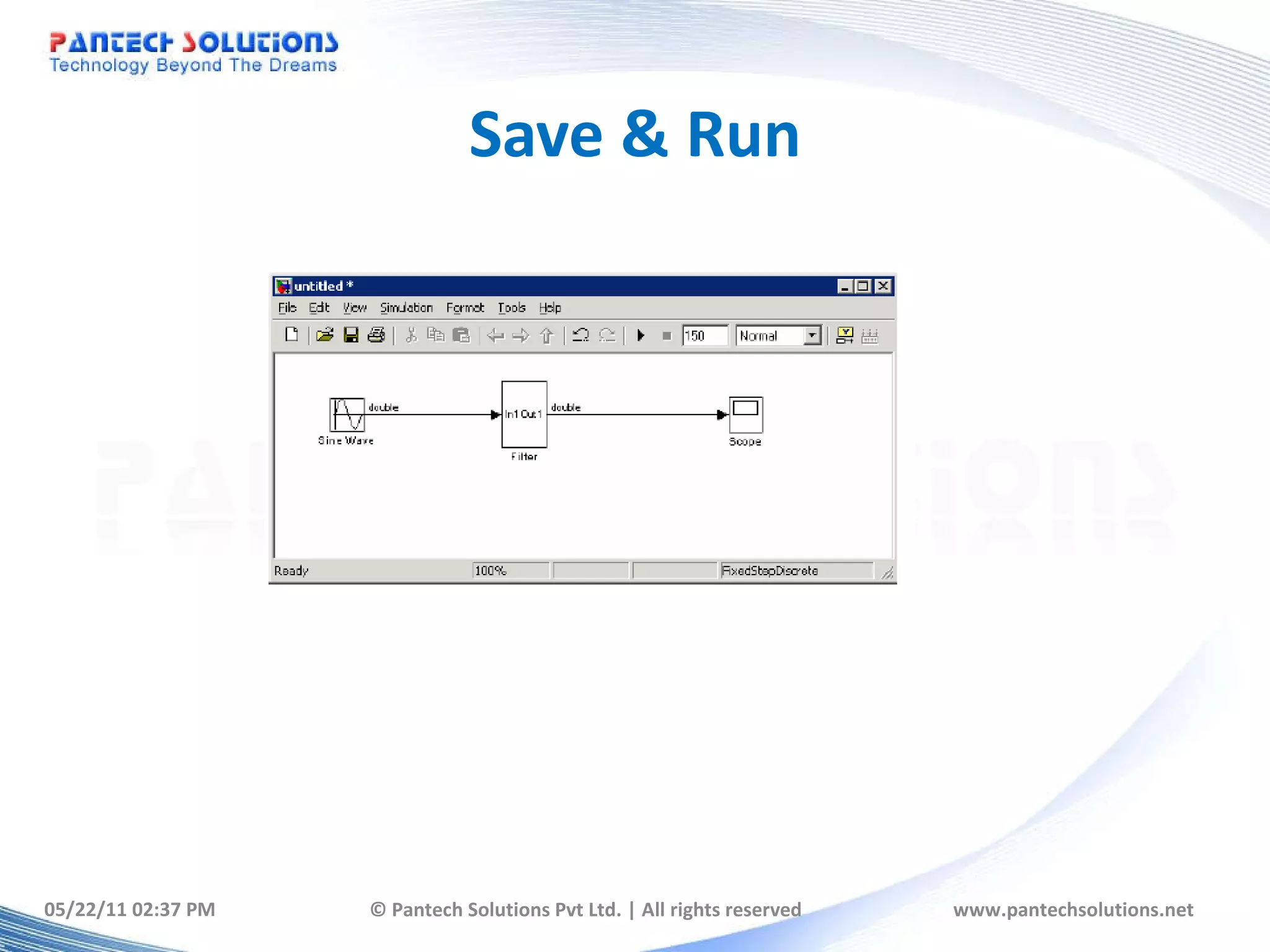

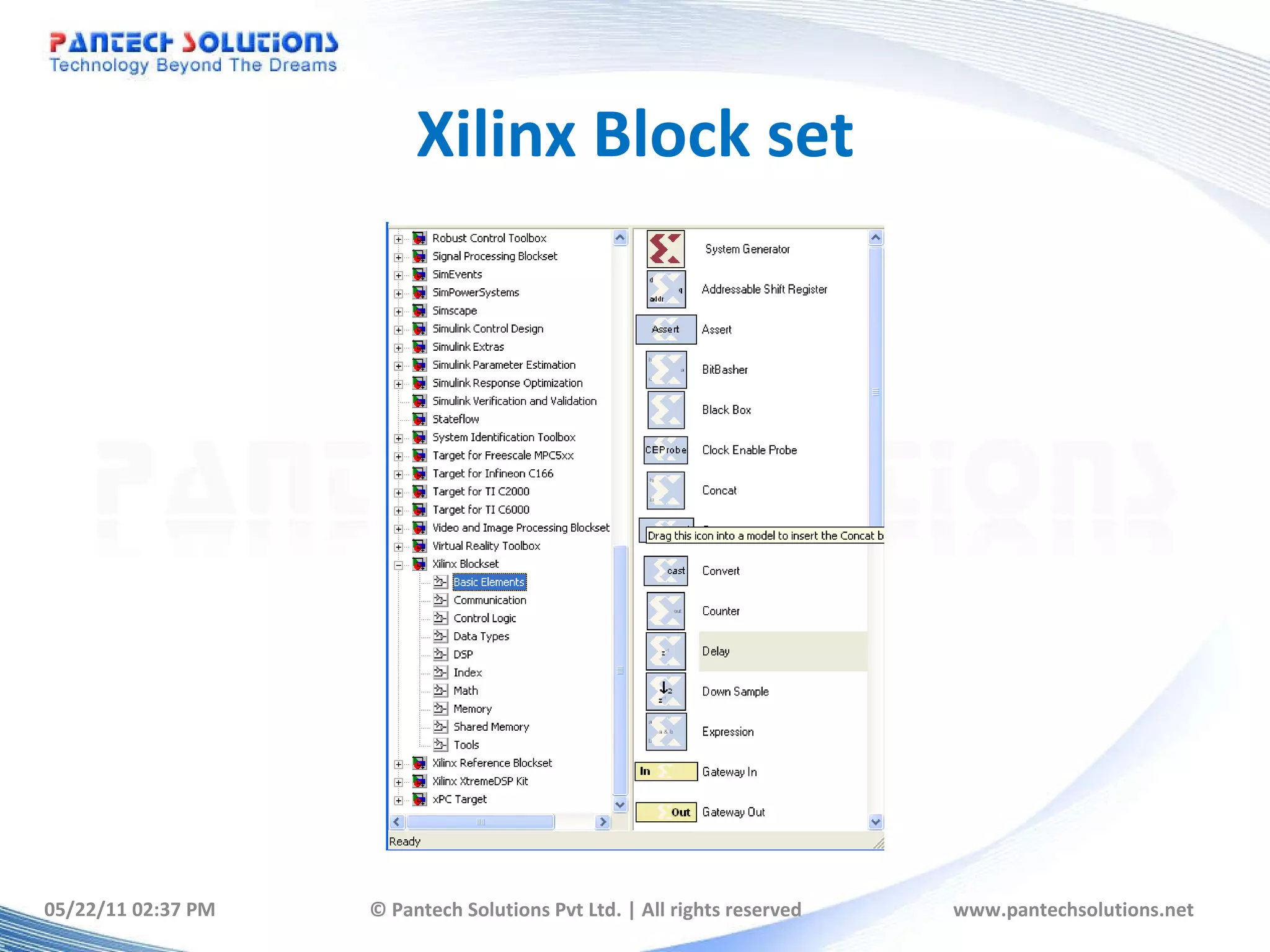

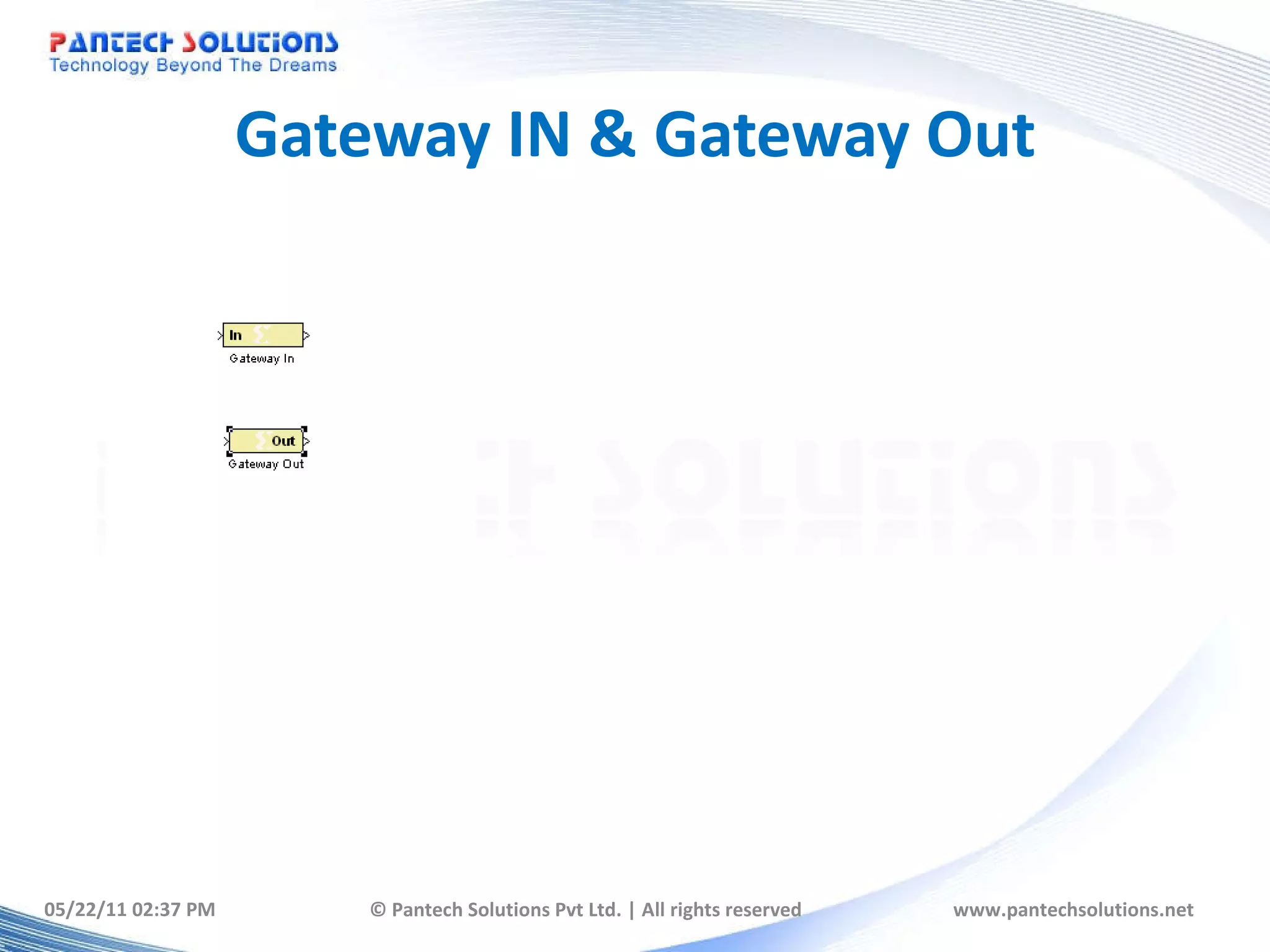

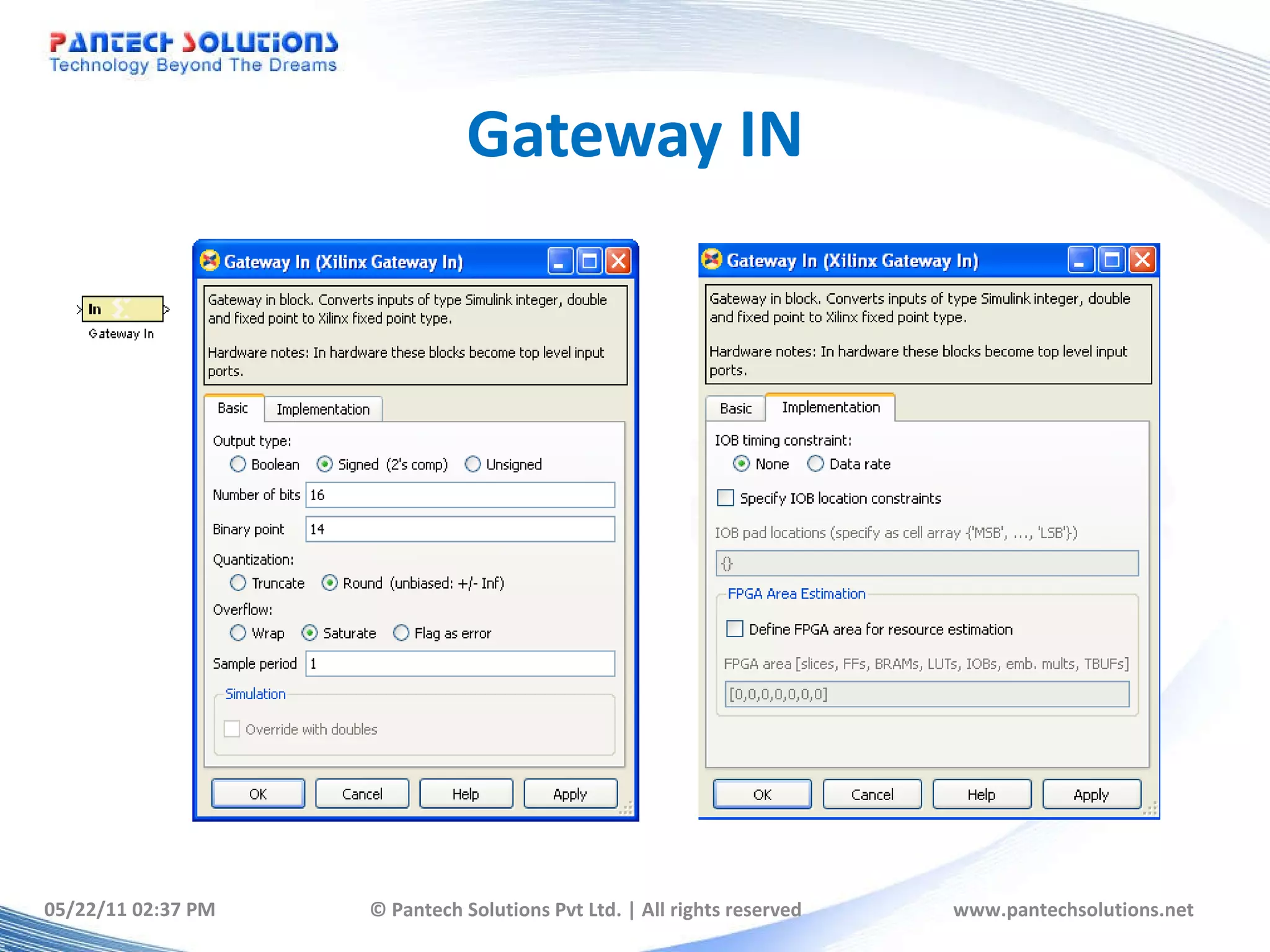

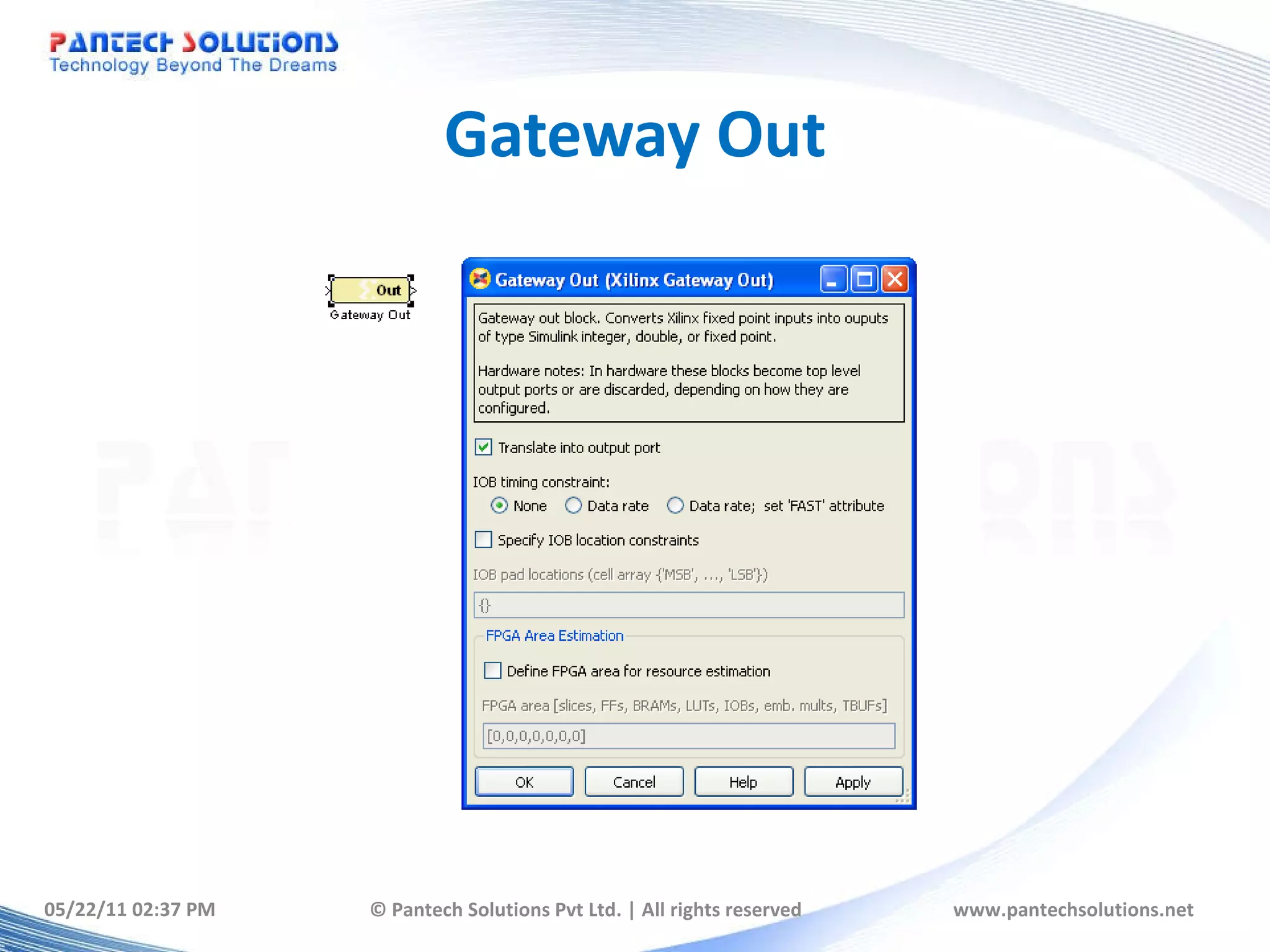

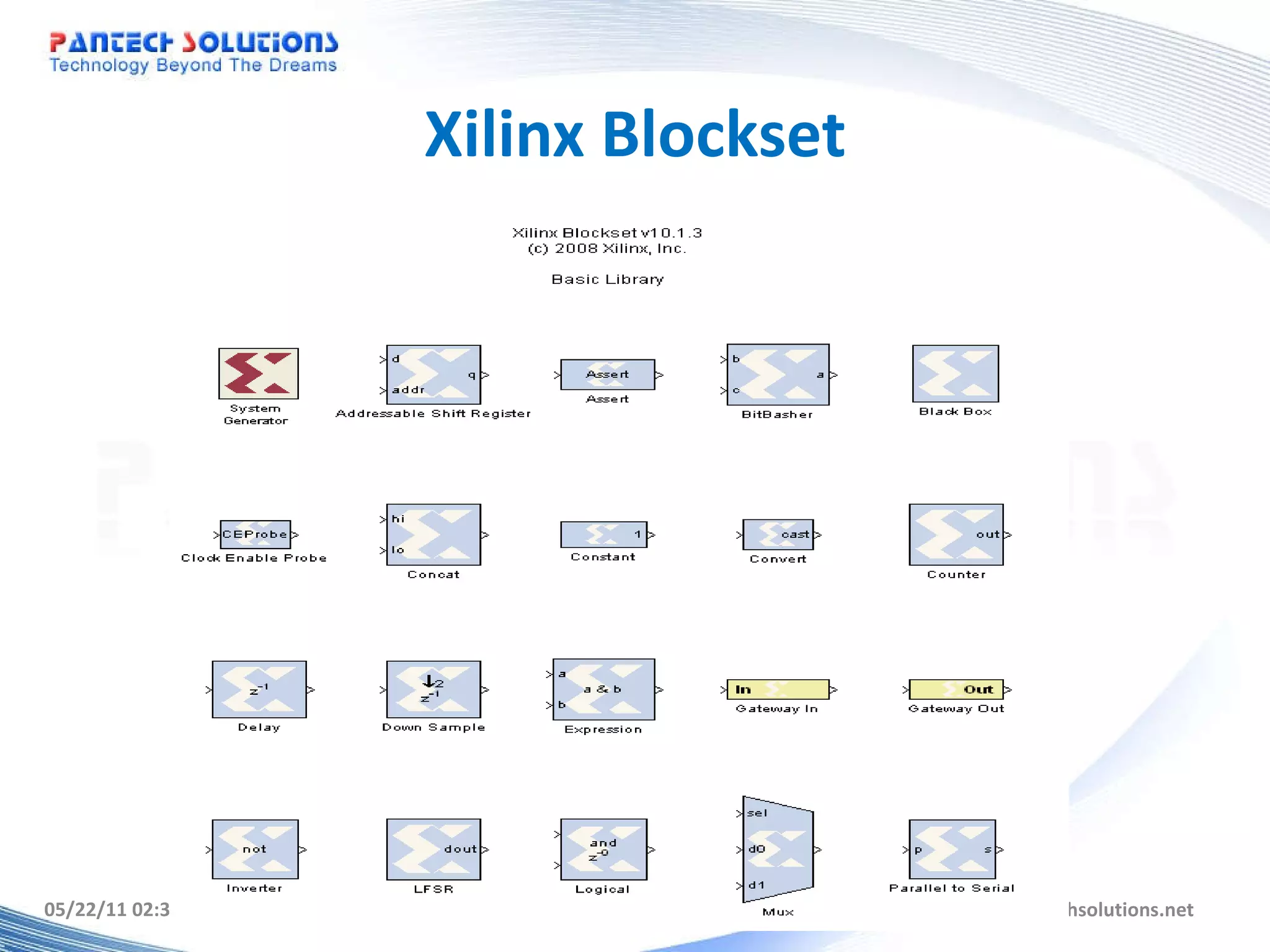

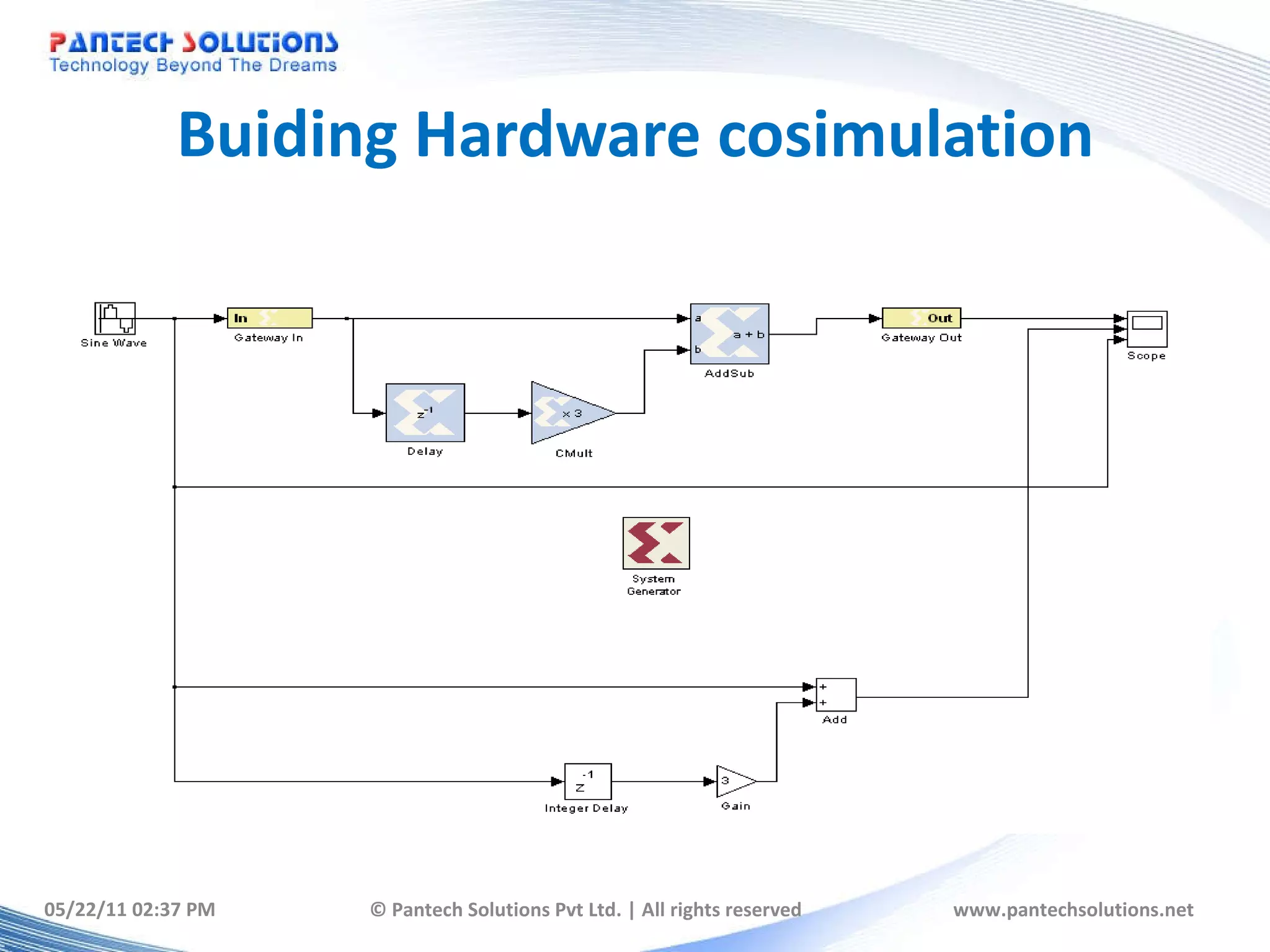

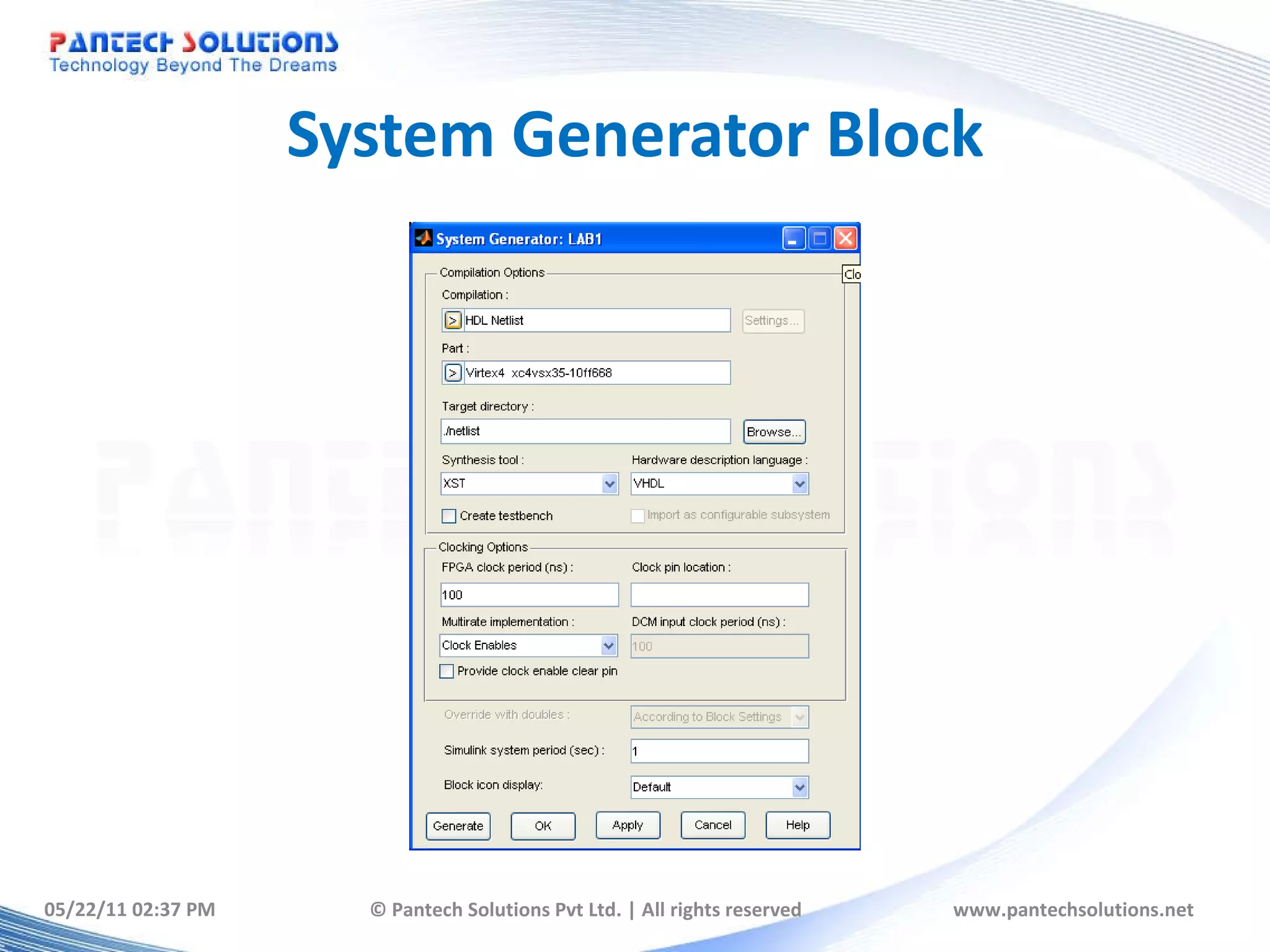

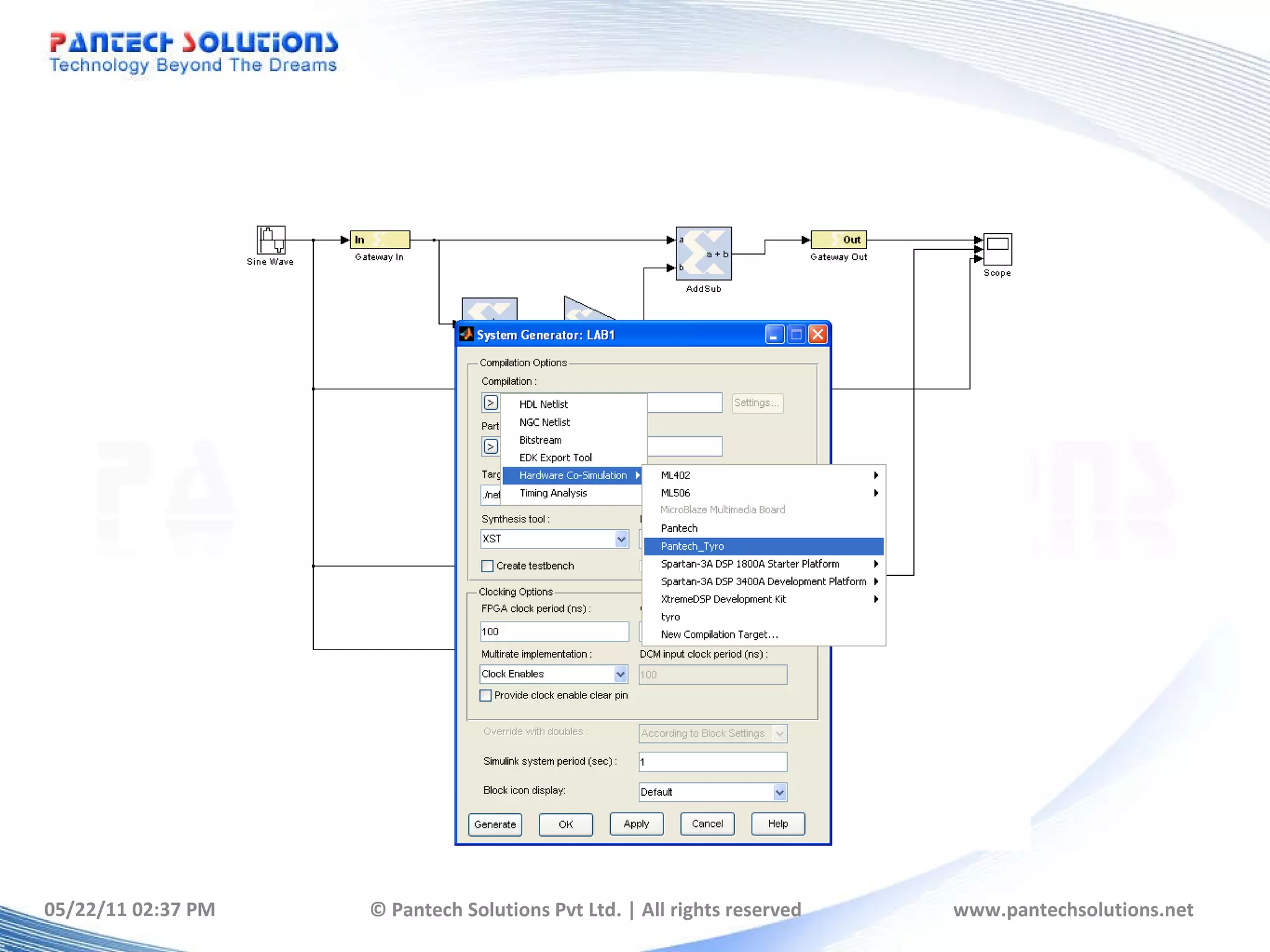

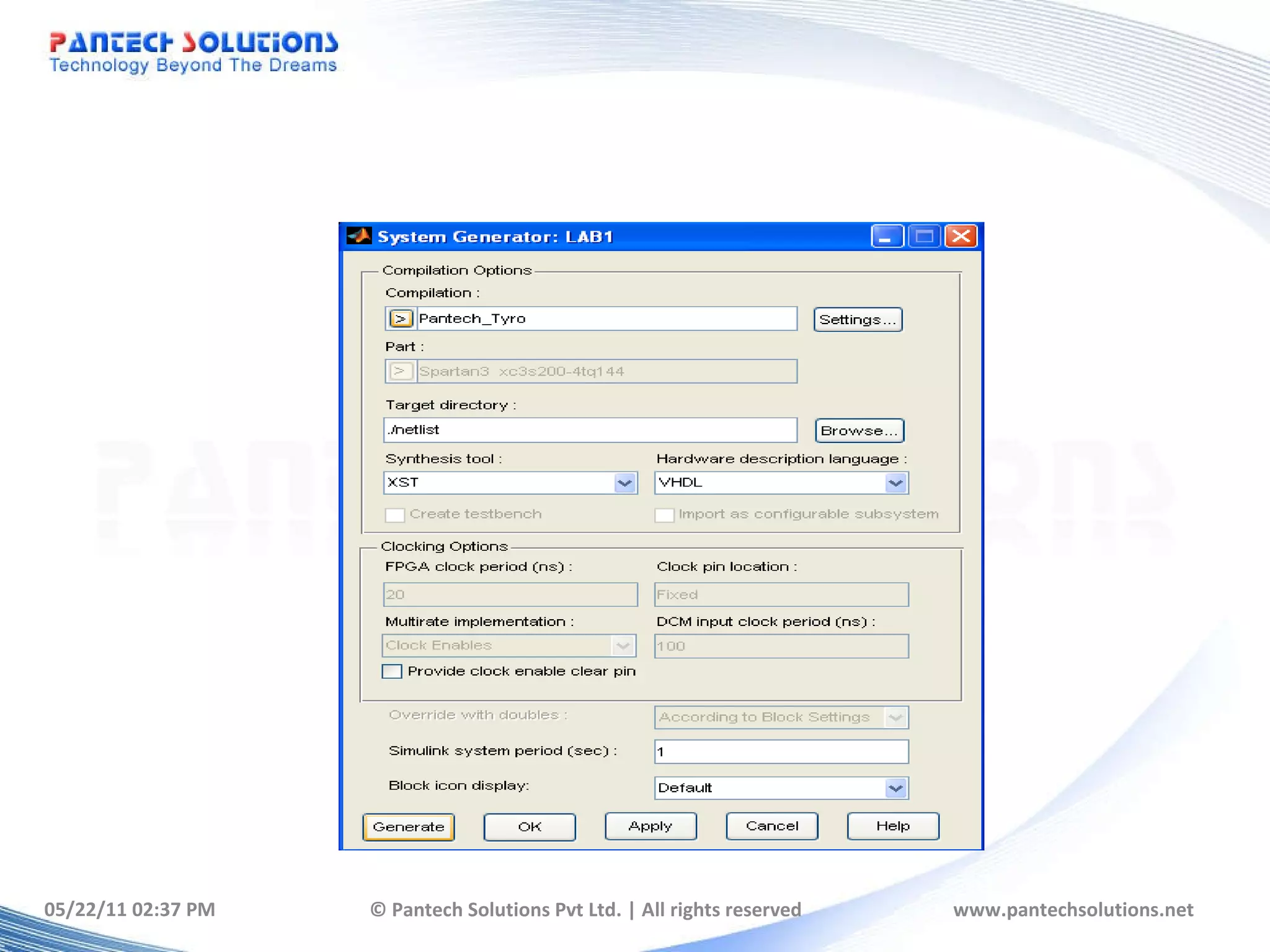

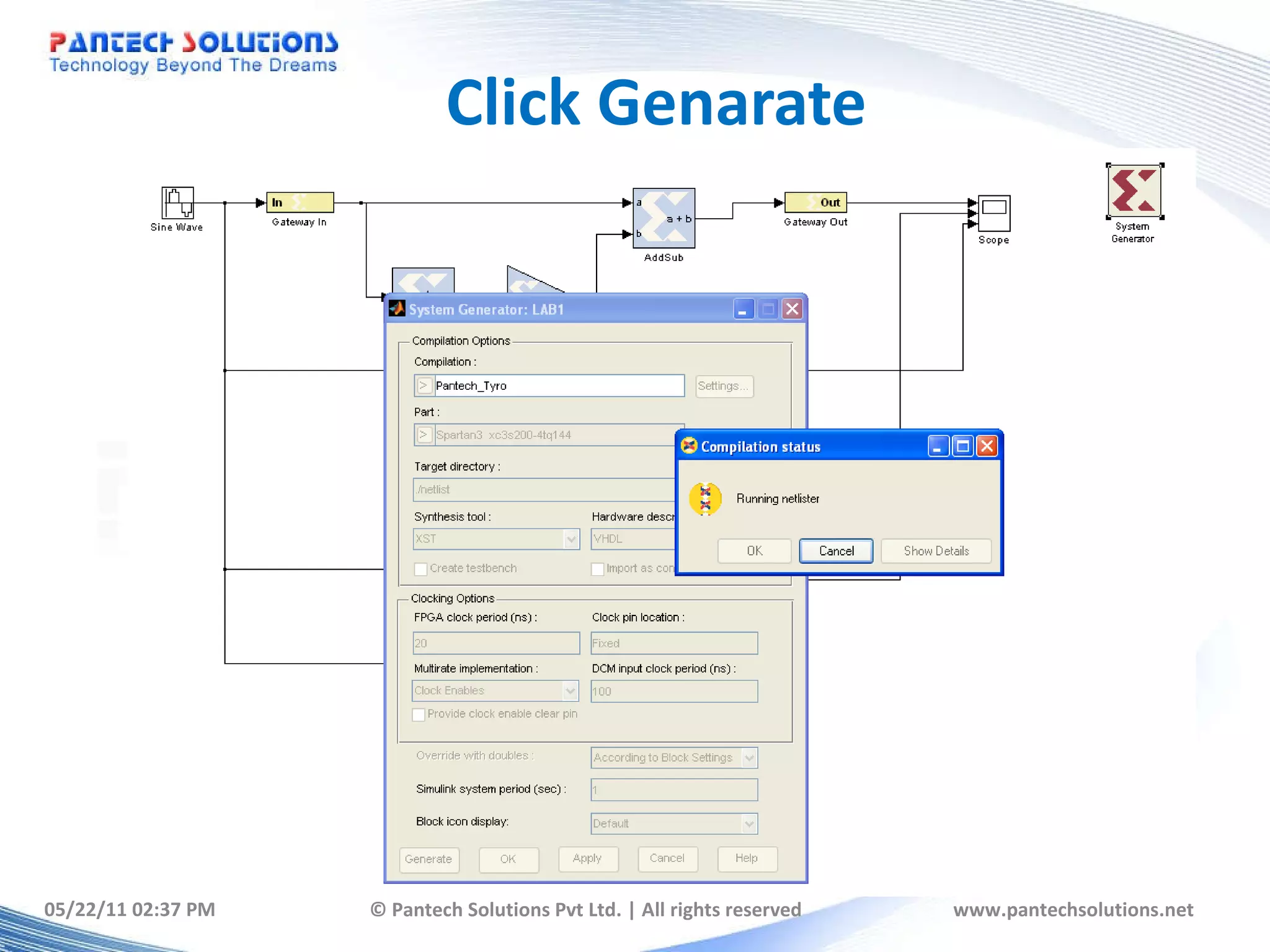

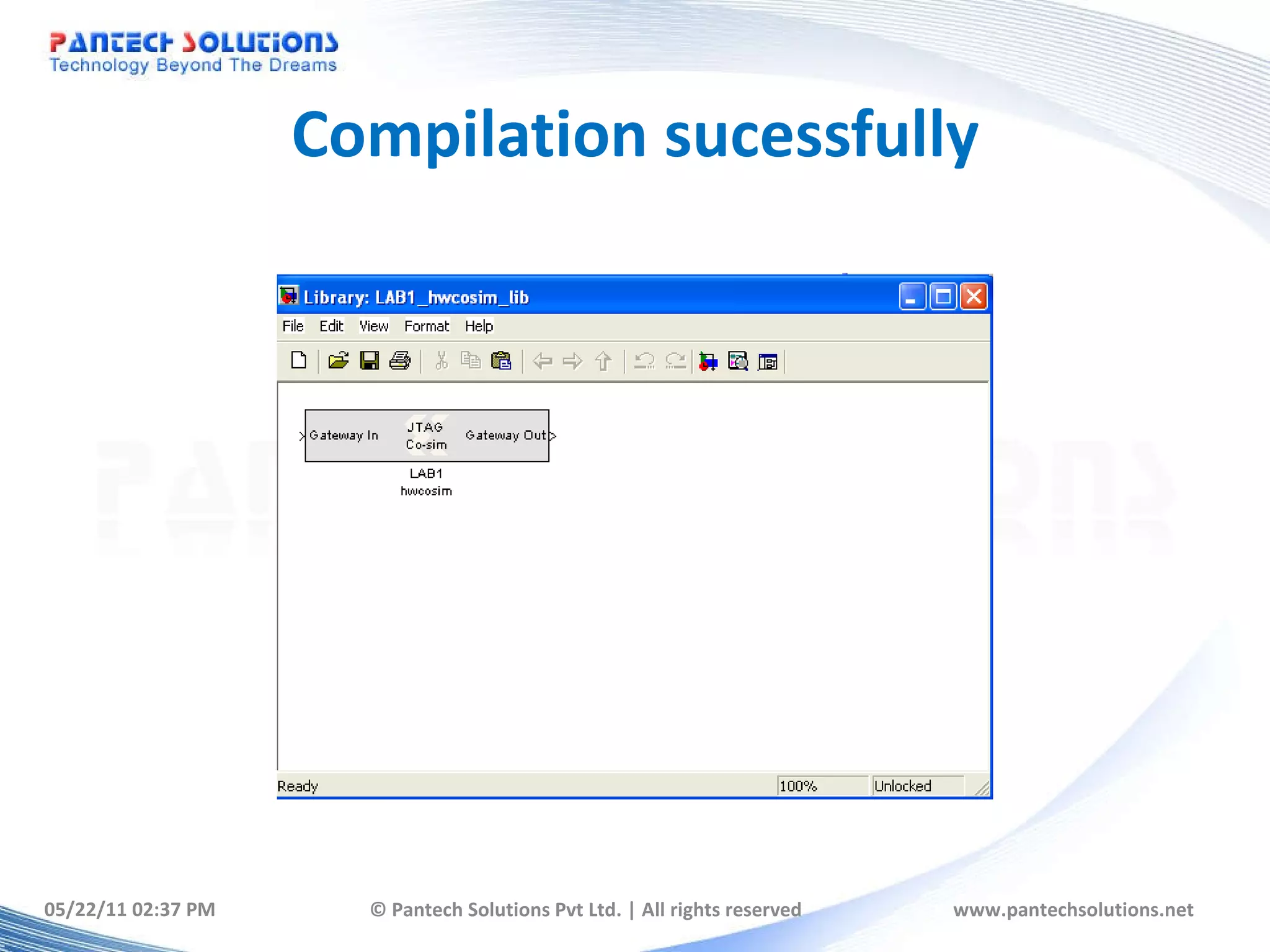

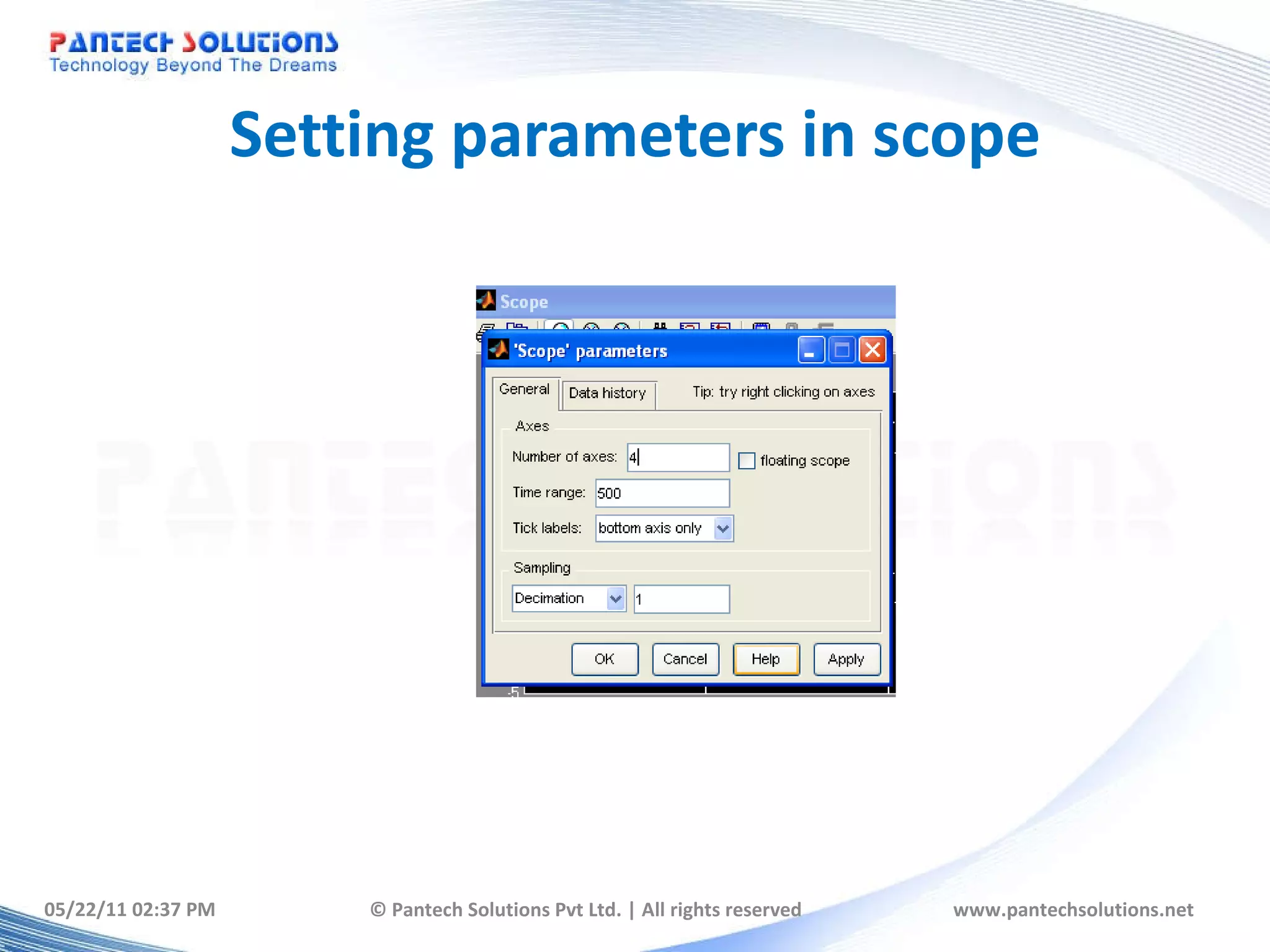

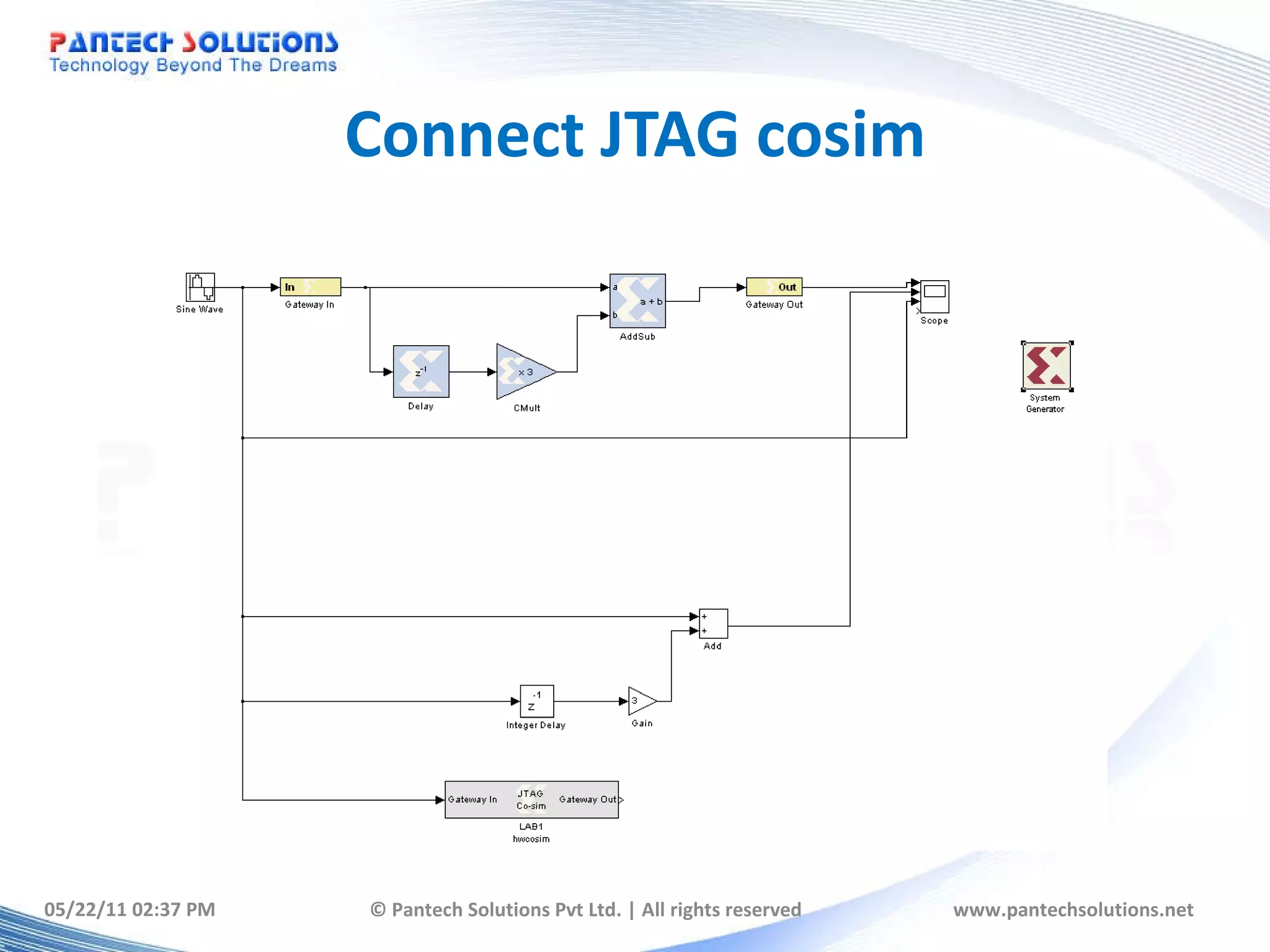

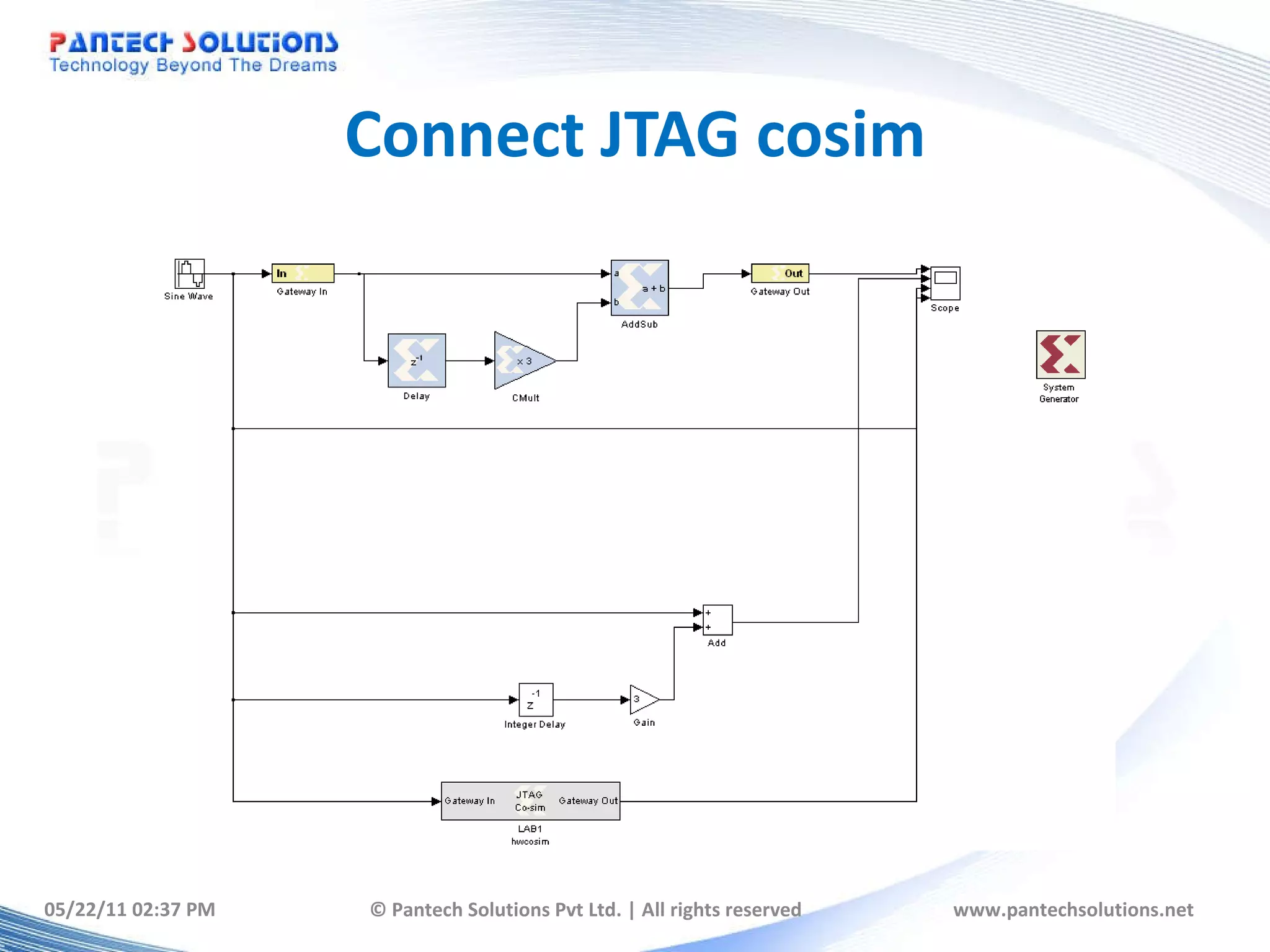

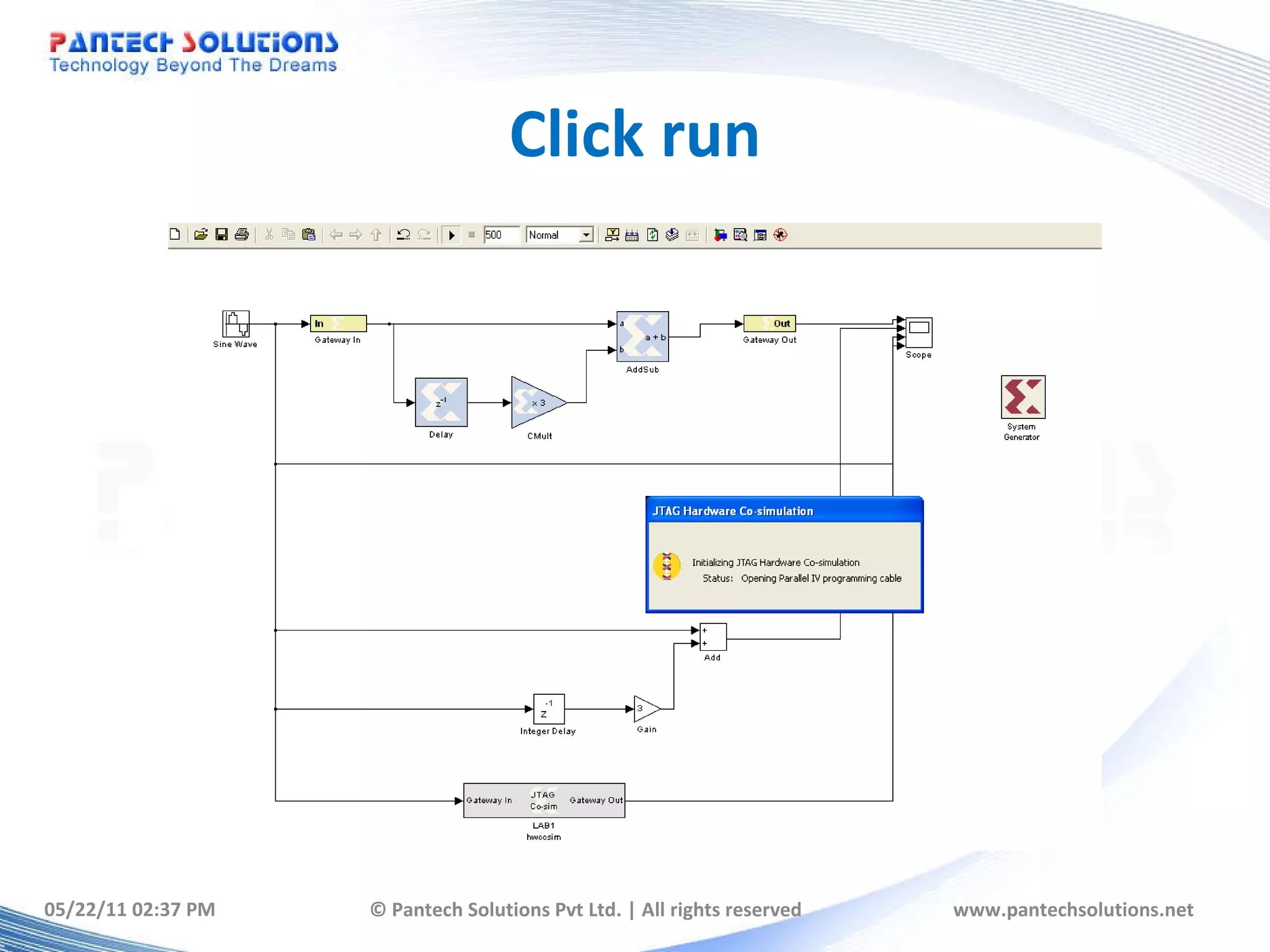

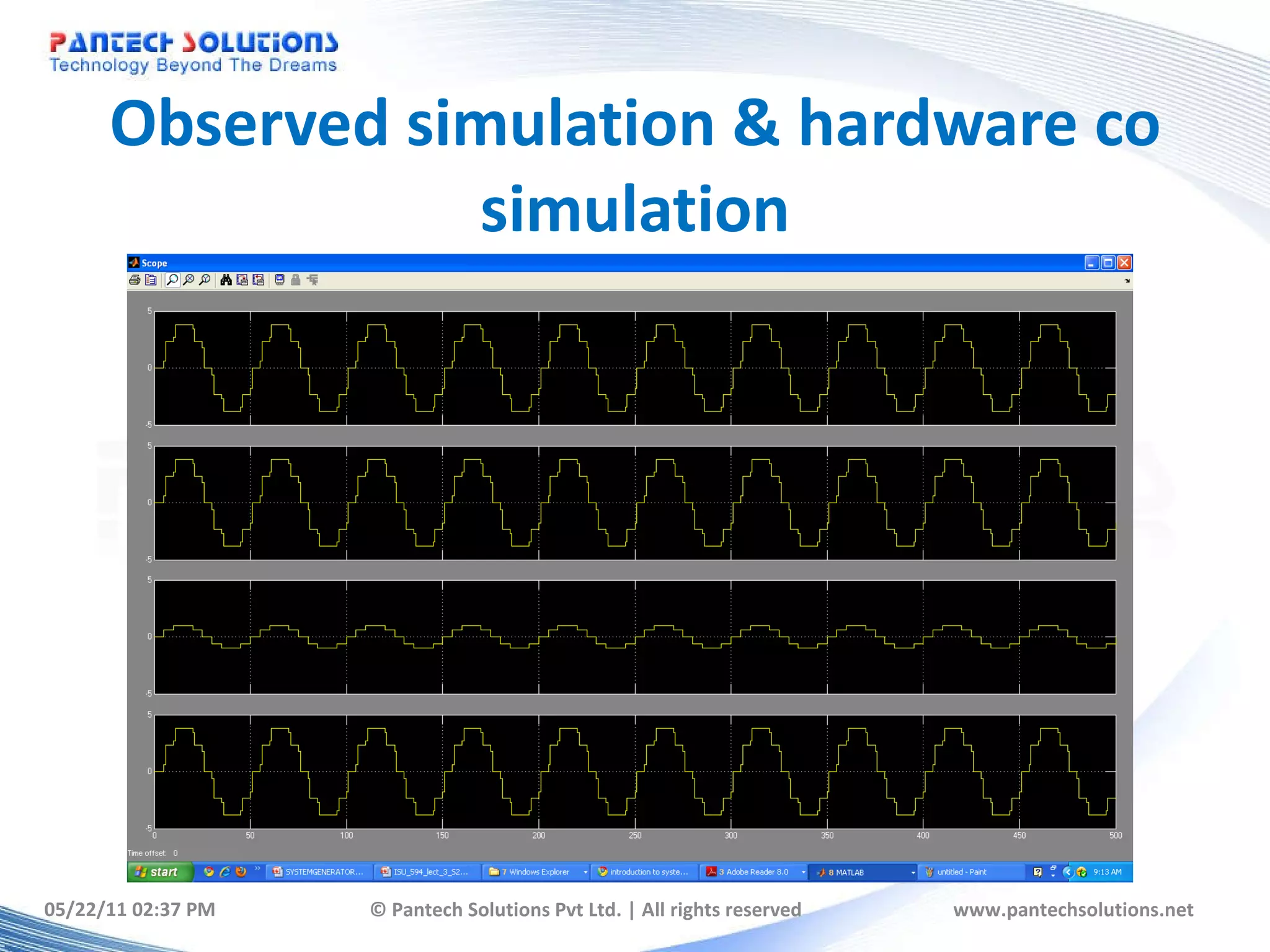

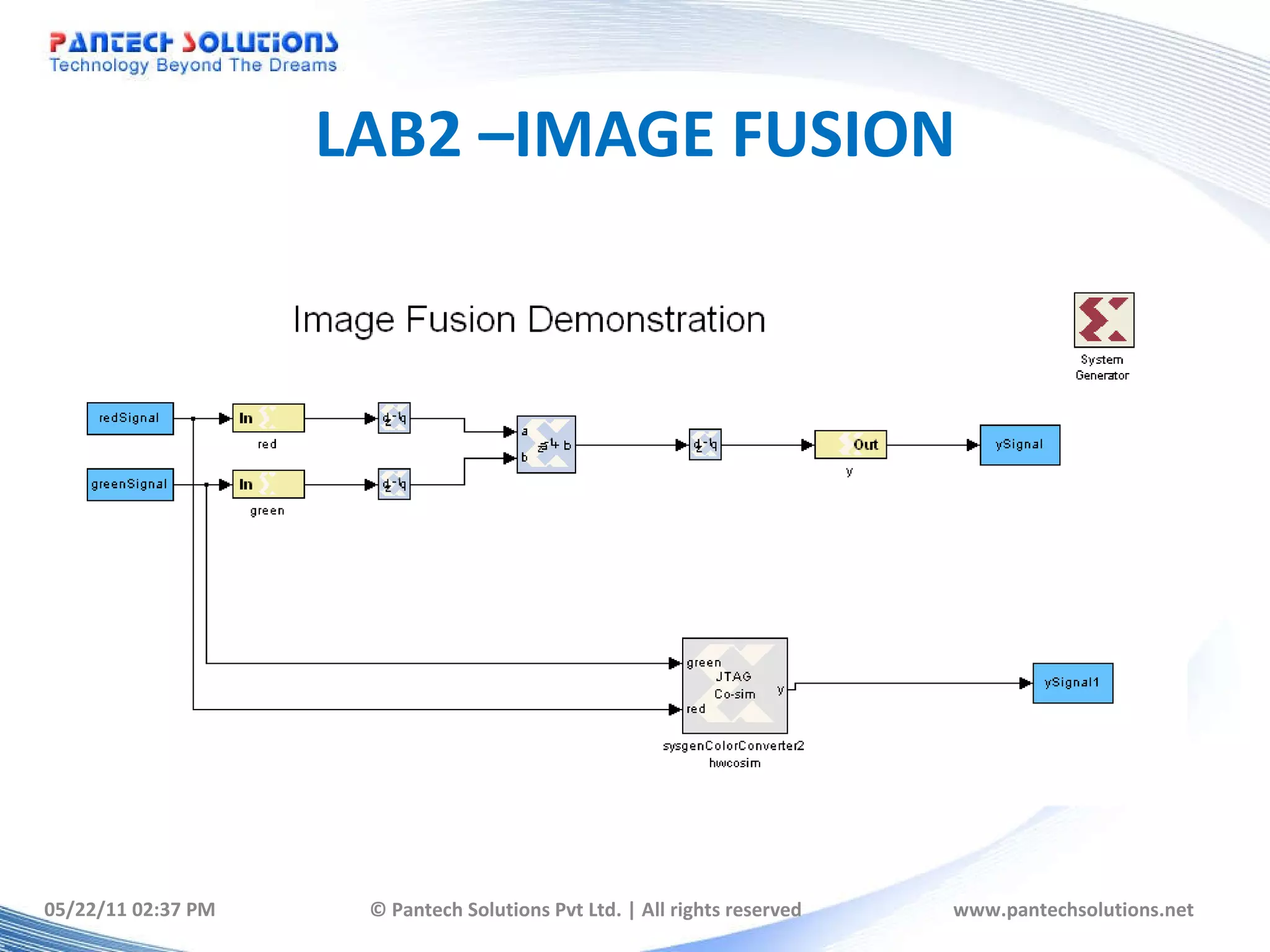

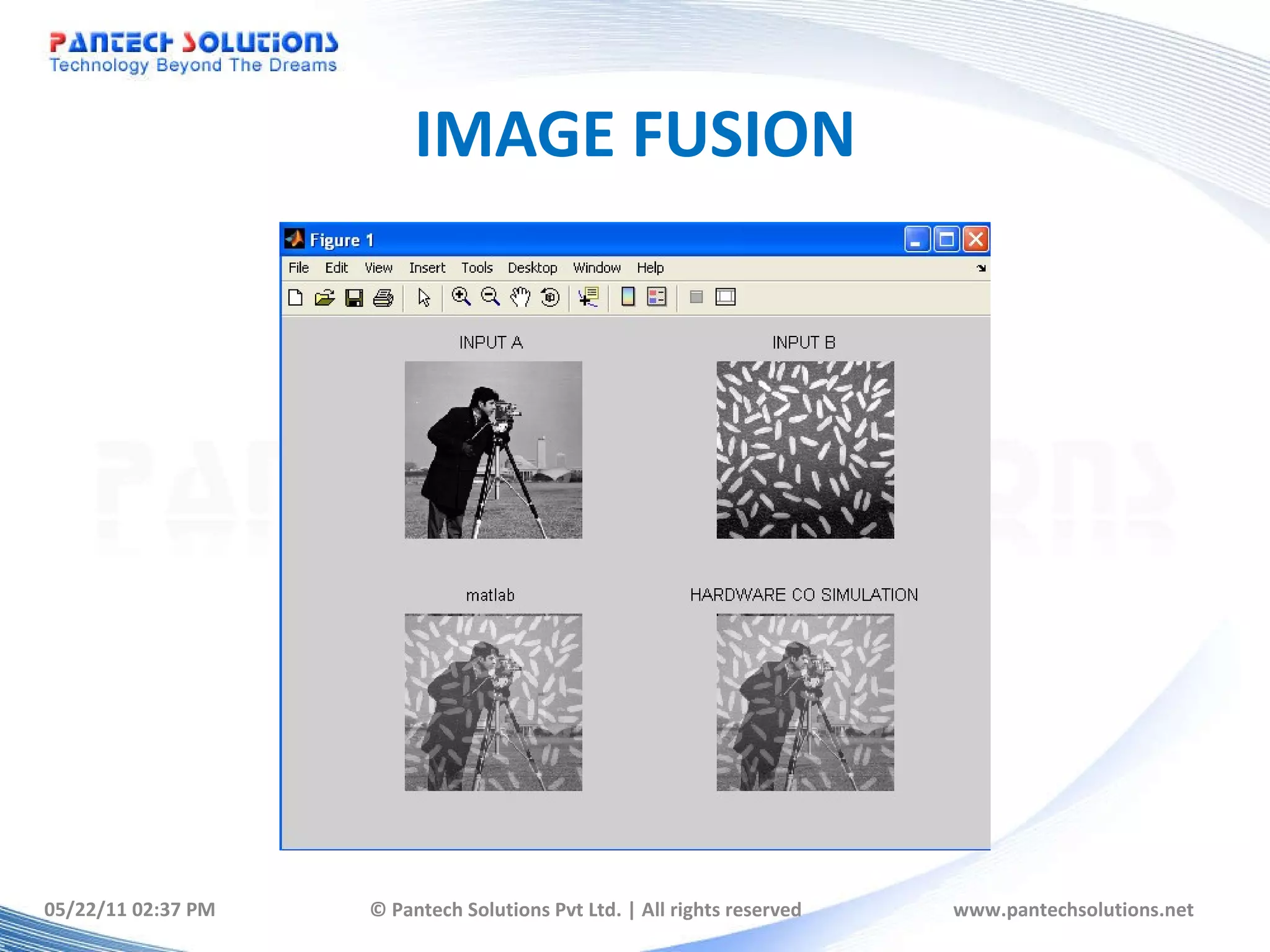

The document discusses steps for system design using Xilinx System Generator including: creating sources and sinks, setting configuration parameters, running simulation, creating and saving subsystems, using Xilinx blocks for gateway in/out, building hardware cosimulation with System Generator blocks, generating and compiling the design, setting scope parameters, connecting JTAG cosimulation, and observing simulation and hardware cosimulation results. It also mentions a lab on image fusion.