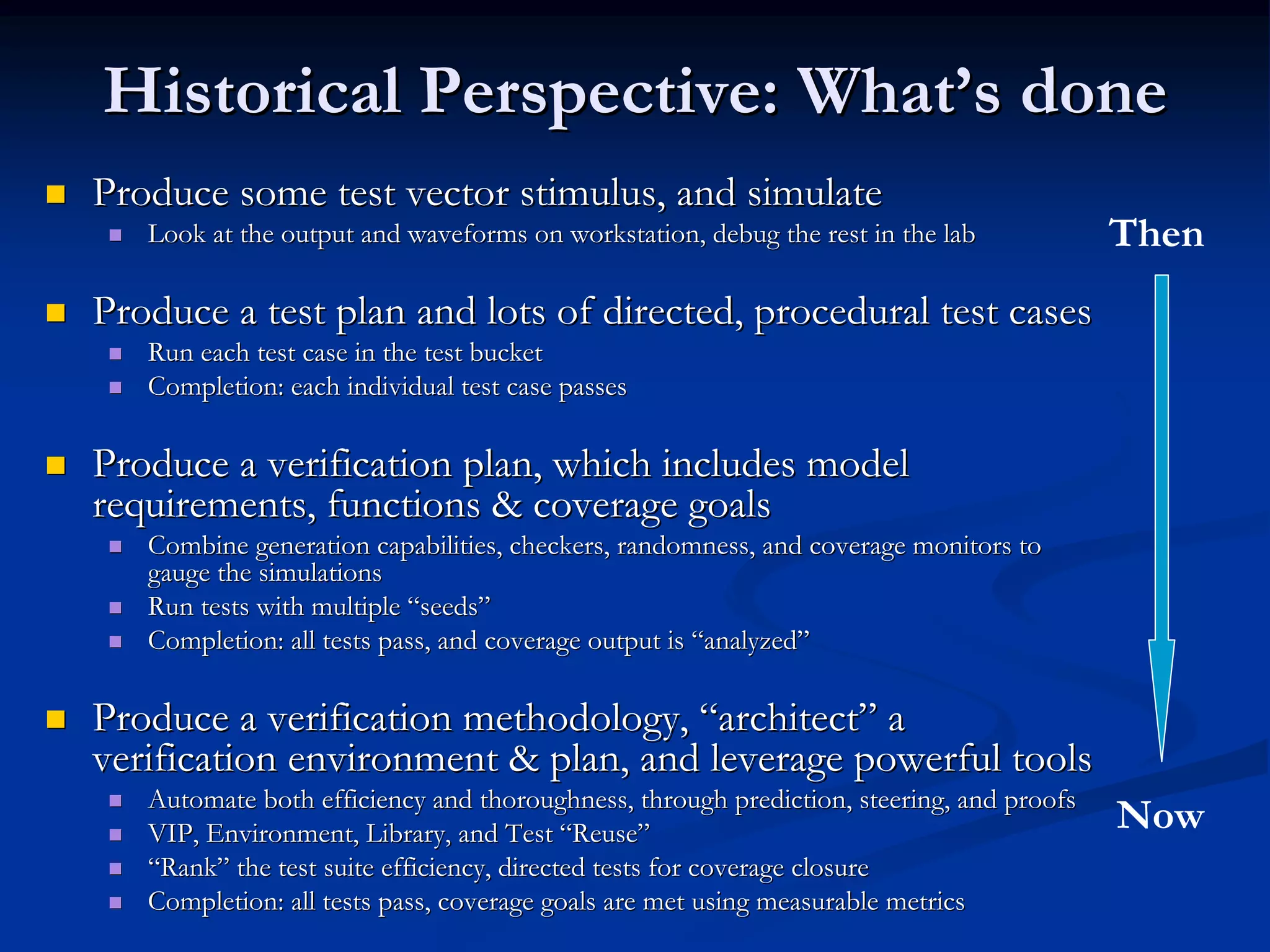

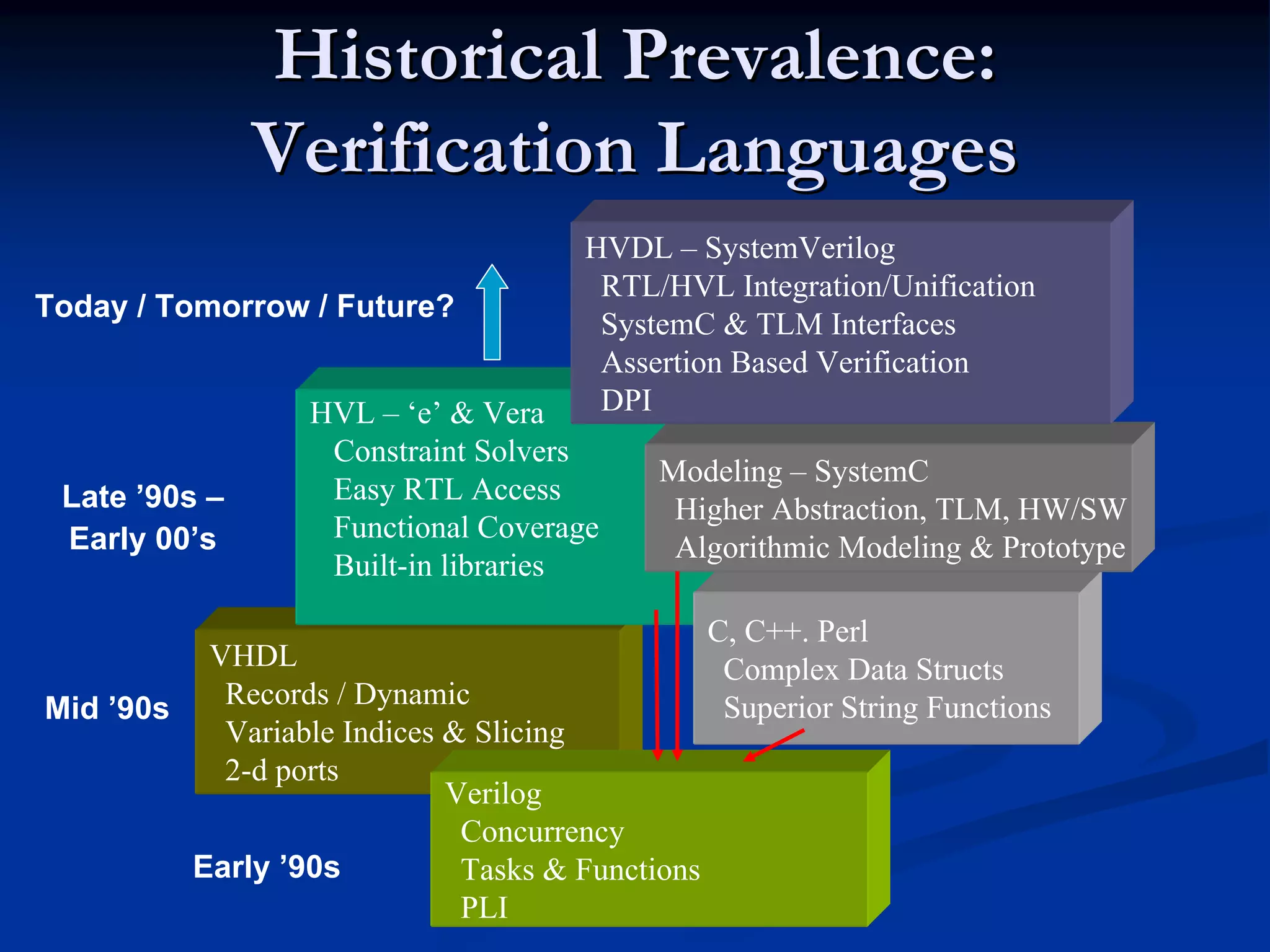

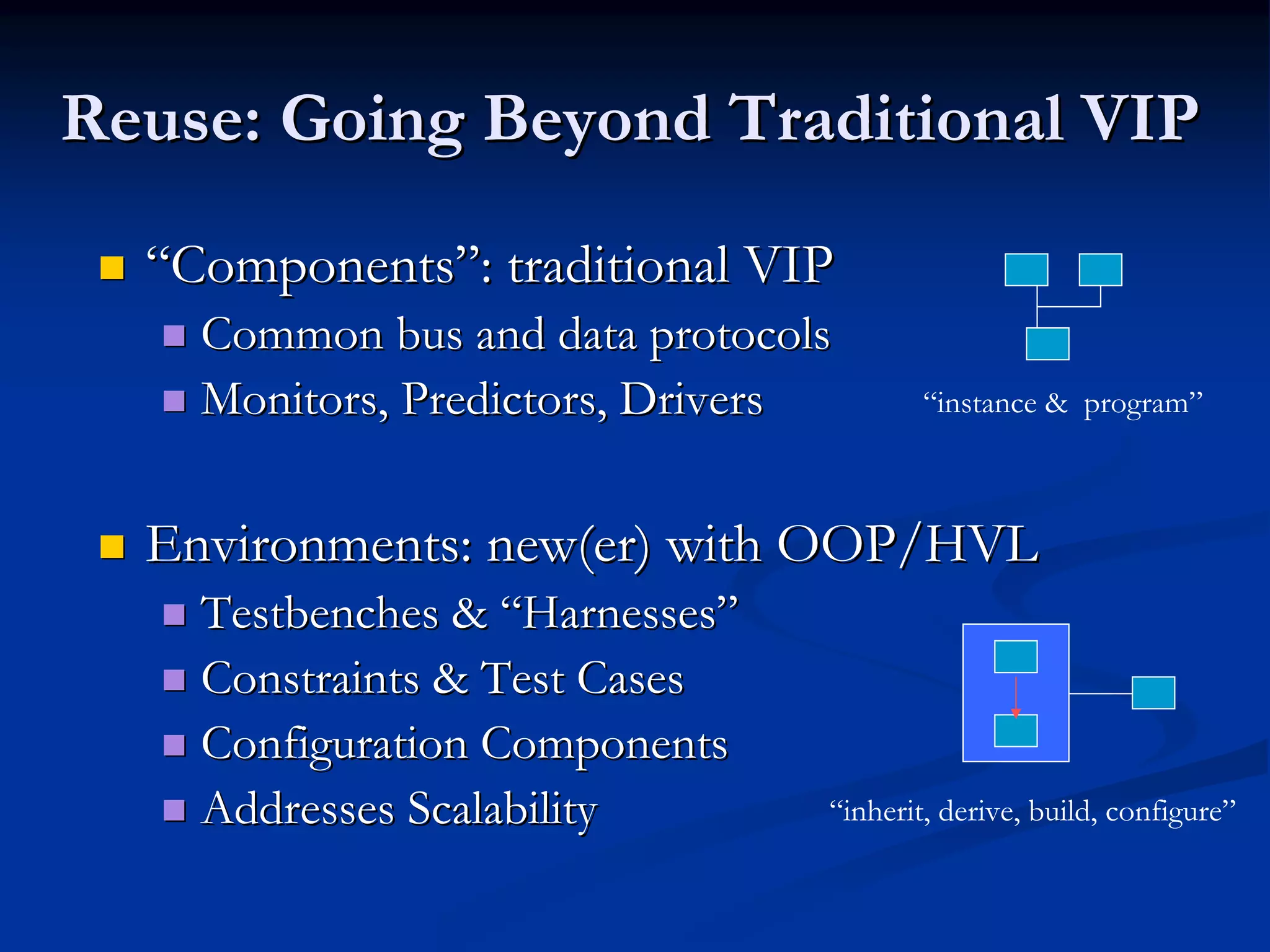

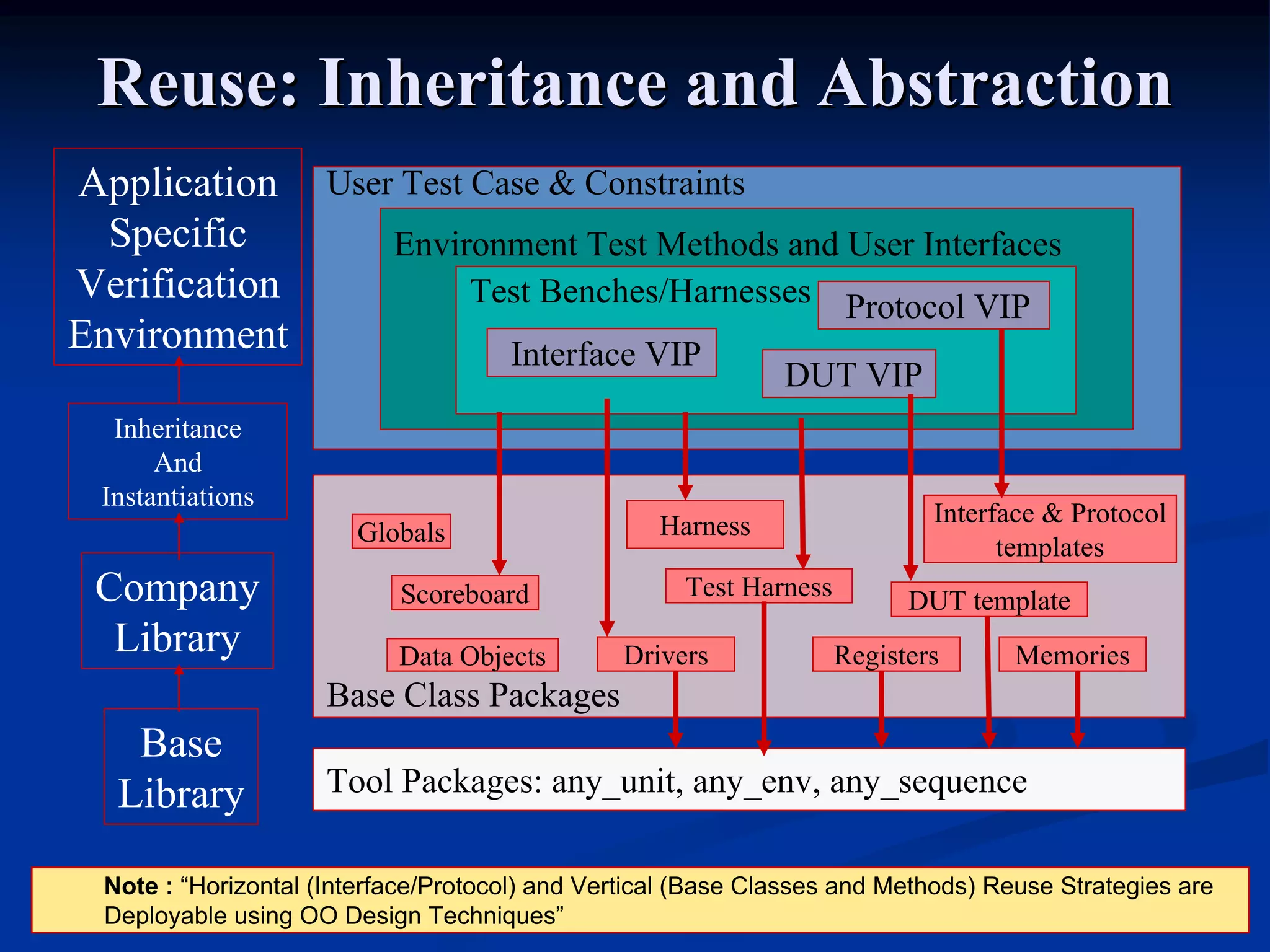

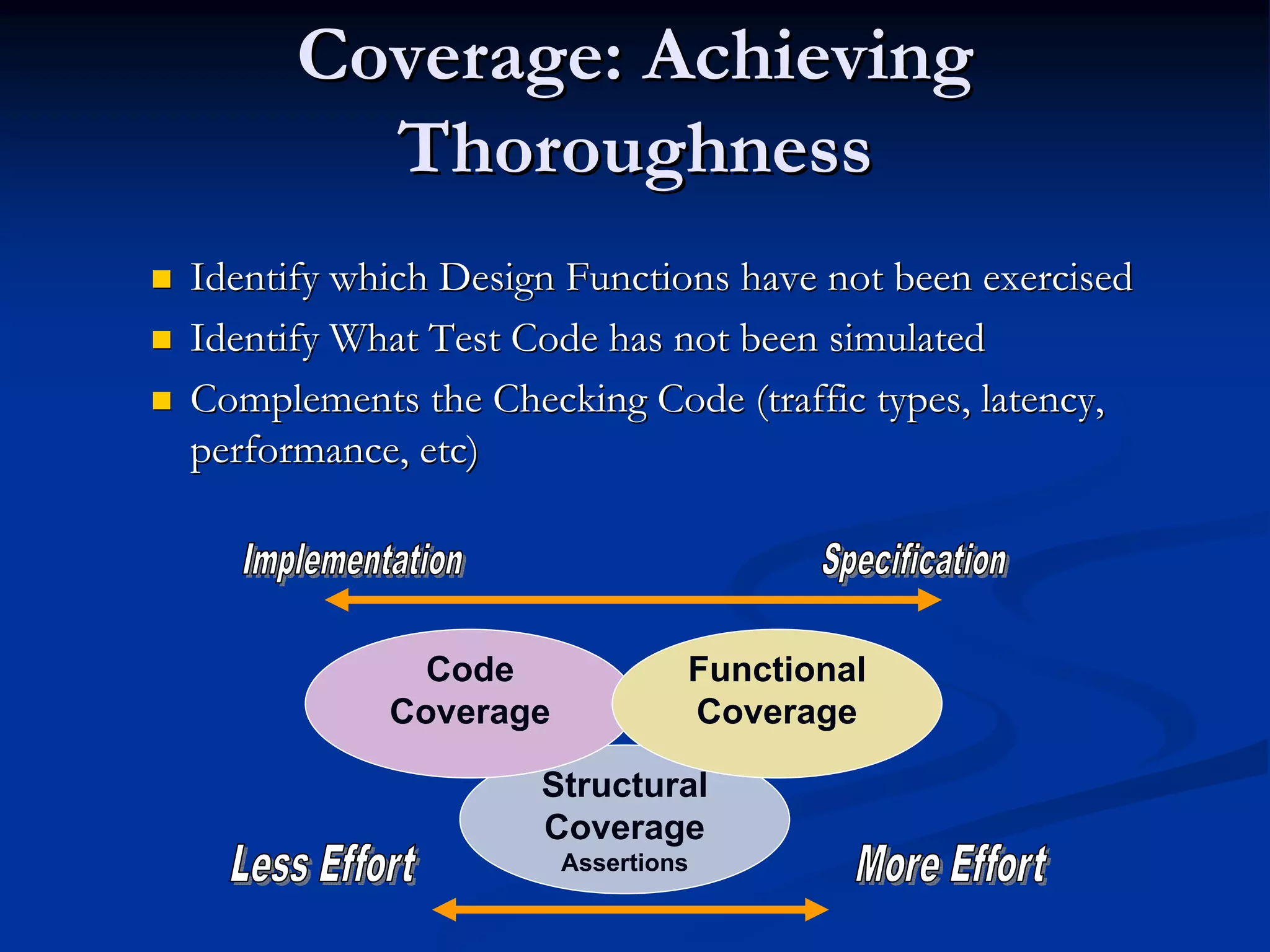

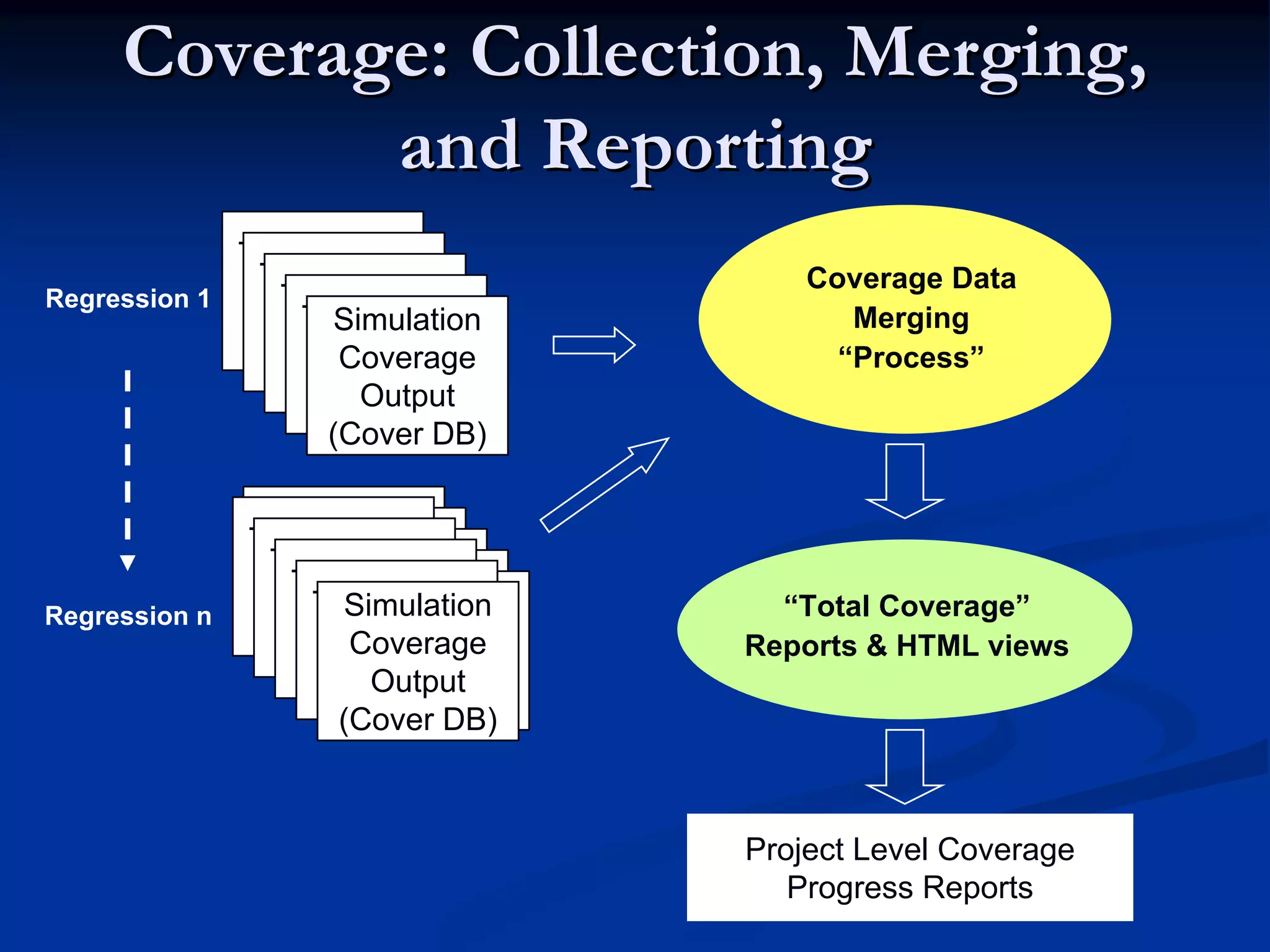

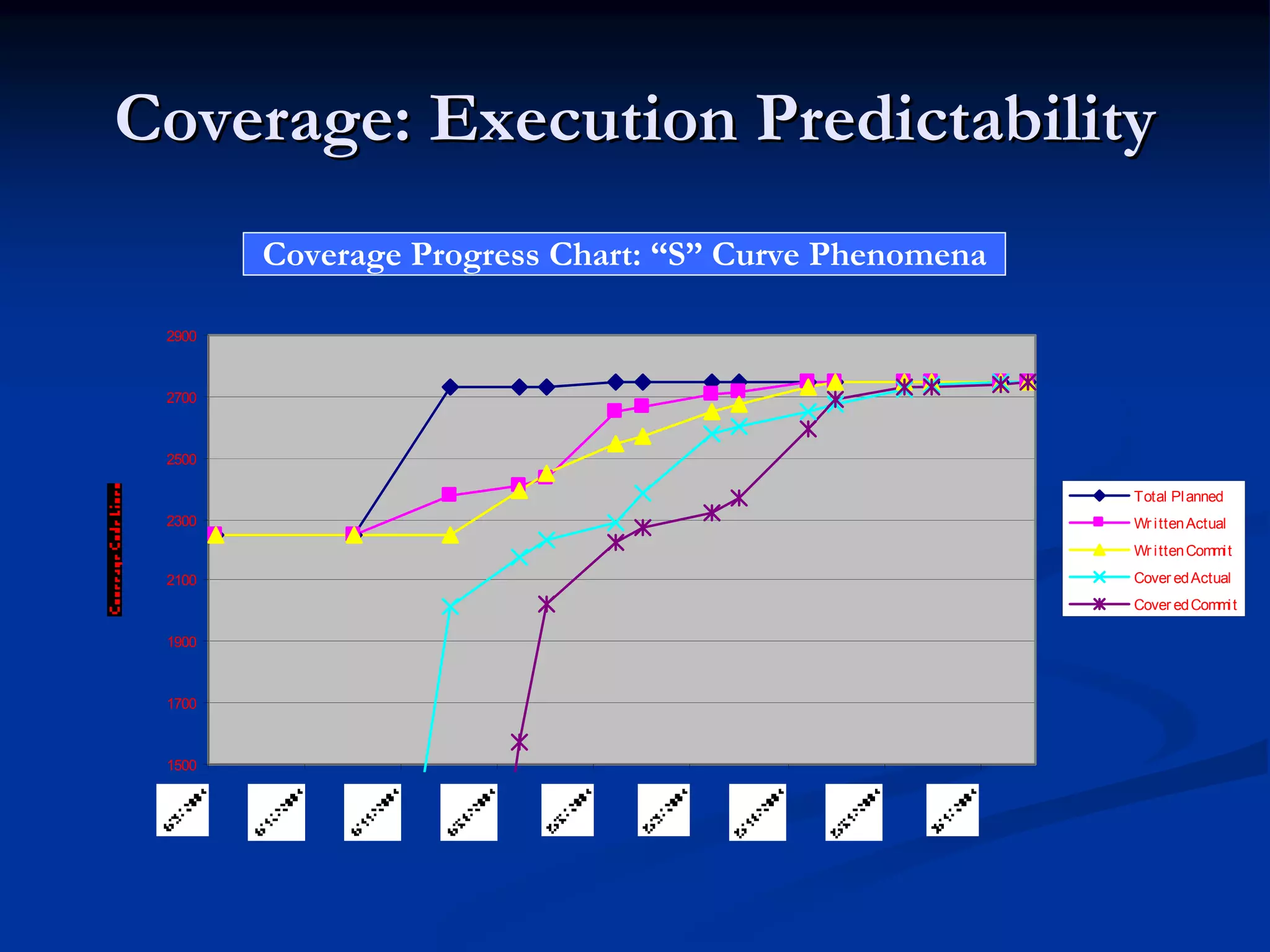

The document discusses topics related to chip verification including an overview of the DVClub, the historical evolution of verification languages and simulators, and various verification techniques such as reuse, coverage, regression engineering, planning, and qualification. The DVClub is a voluntary community group that discusses present day verification challenges through presentations of ideas, experiences, and results. Verification has evolved from producing test vectors and simulating outputs to developing sophisticated methodologies that automate efficiency and thoroughness through techniques like reuse, coverage-driven verification, regression engineering, and planning.