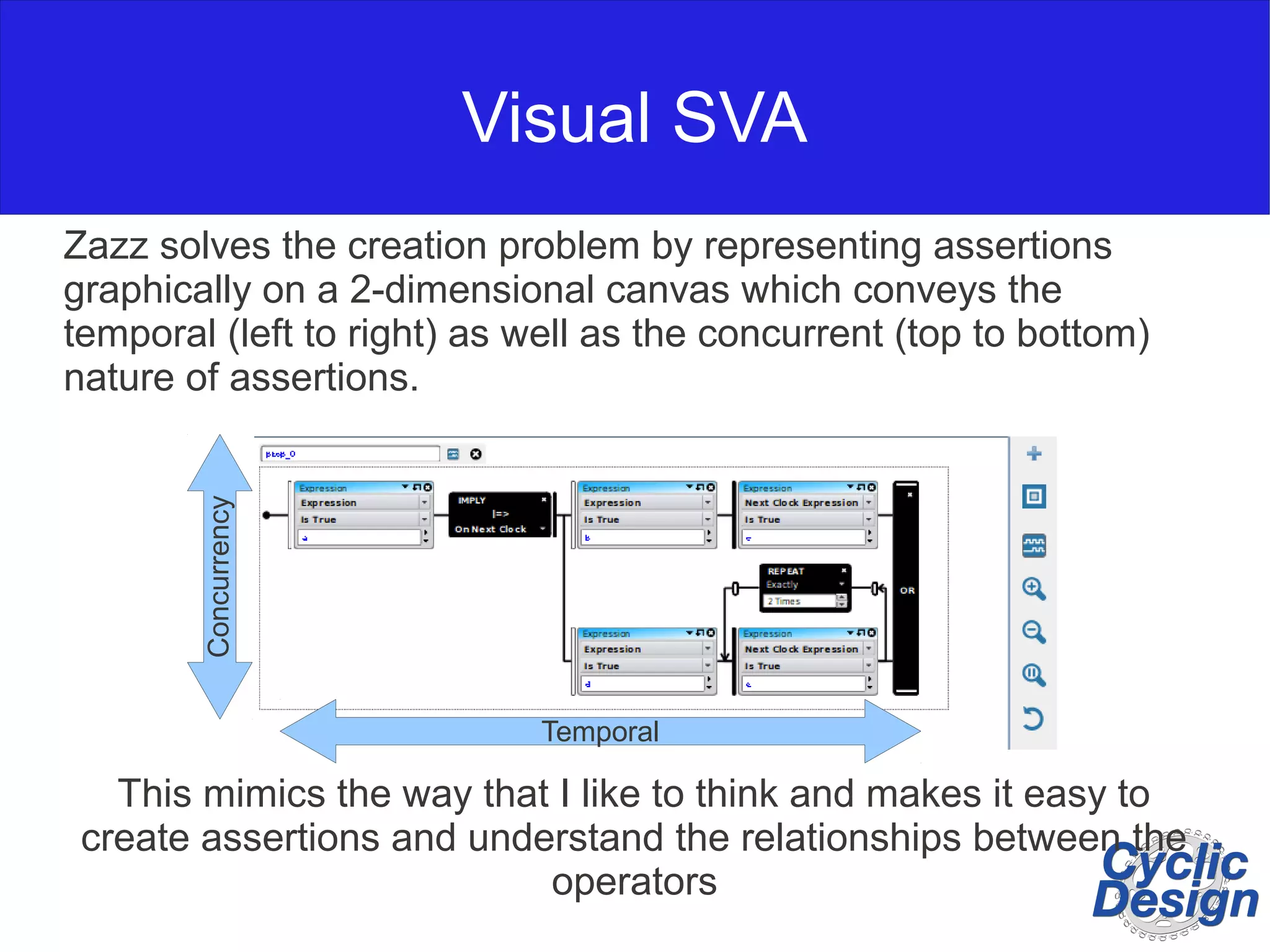

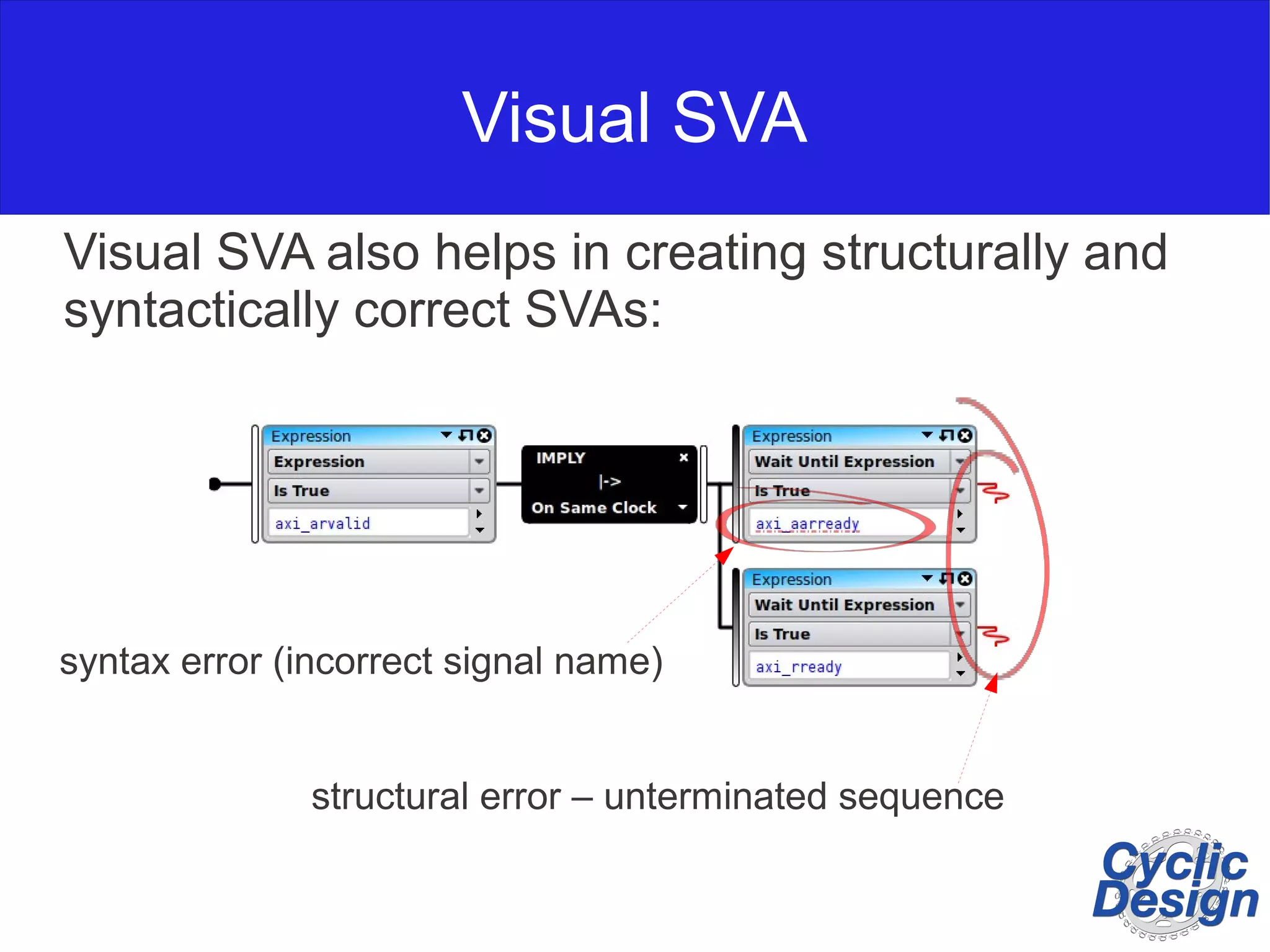

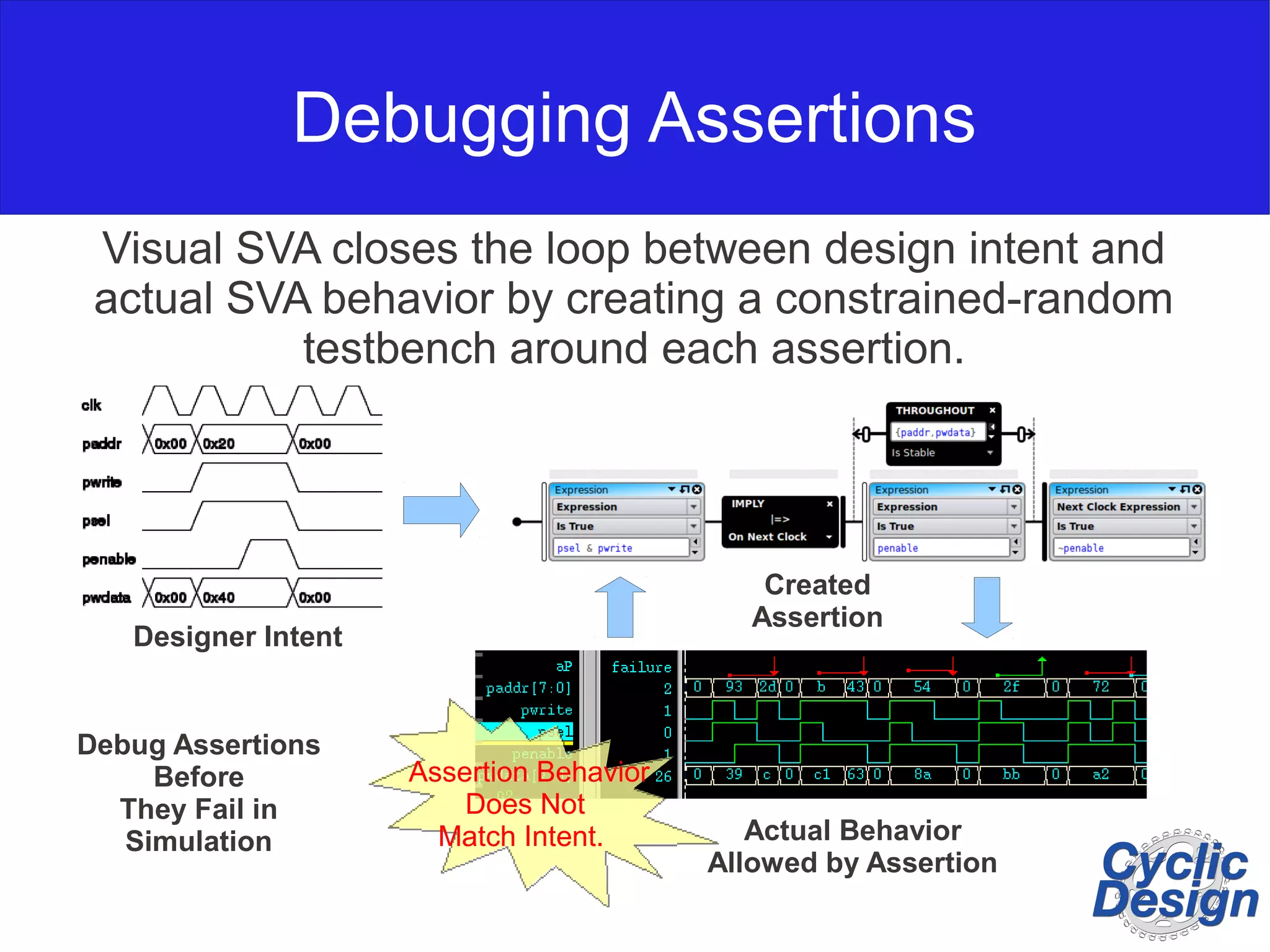

1) Visual SVA tools like Zazz allow designers to create complex SystemVerilog assertions through a graphical interface, addressing issues with SVA syntax. 2) Zazz also enables debugging assertions as they are created by generating constrained random tests, improving assertion quality before use in verification. 3) Using assertions improved the author's verification and debugging process, identifying errors sooner and in corner cases, and provided additional value to IP customers through early fault detection.