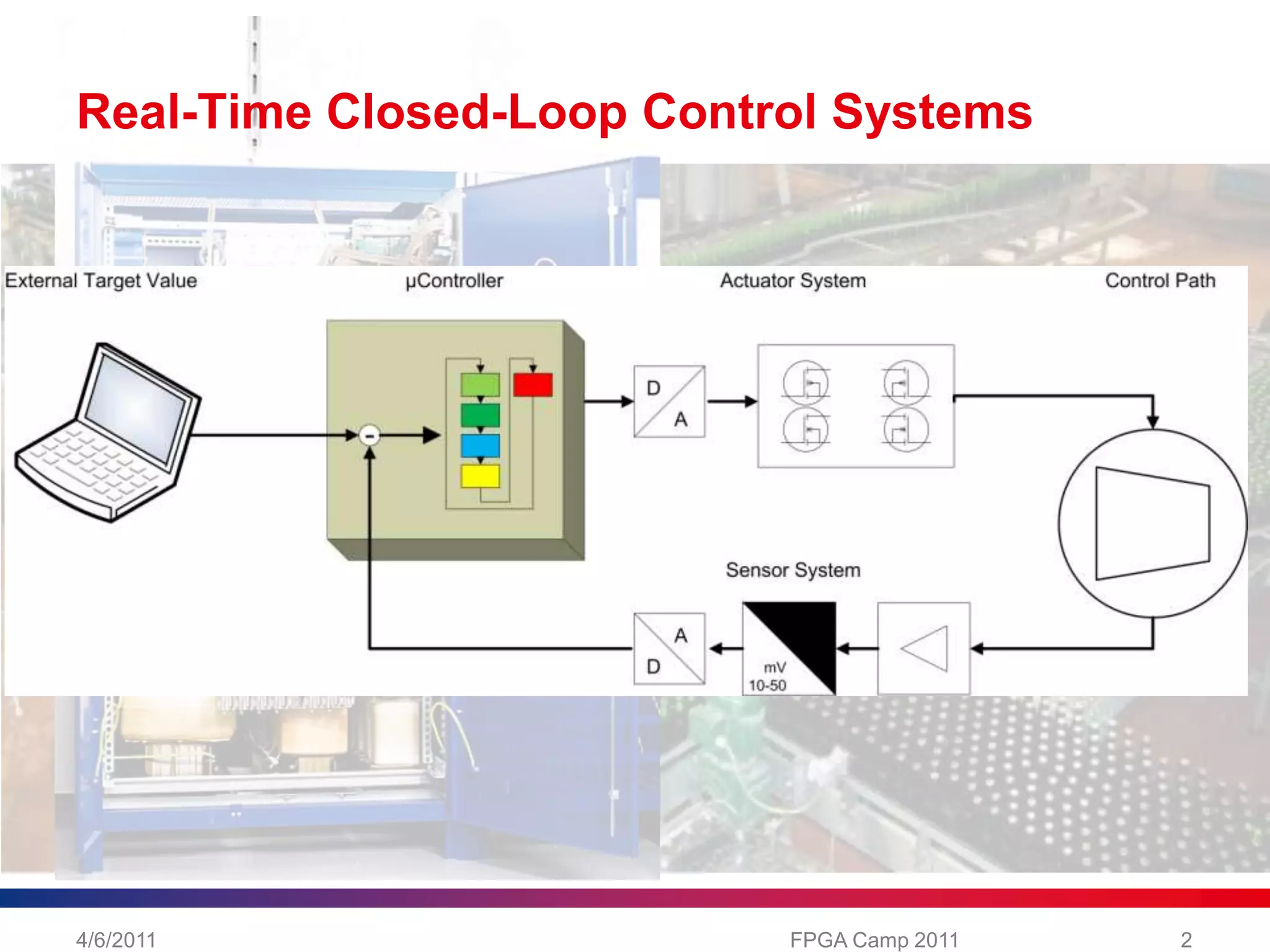

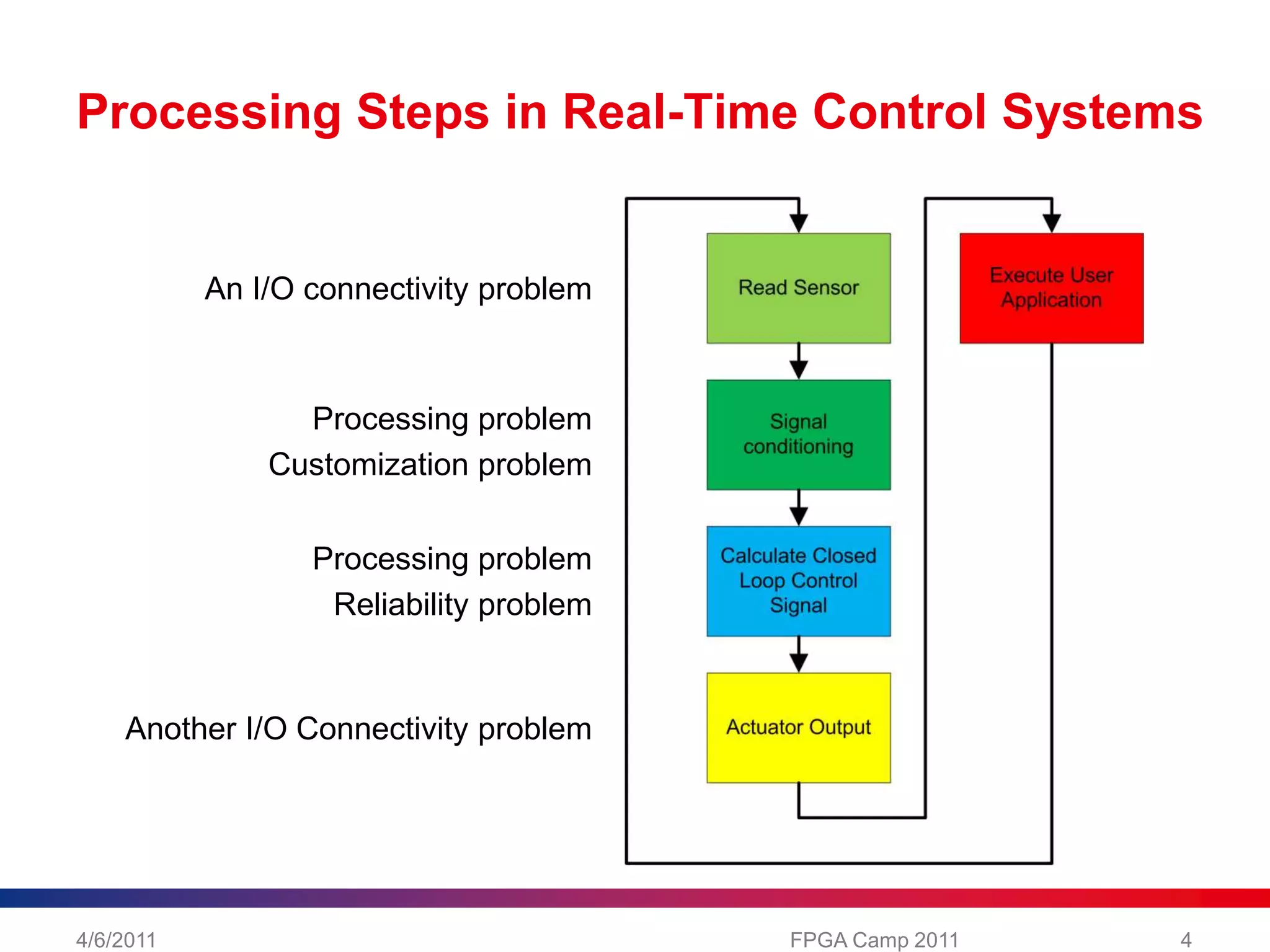

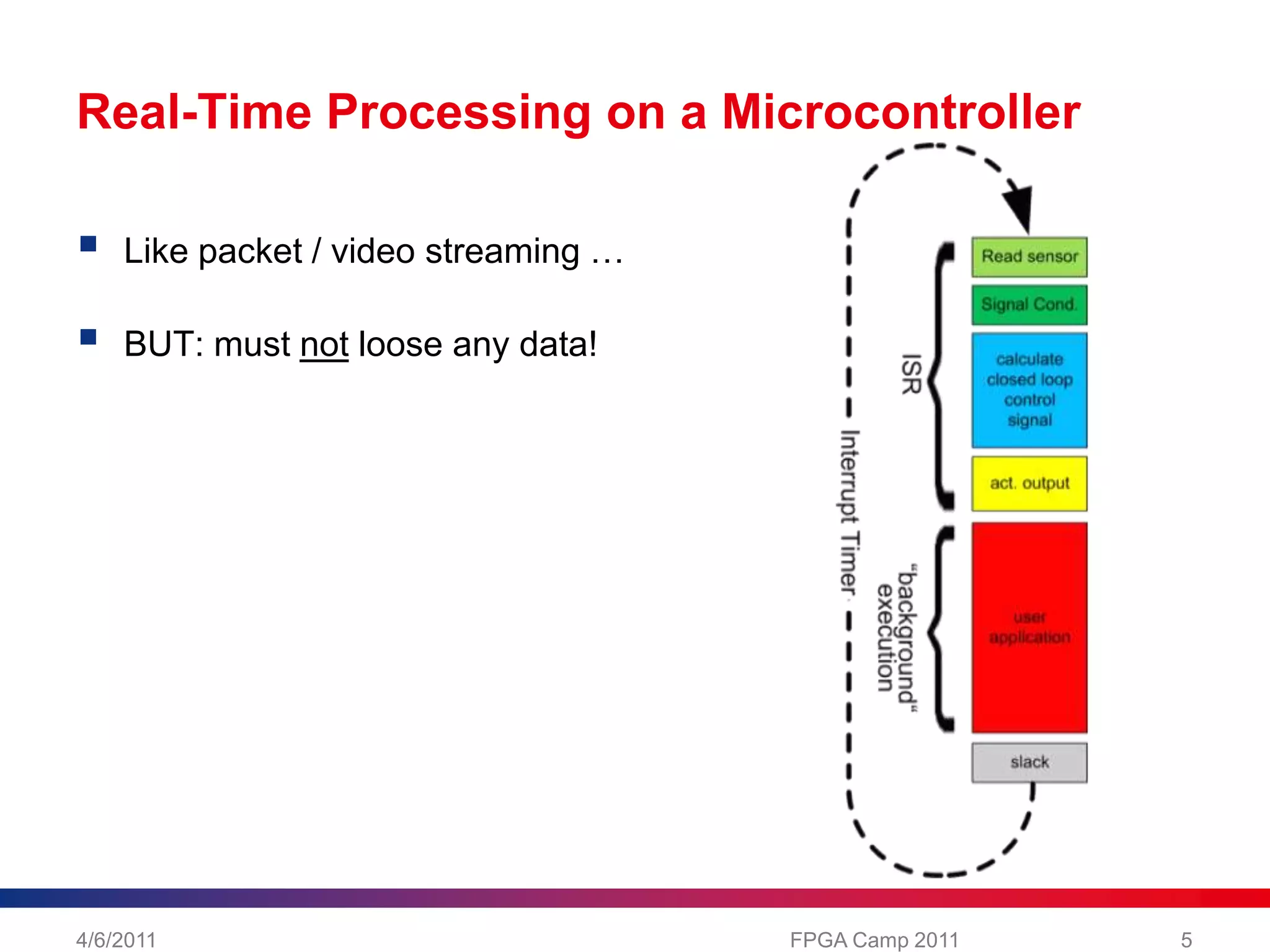

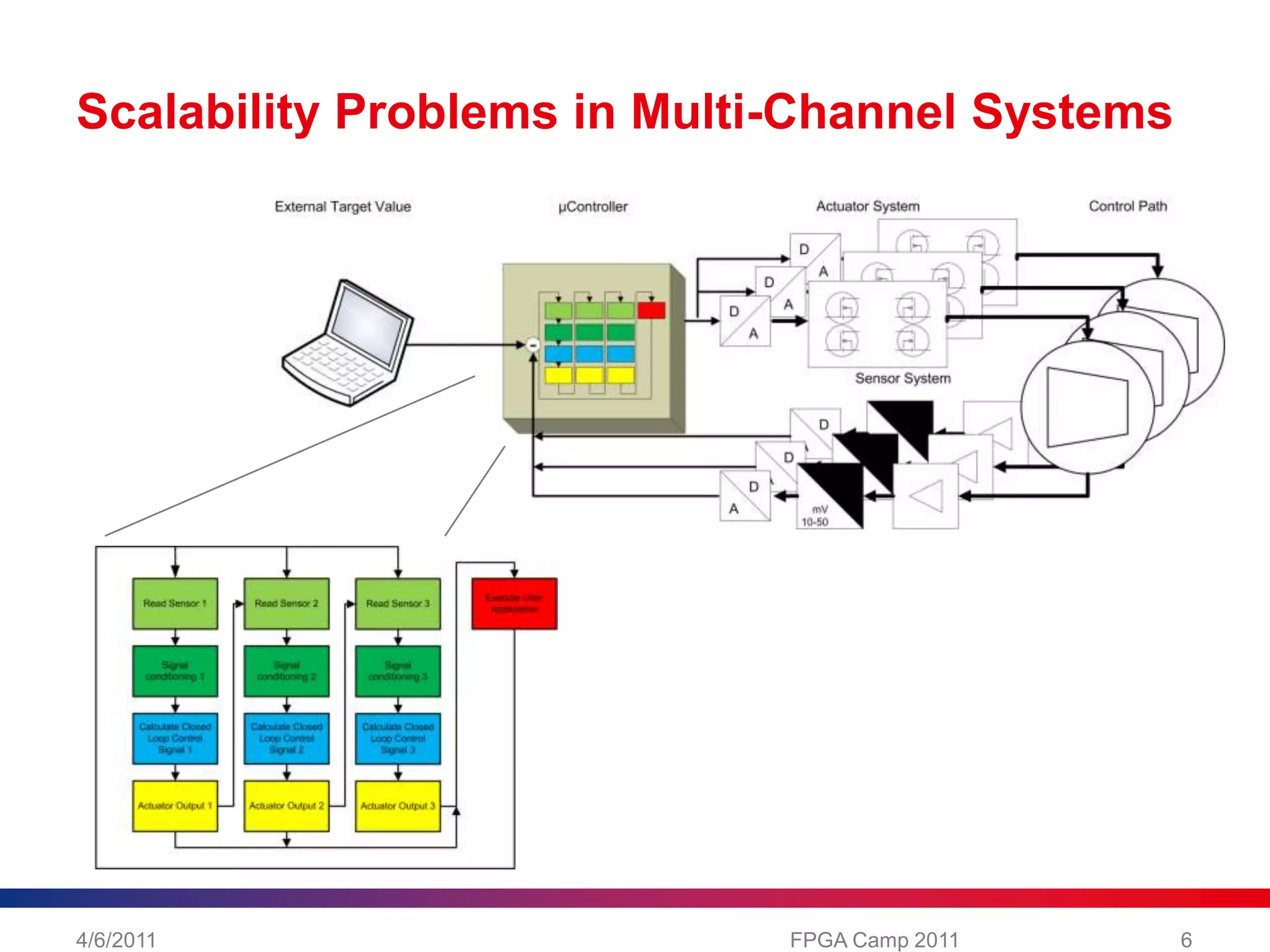

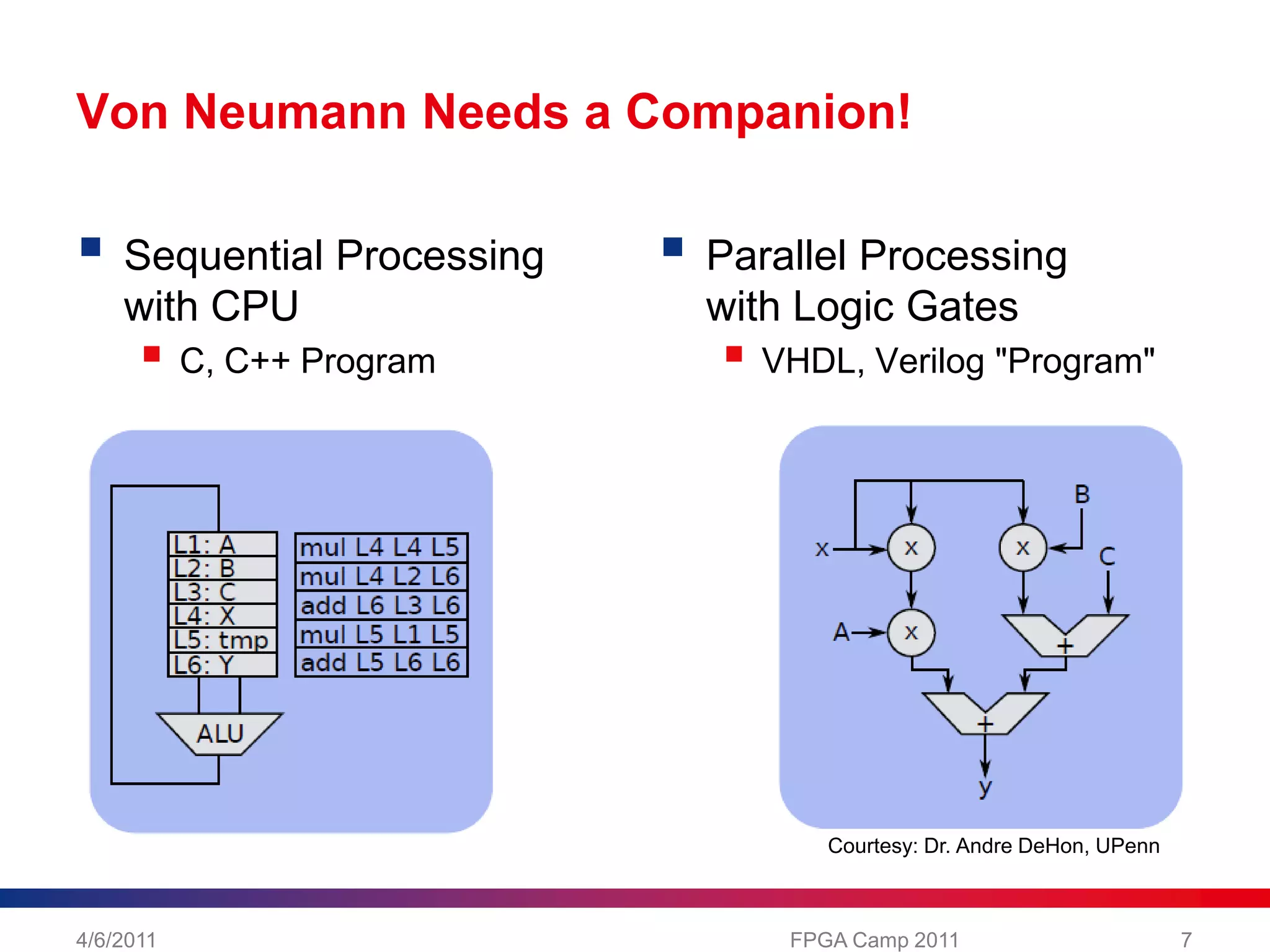

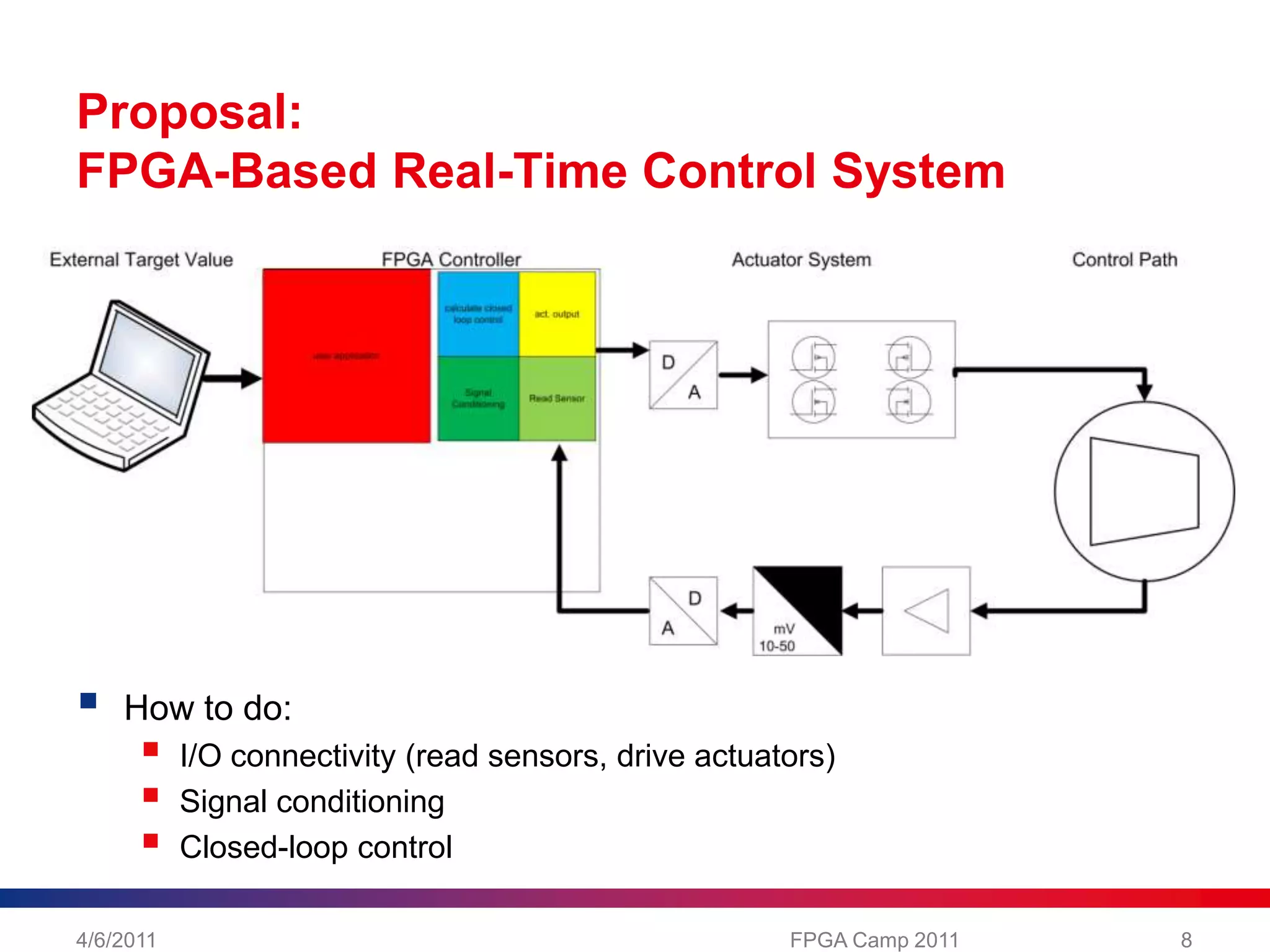

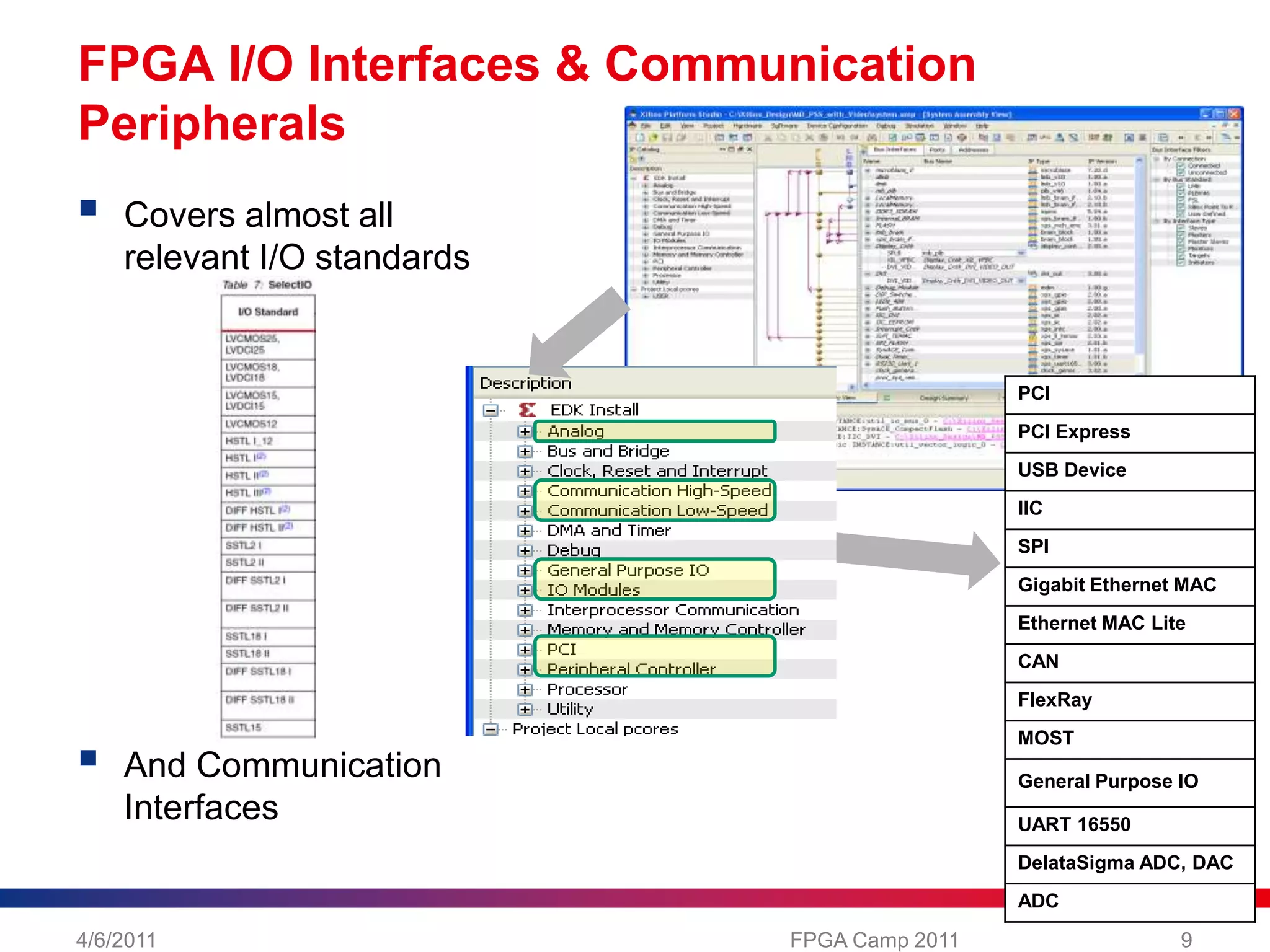

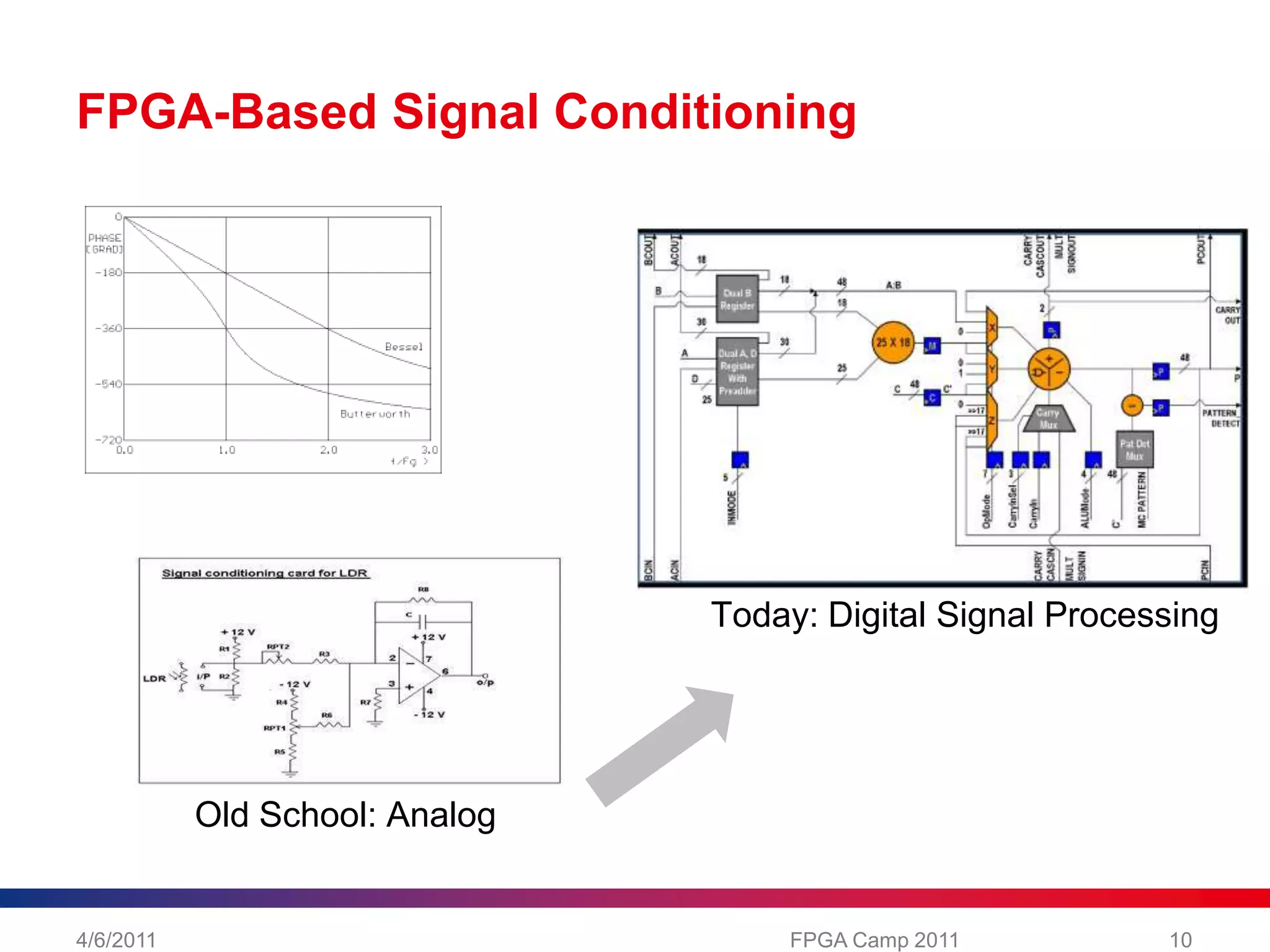

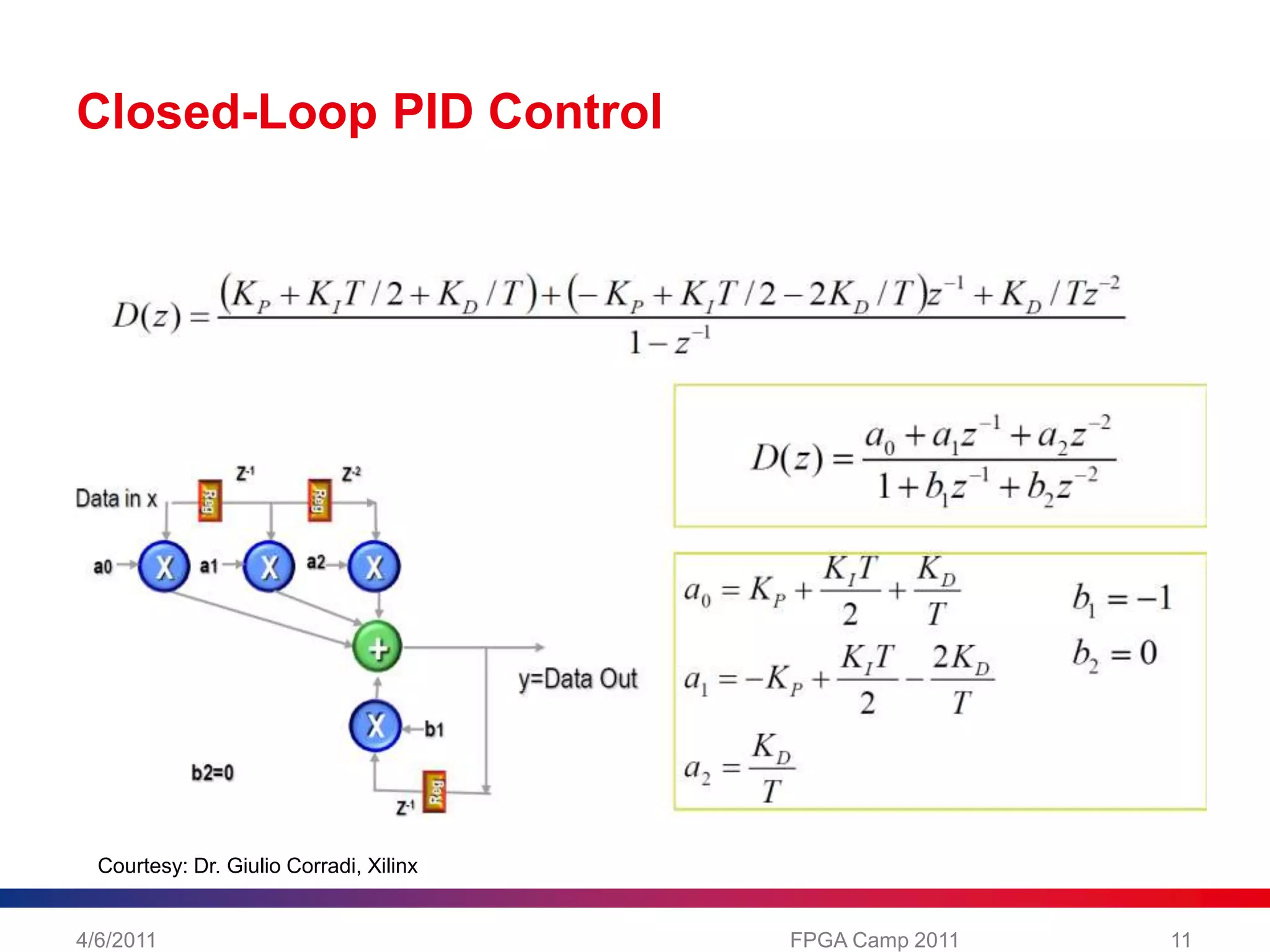

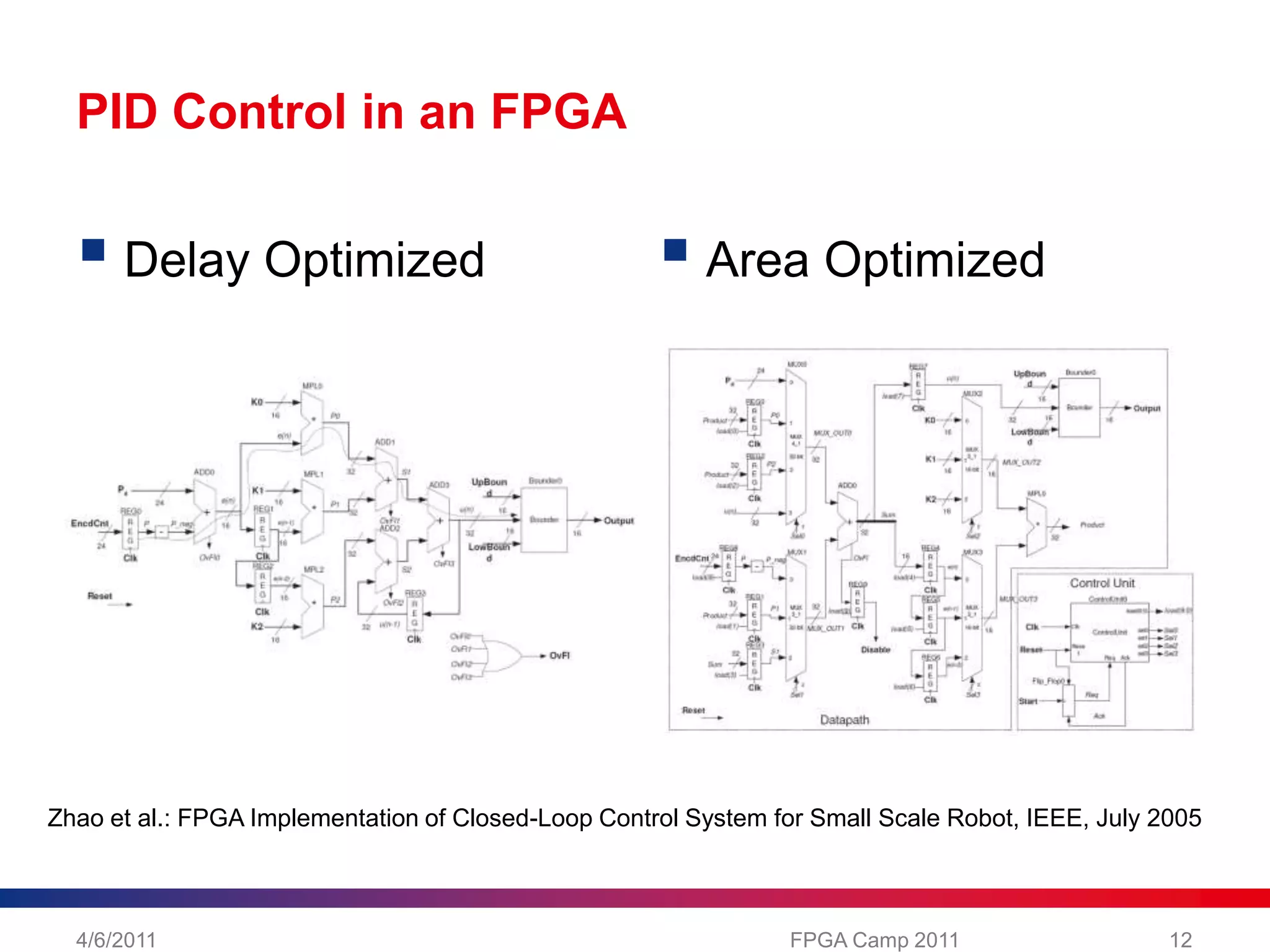

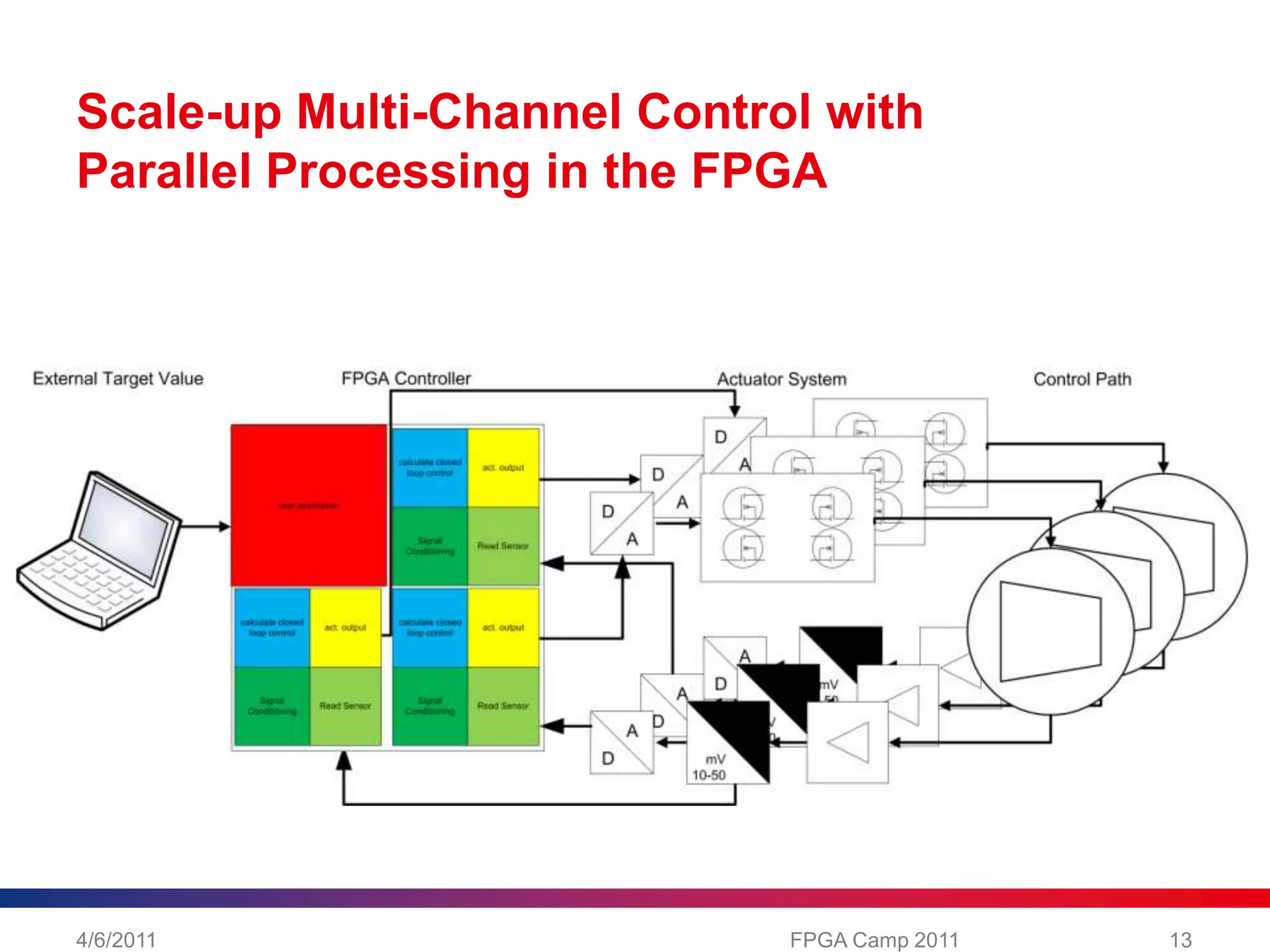

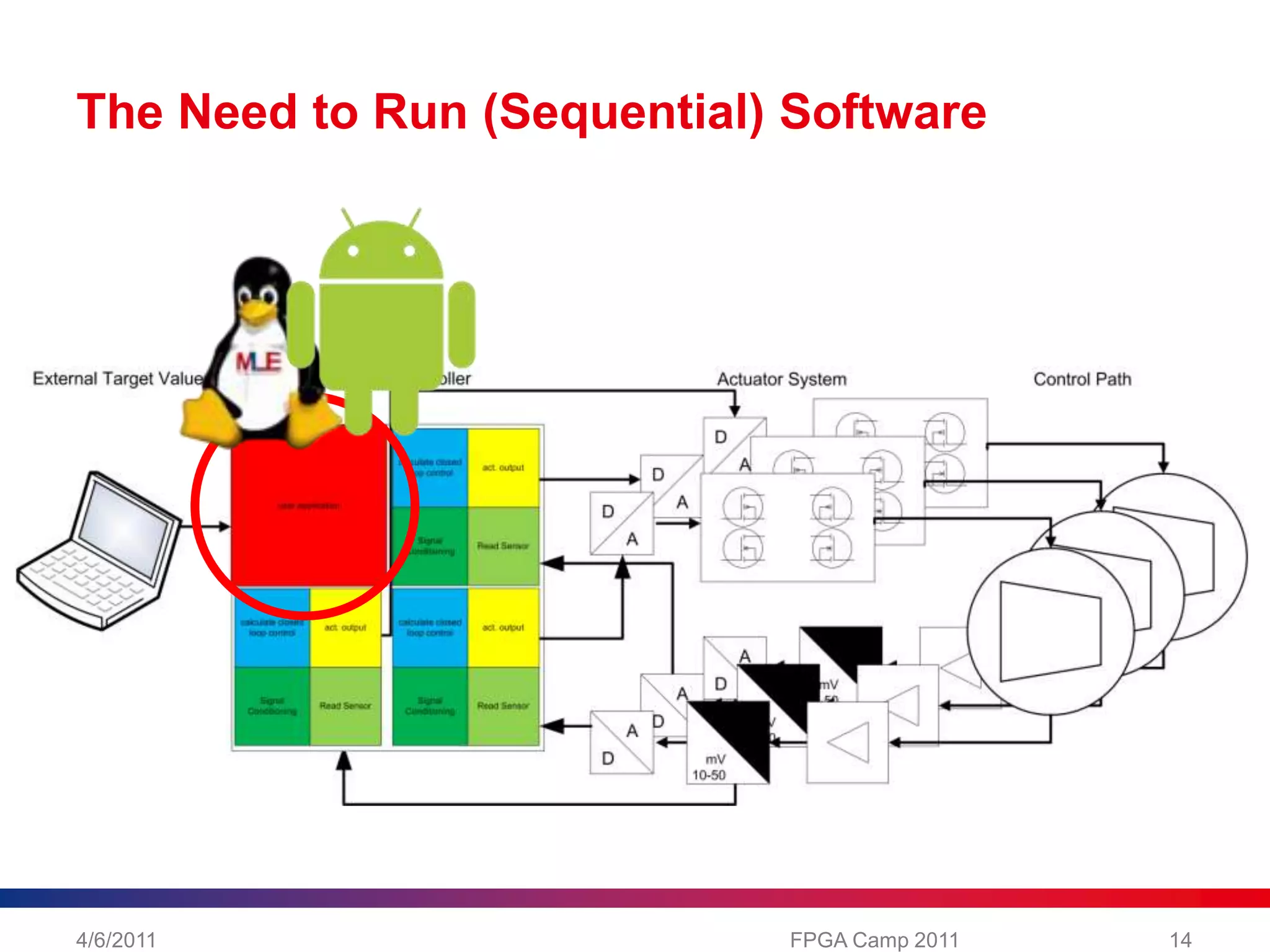

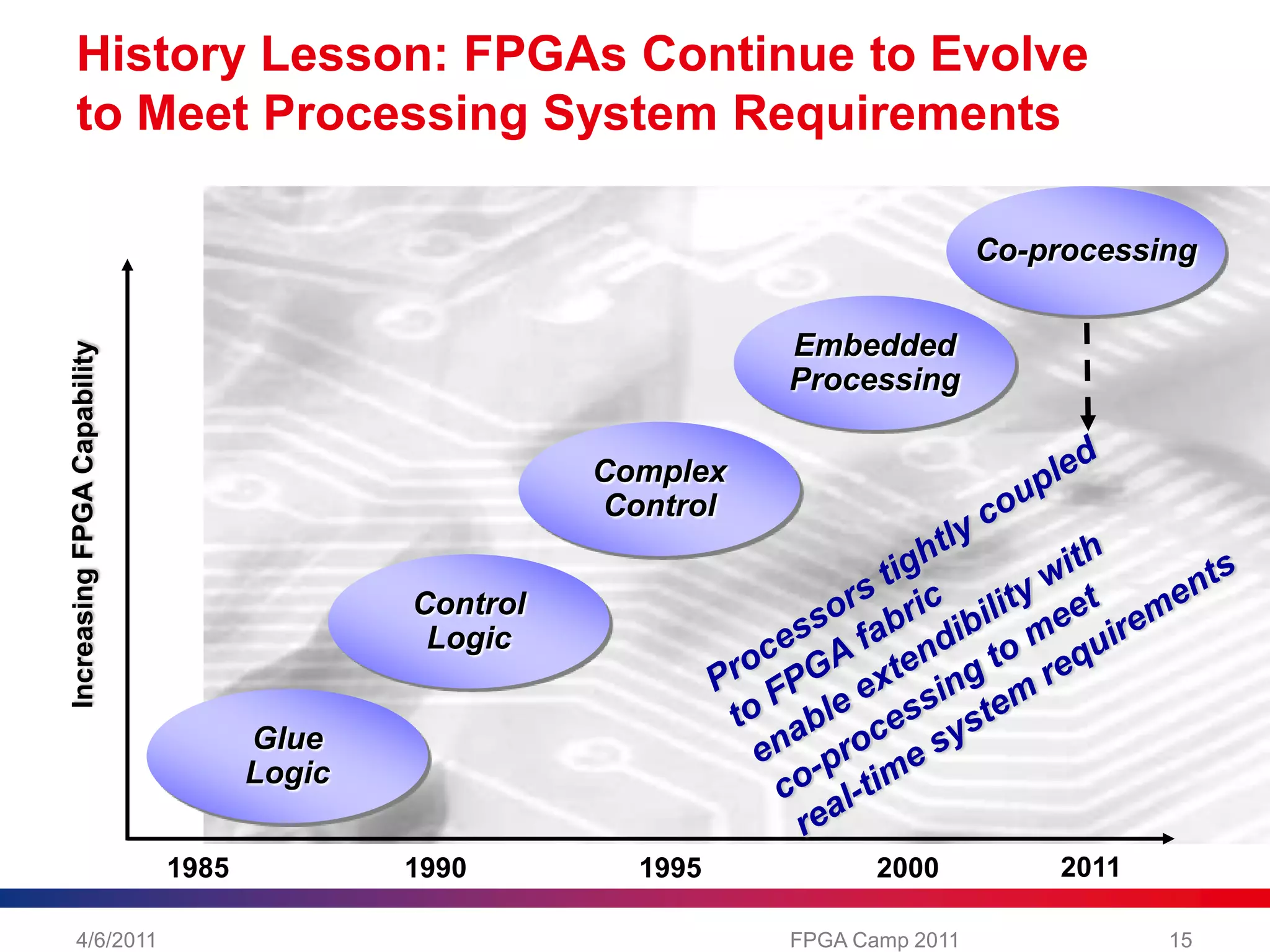

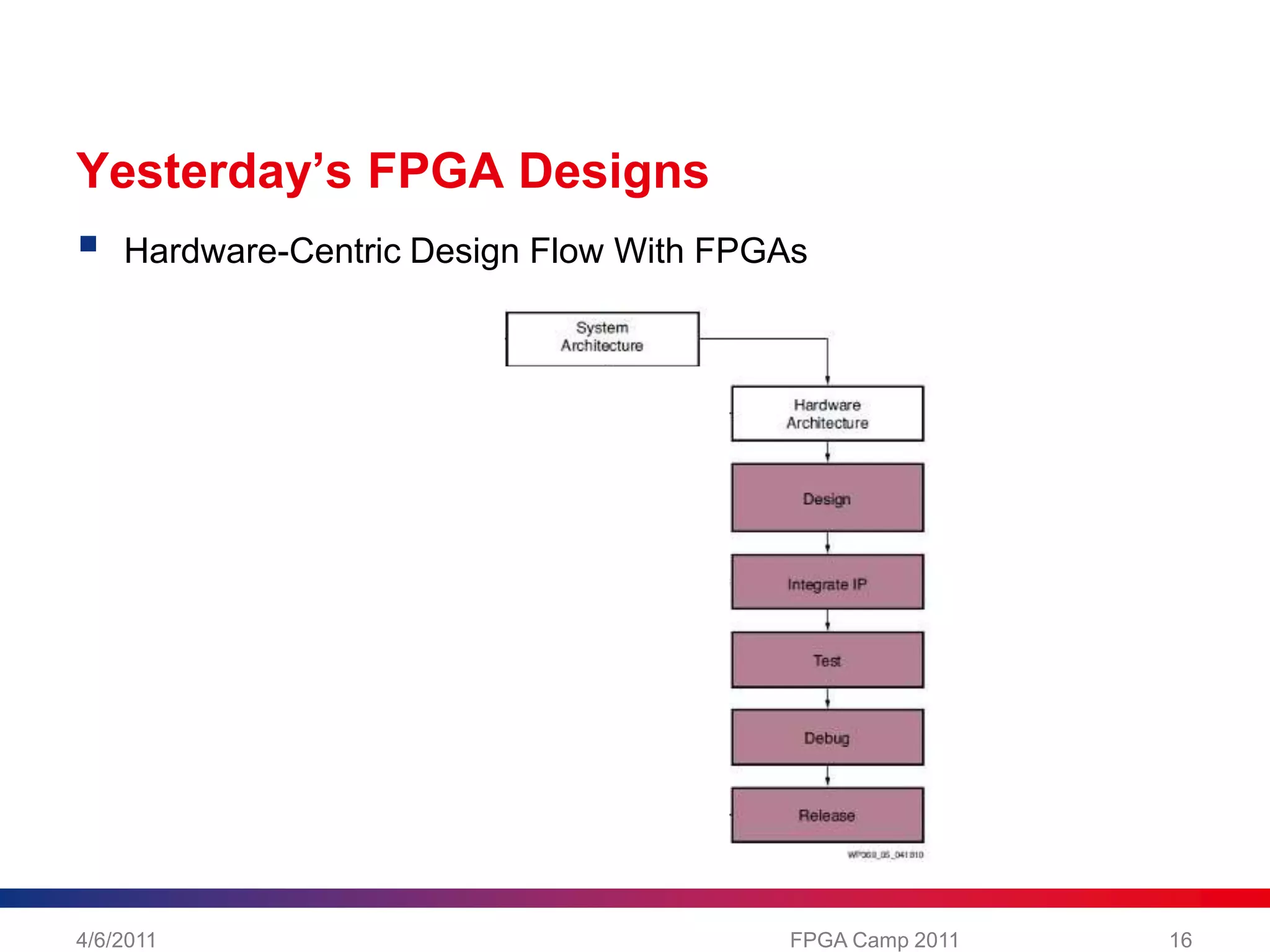

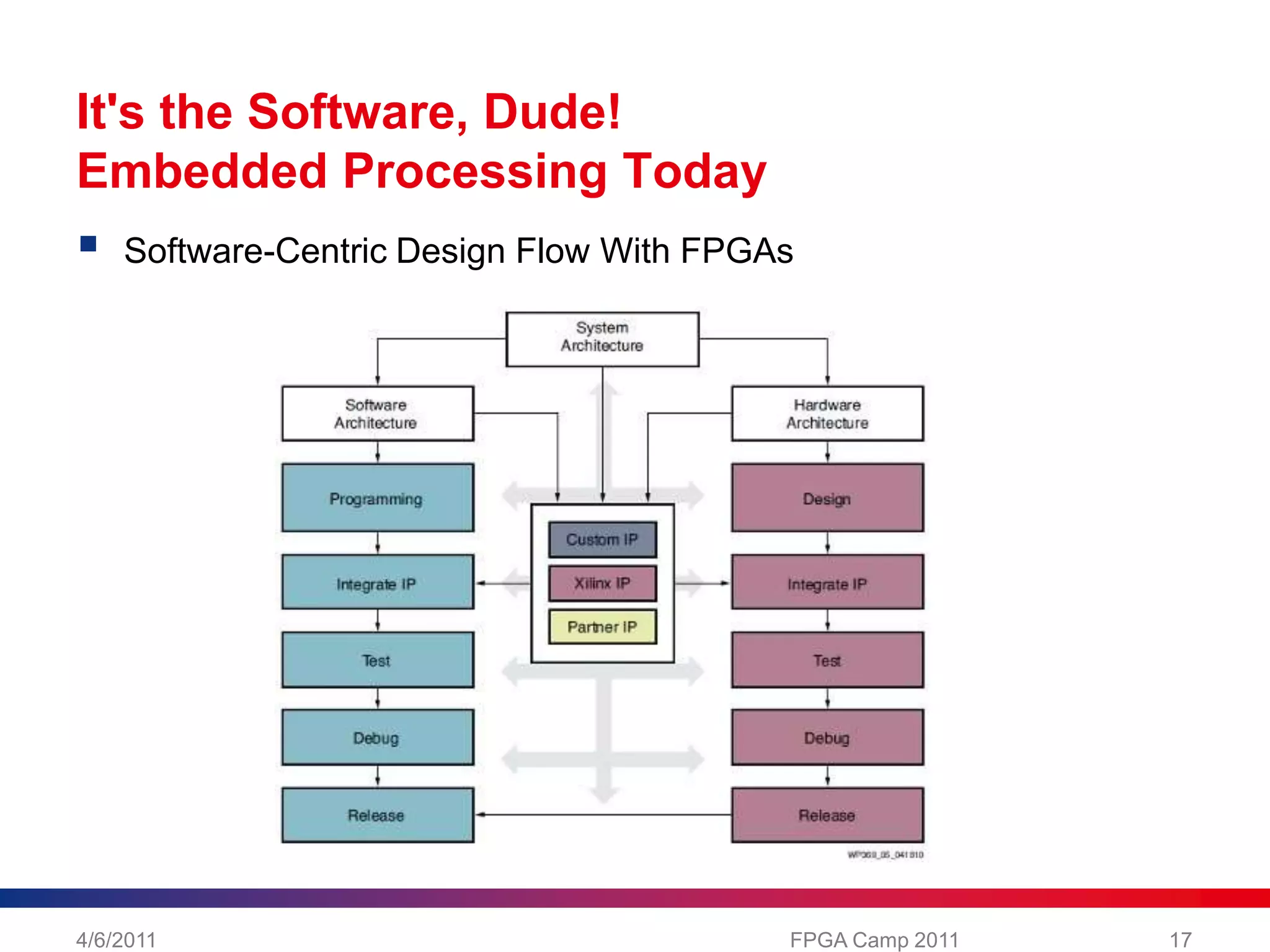

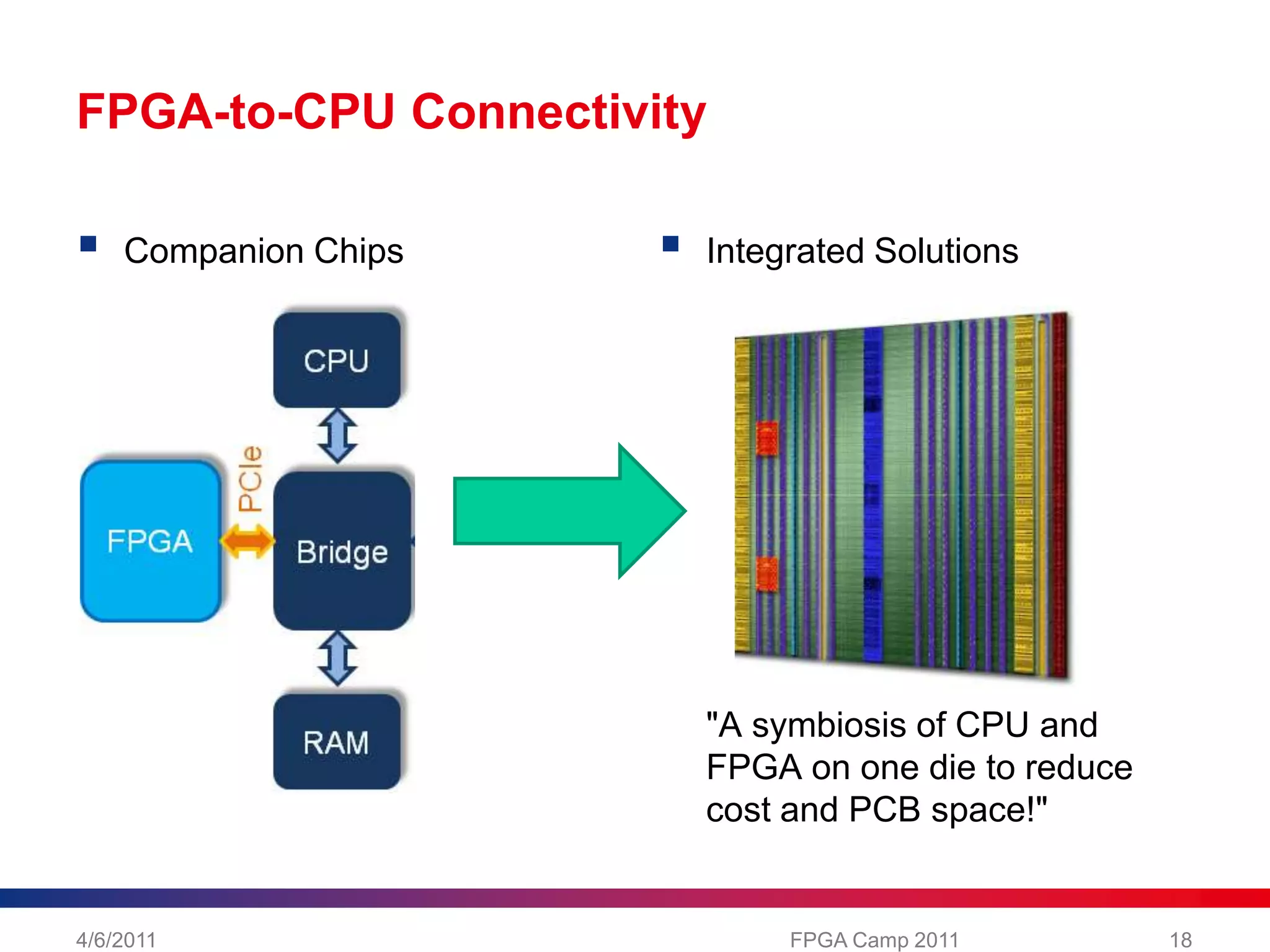

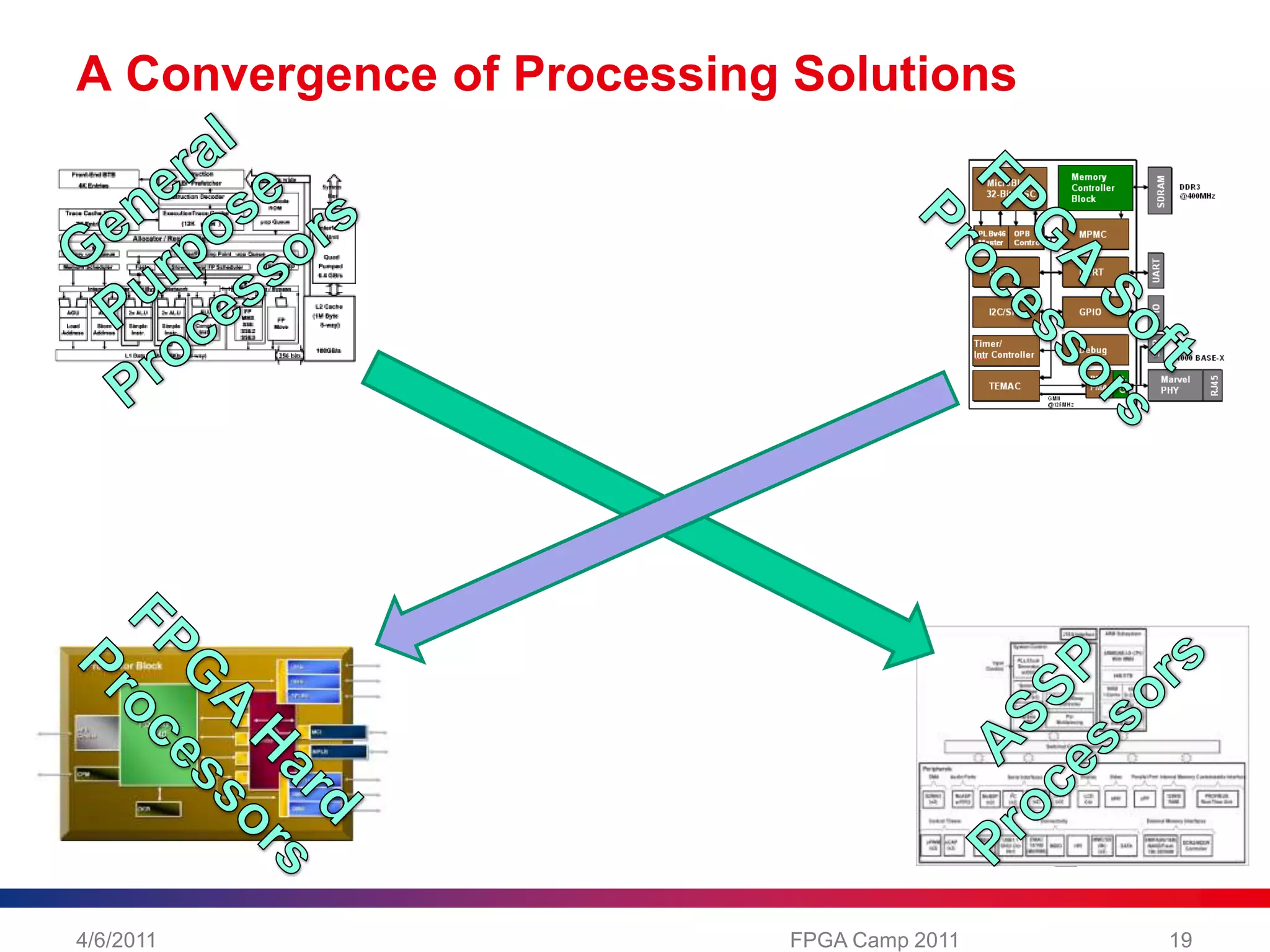

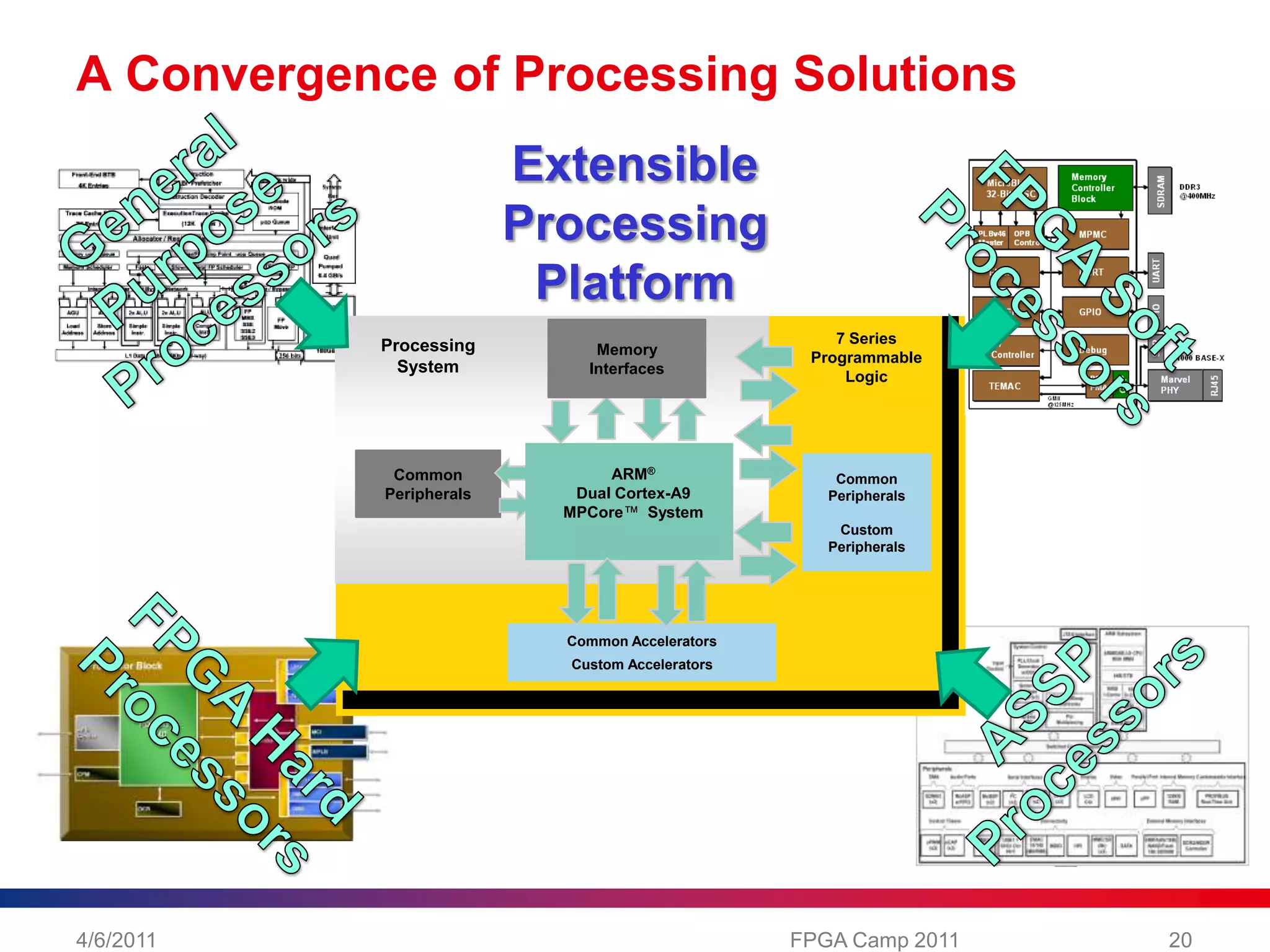

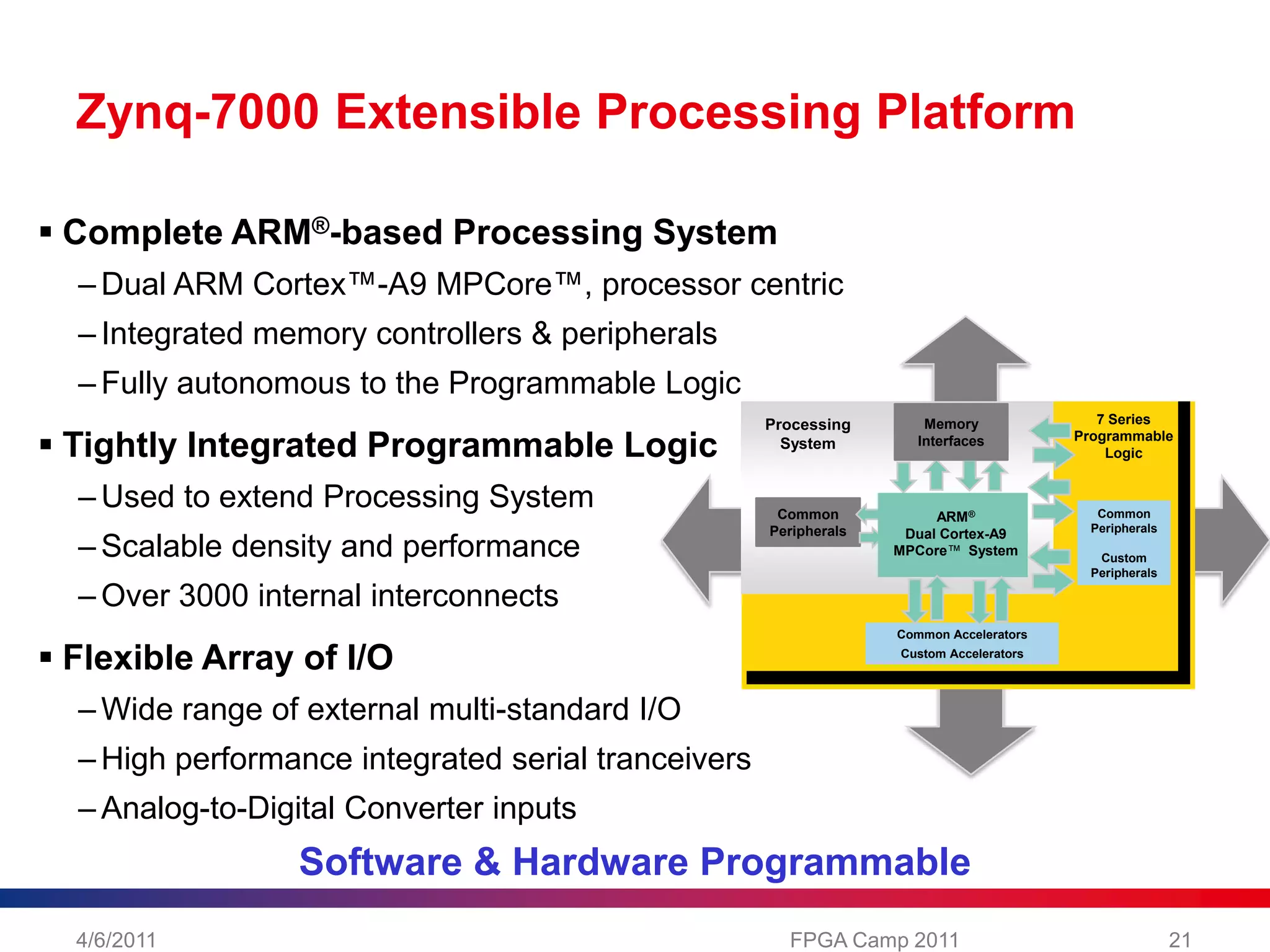

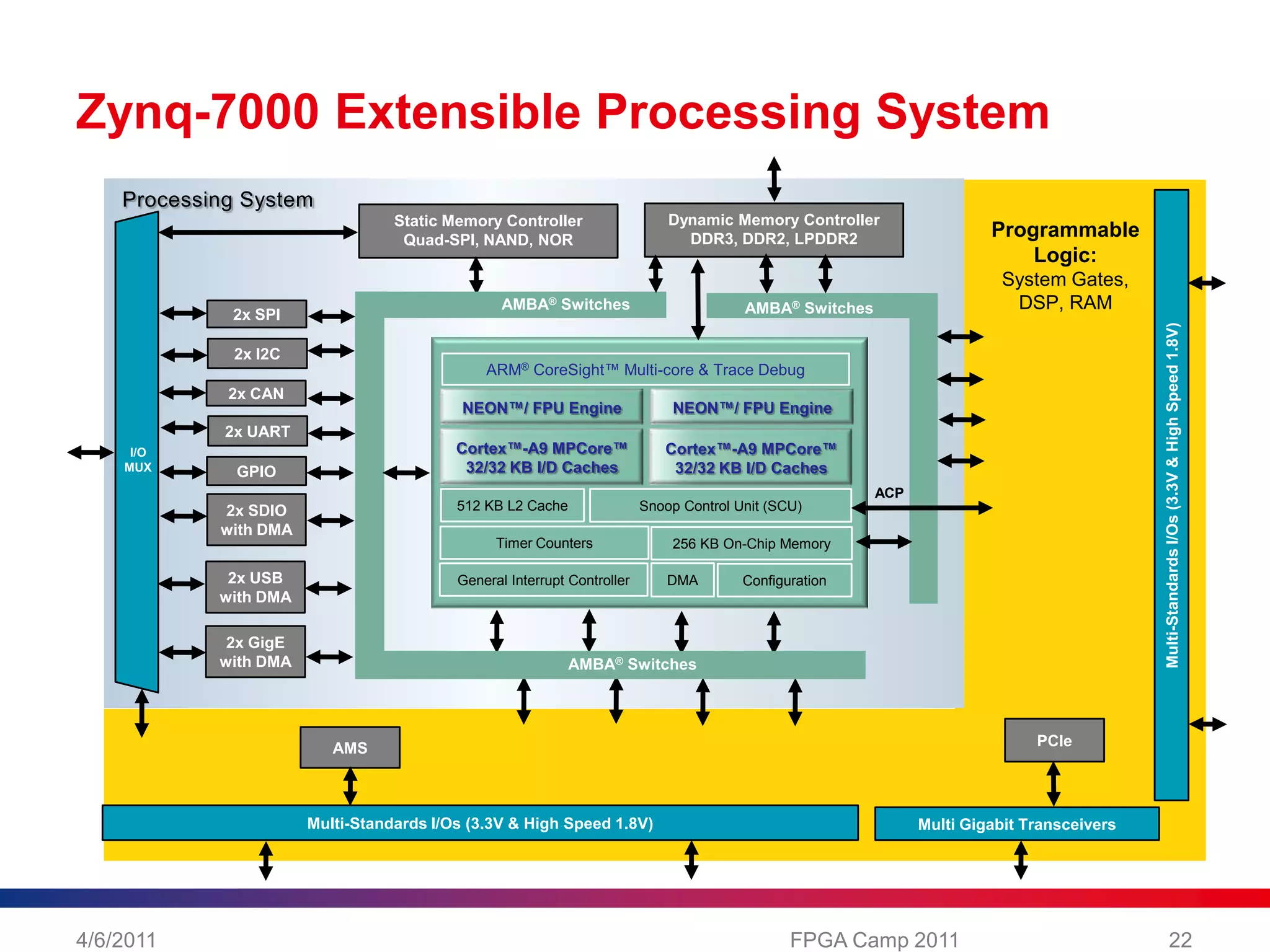

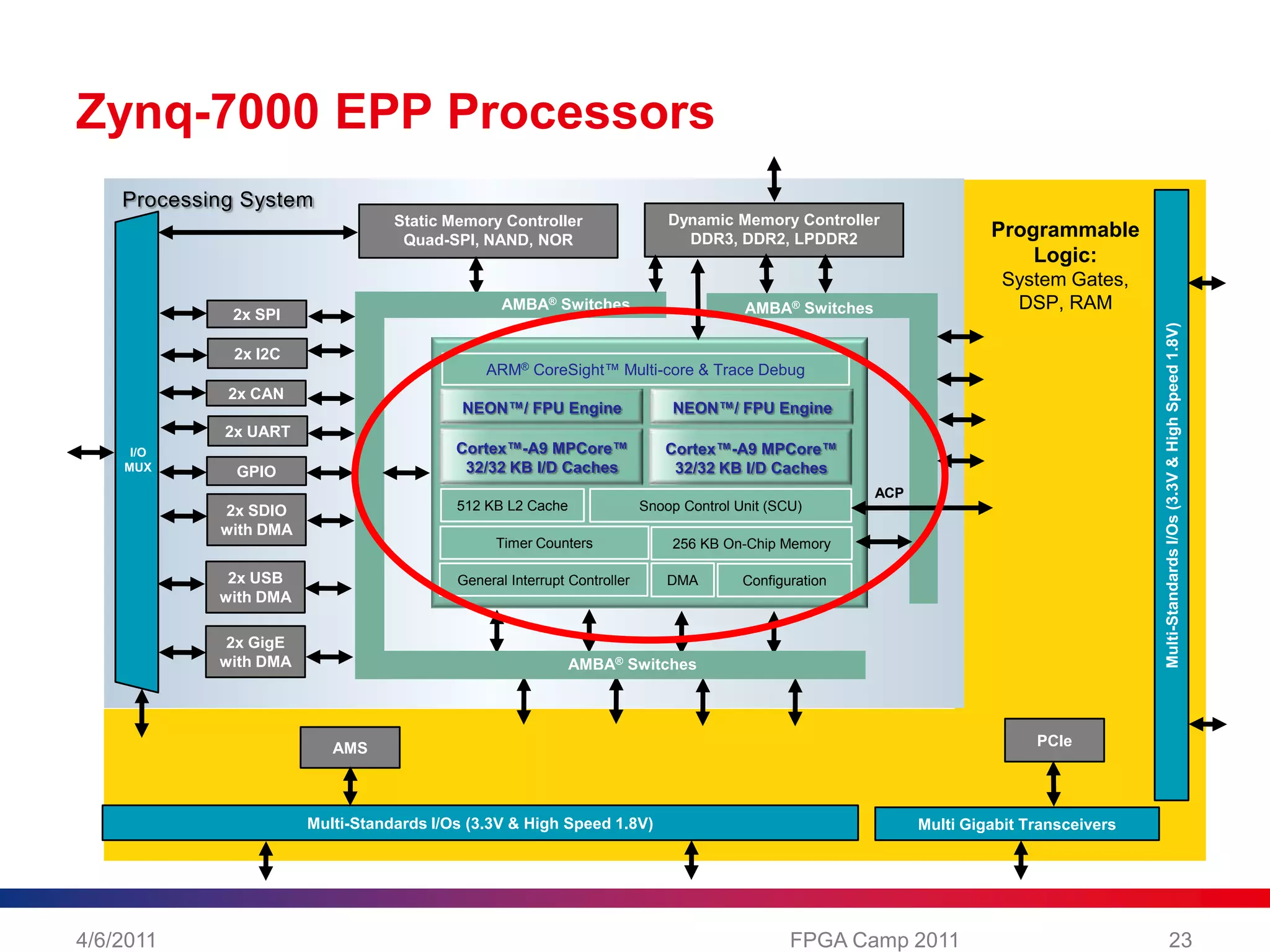

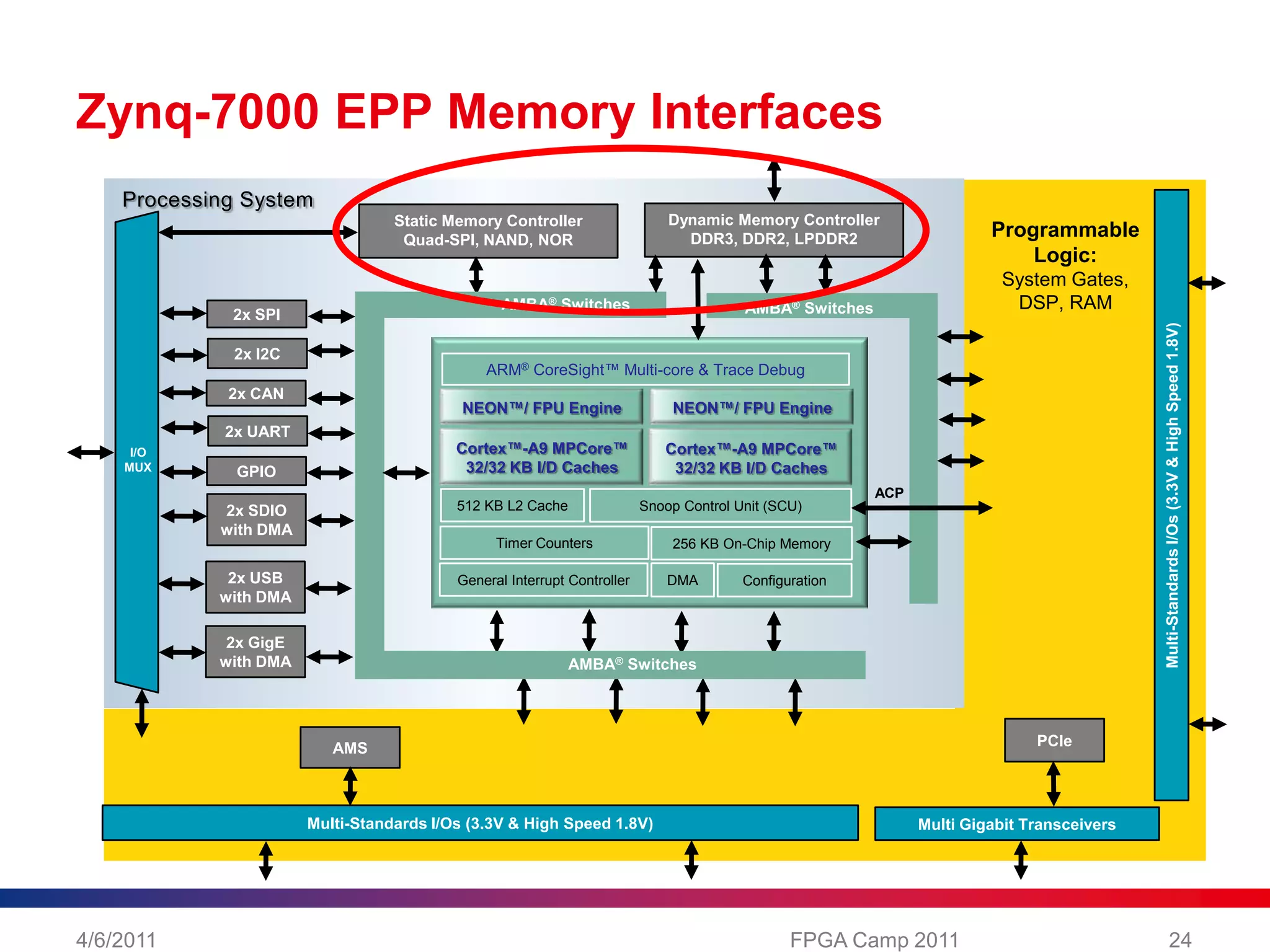

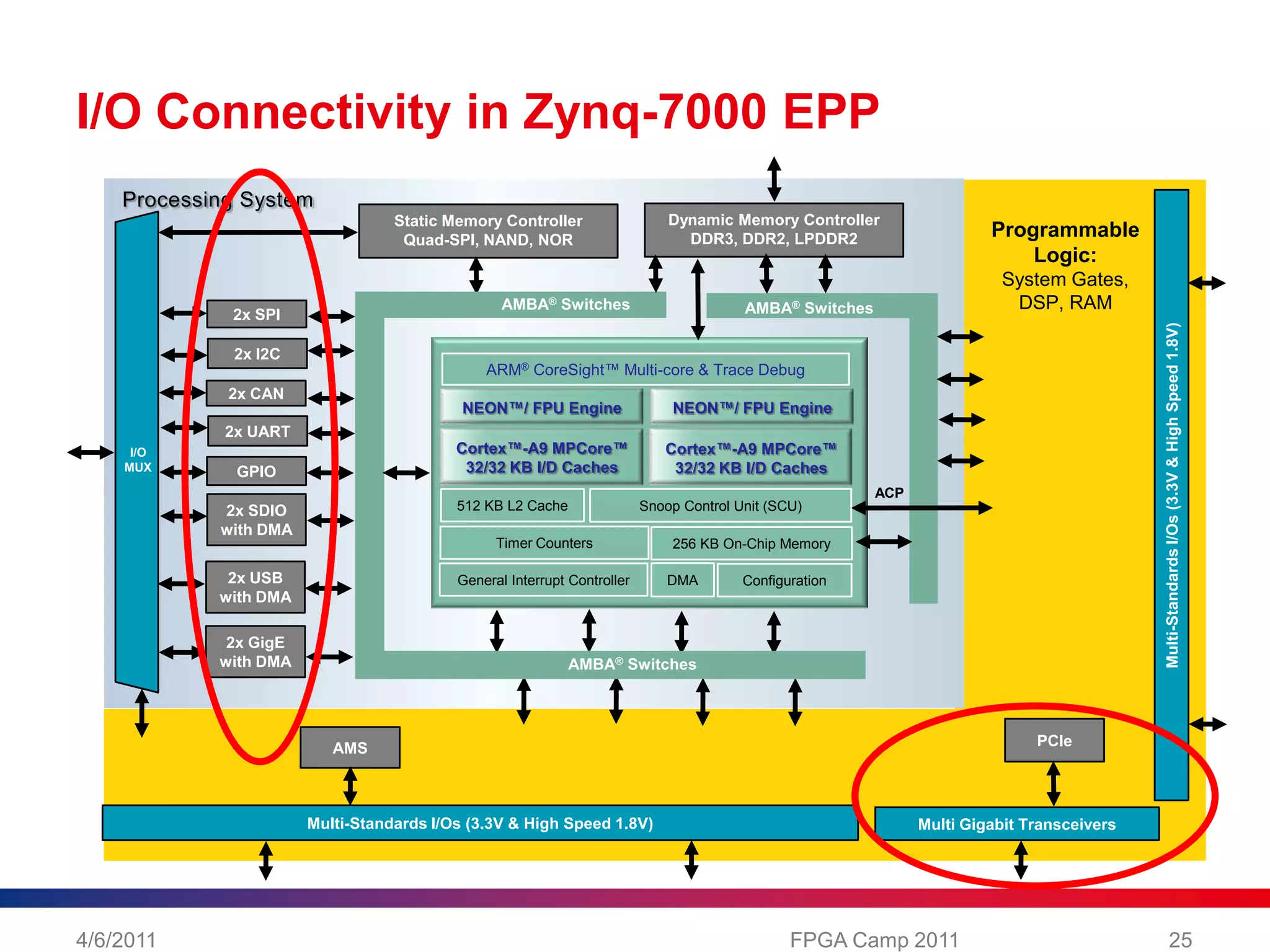

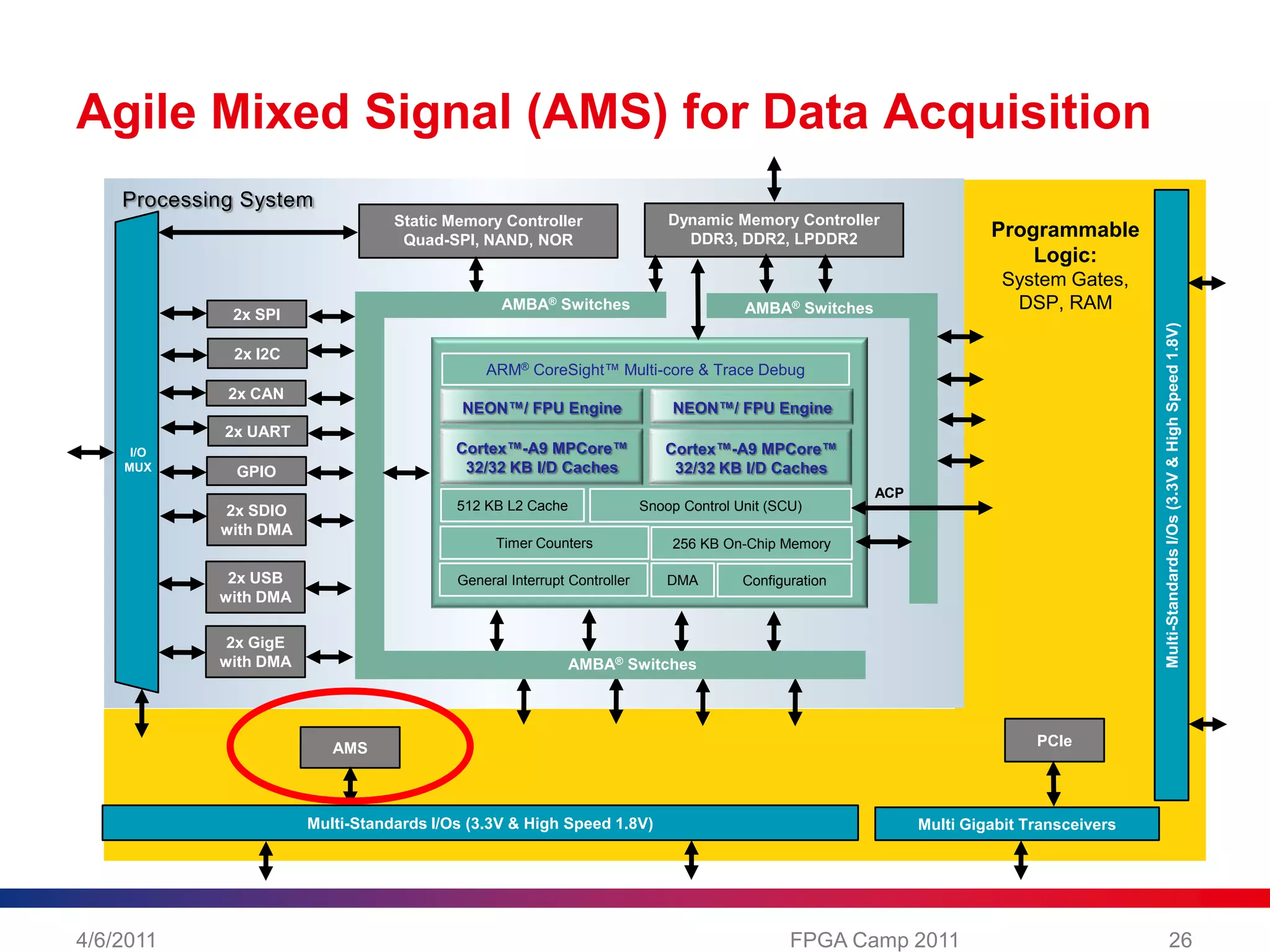

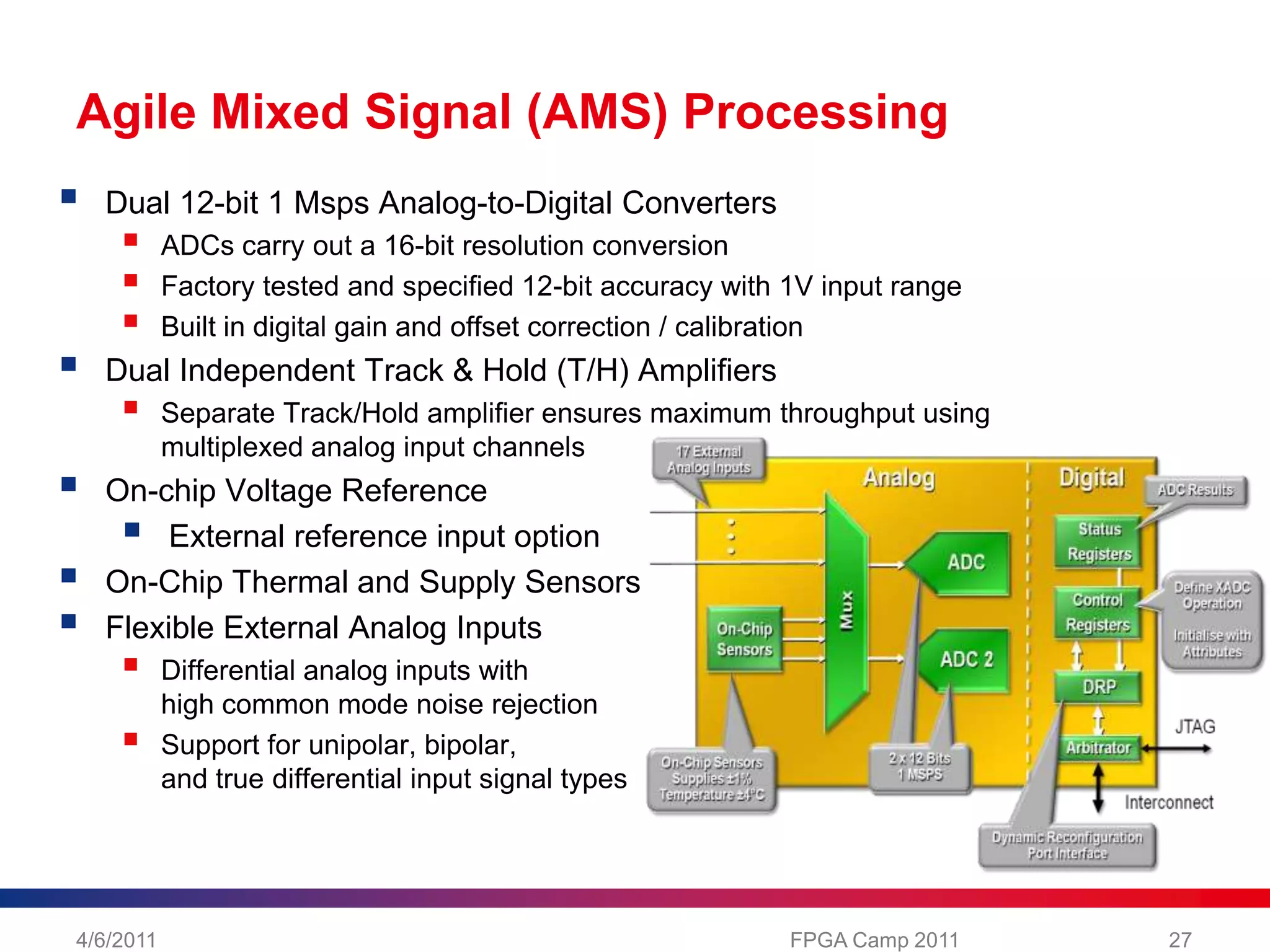

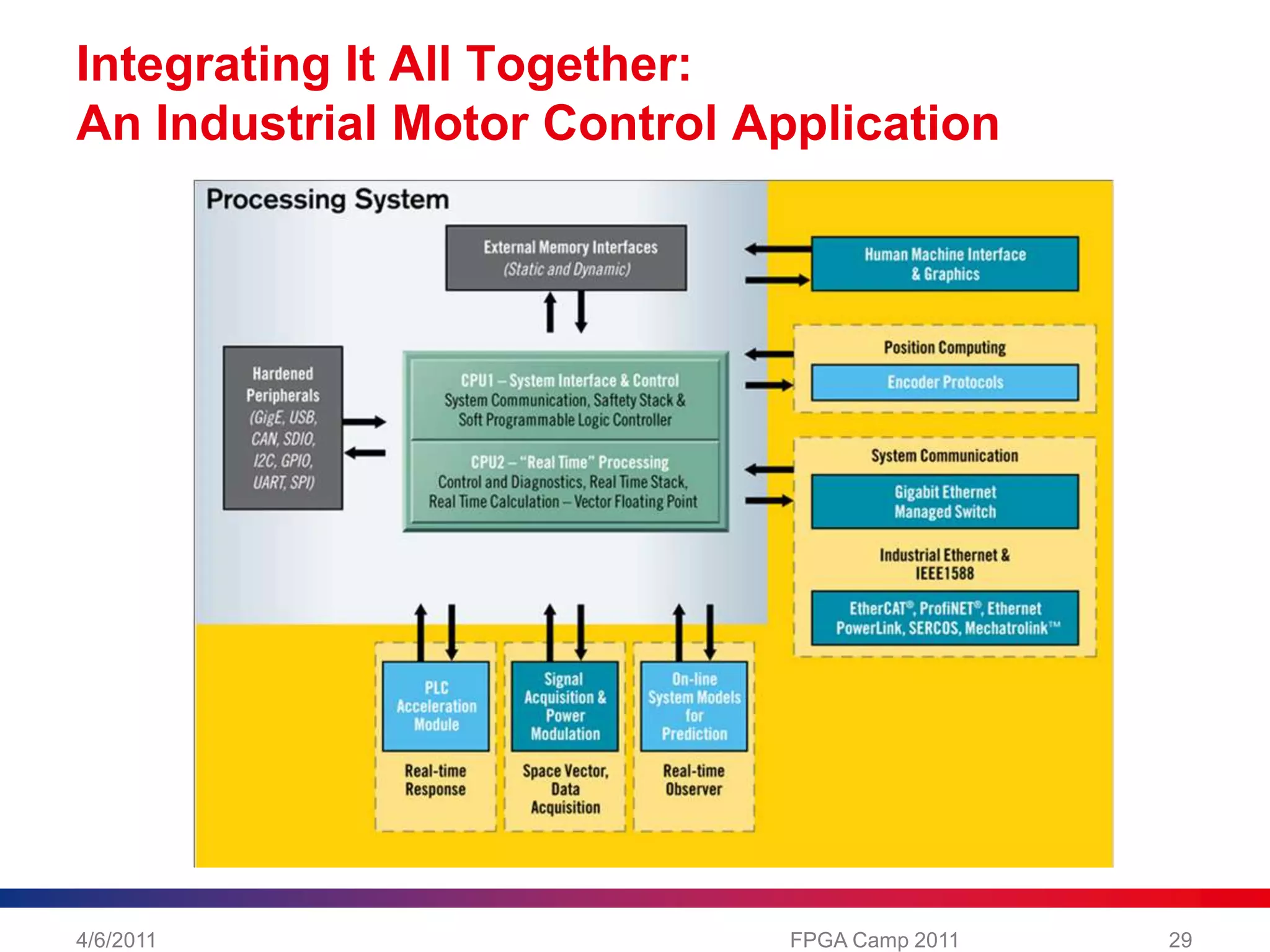

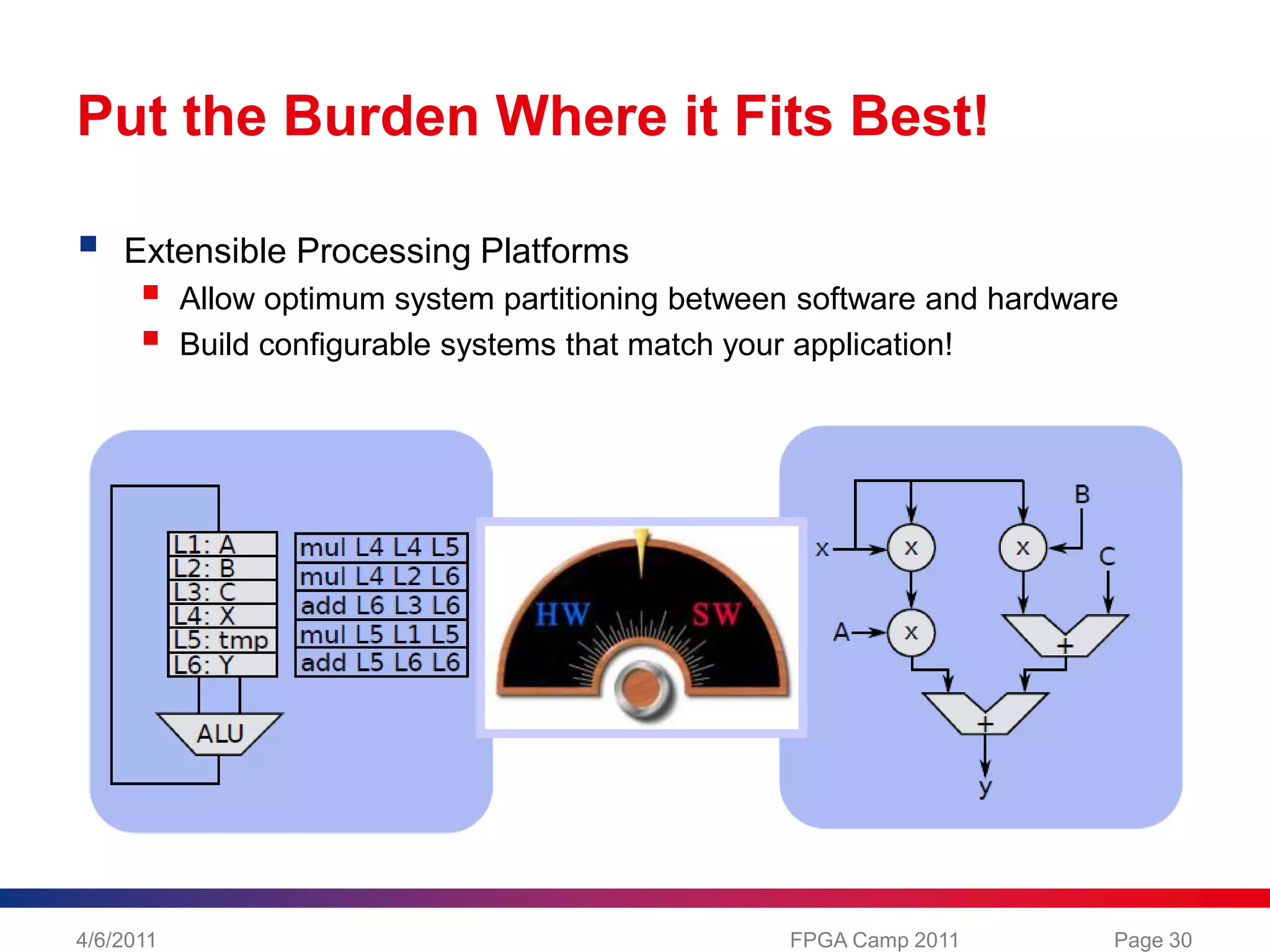

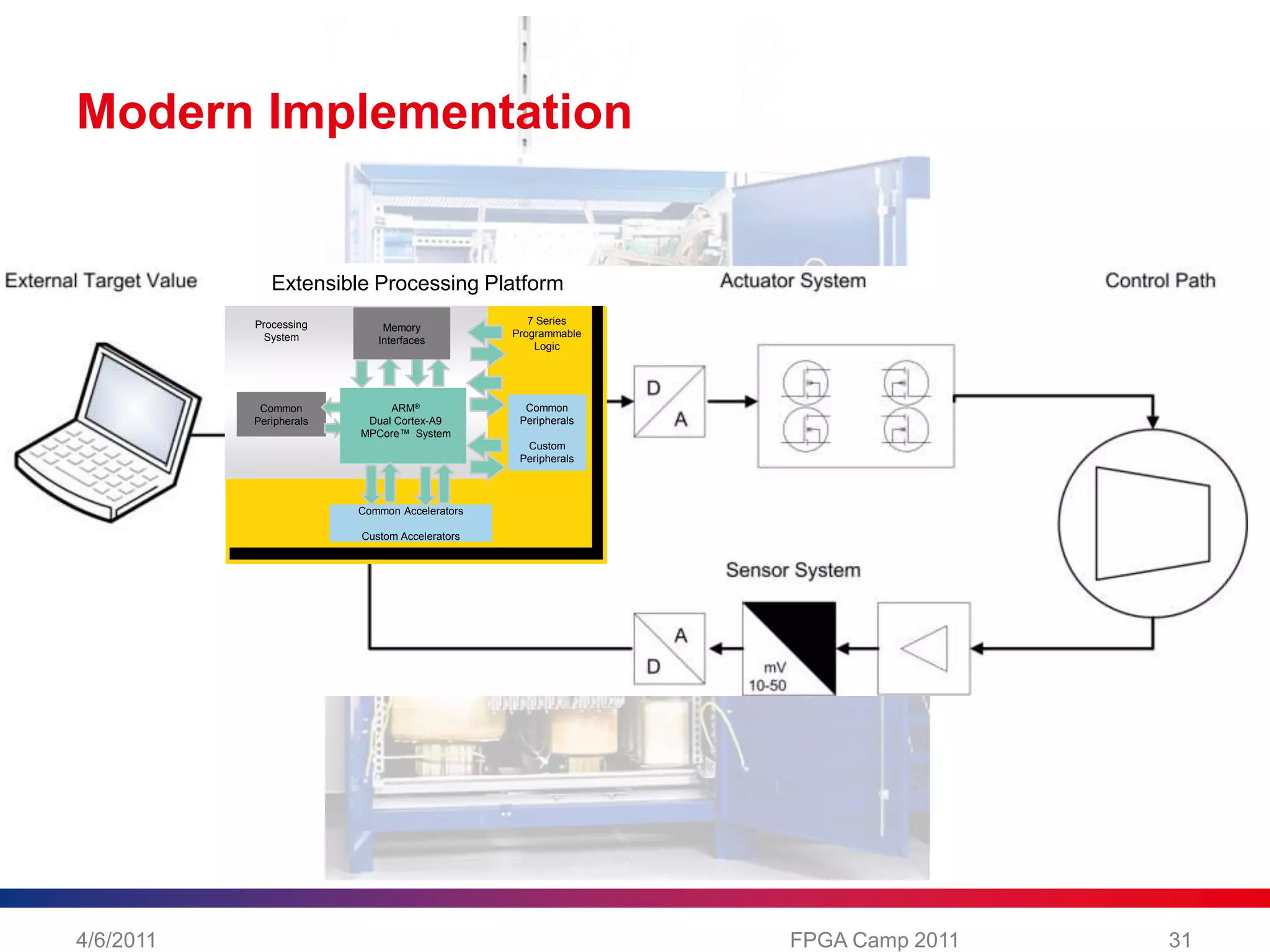

The document discusses design choices for embedded real-time control systems using FPGA technology, highlighting the evolution from hardware-centric to software-centric design flows. It covers issues such as I/O connectivity, parallel processing, and the integration of processing solutions like the Zynq-7000 extensible processing platform. Additionally, it addresses challenges related to scalability, reliability, and system partitioning in control applications.