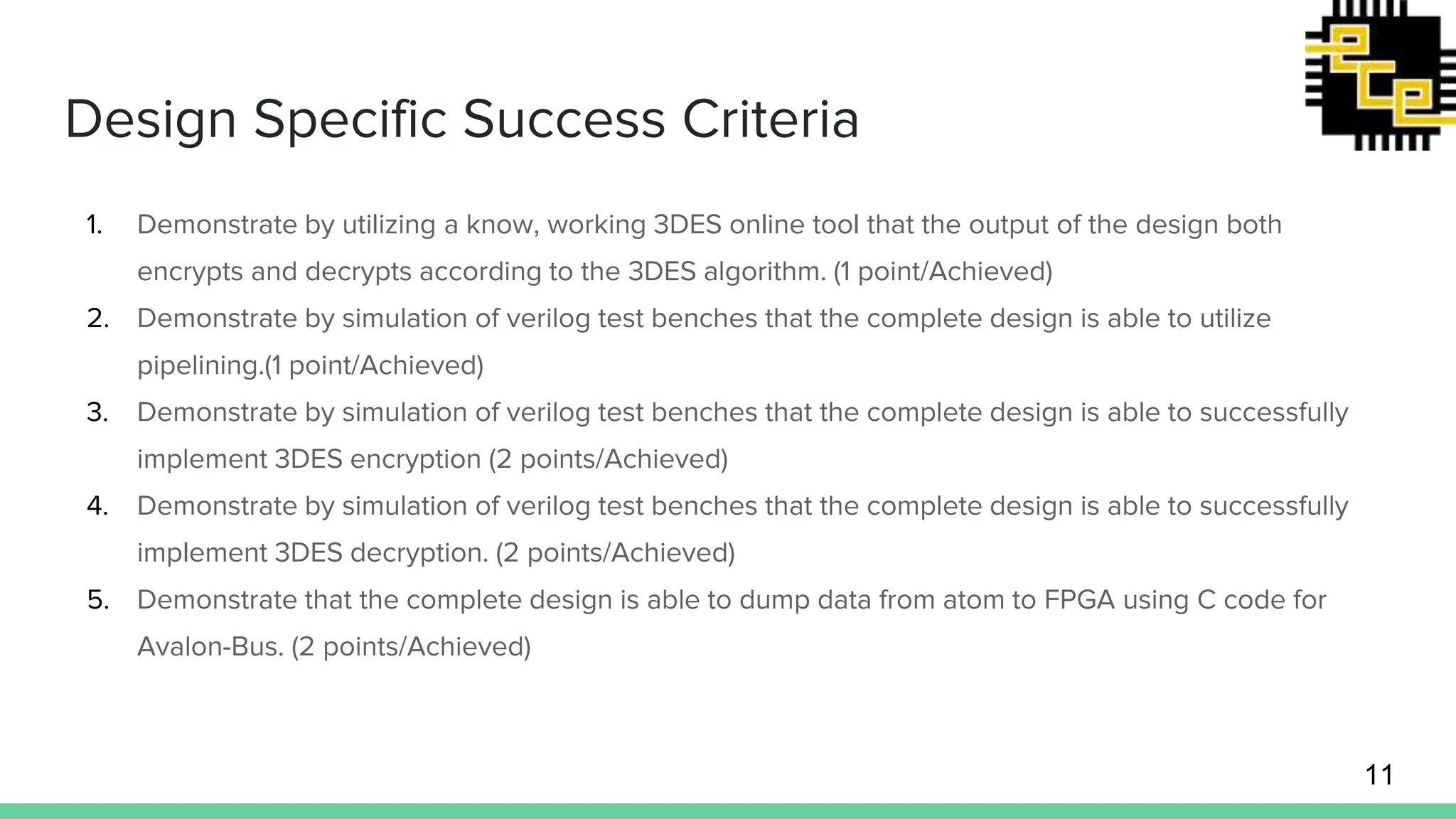

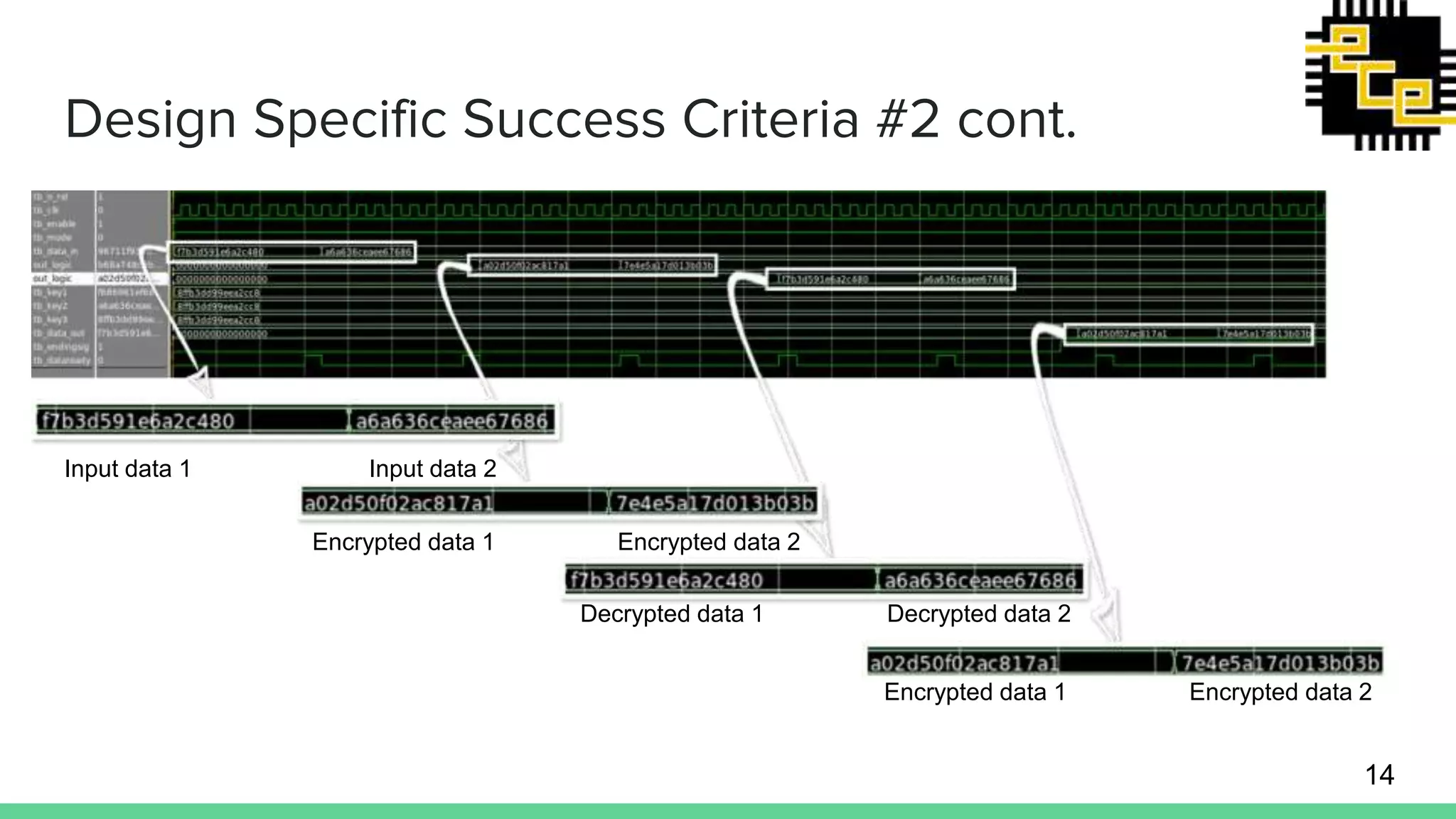

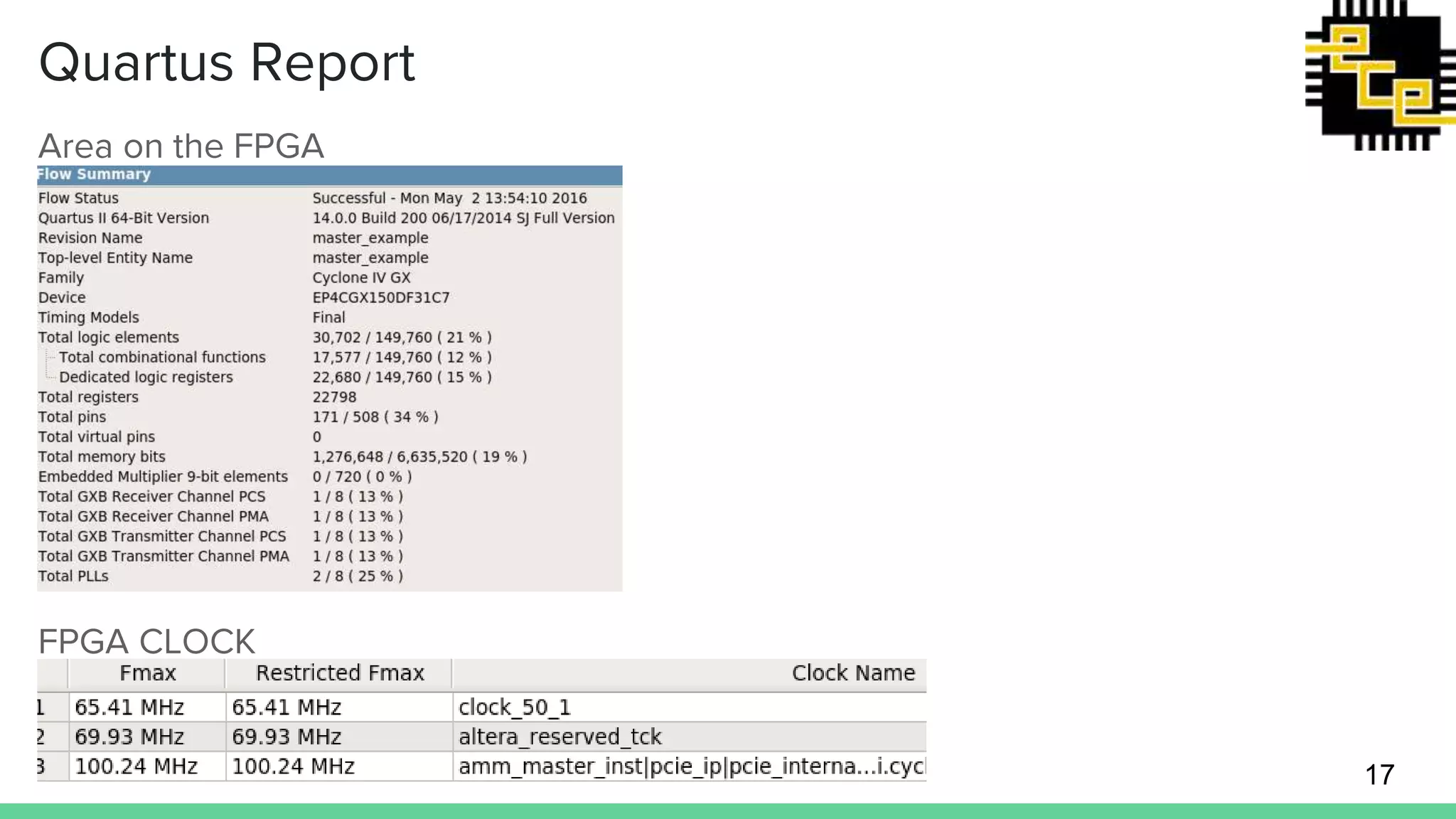

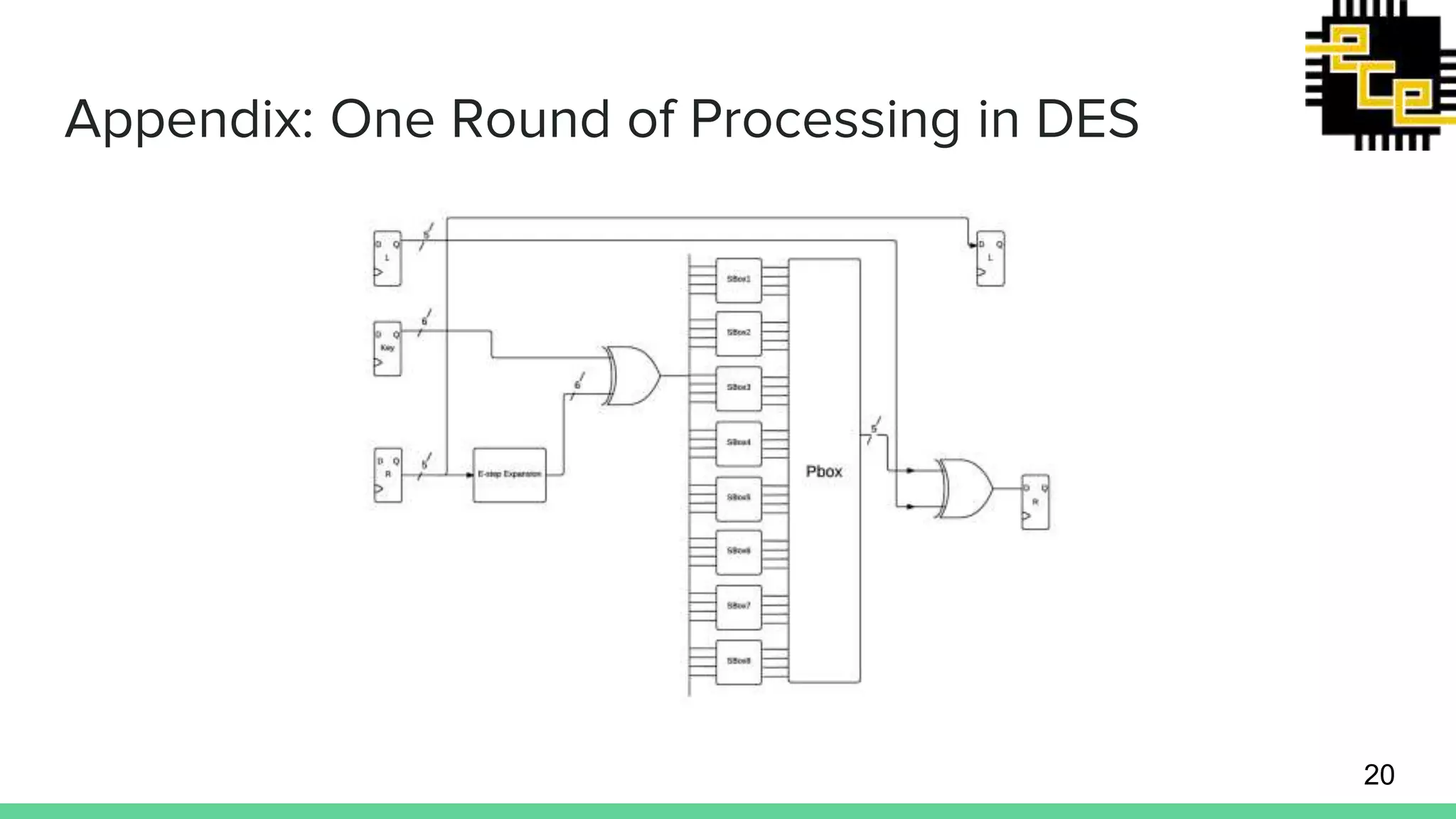

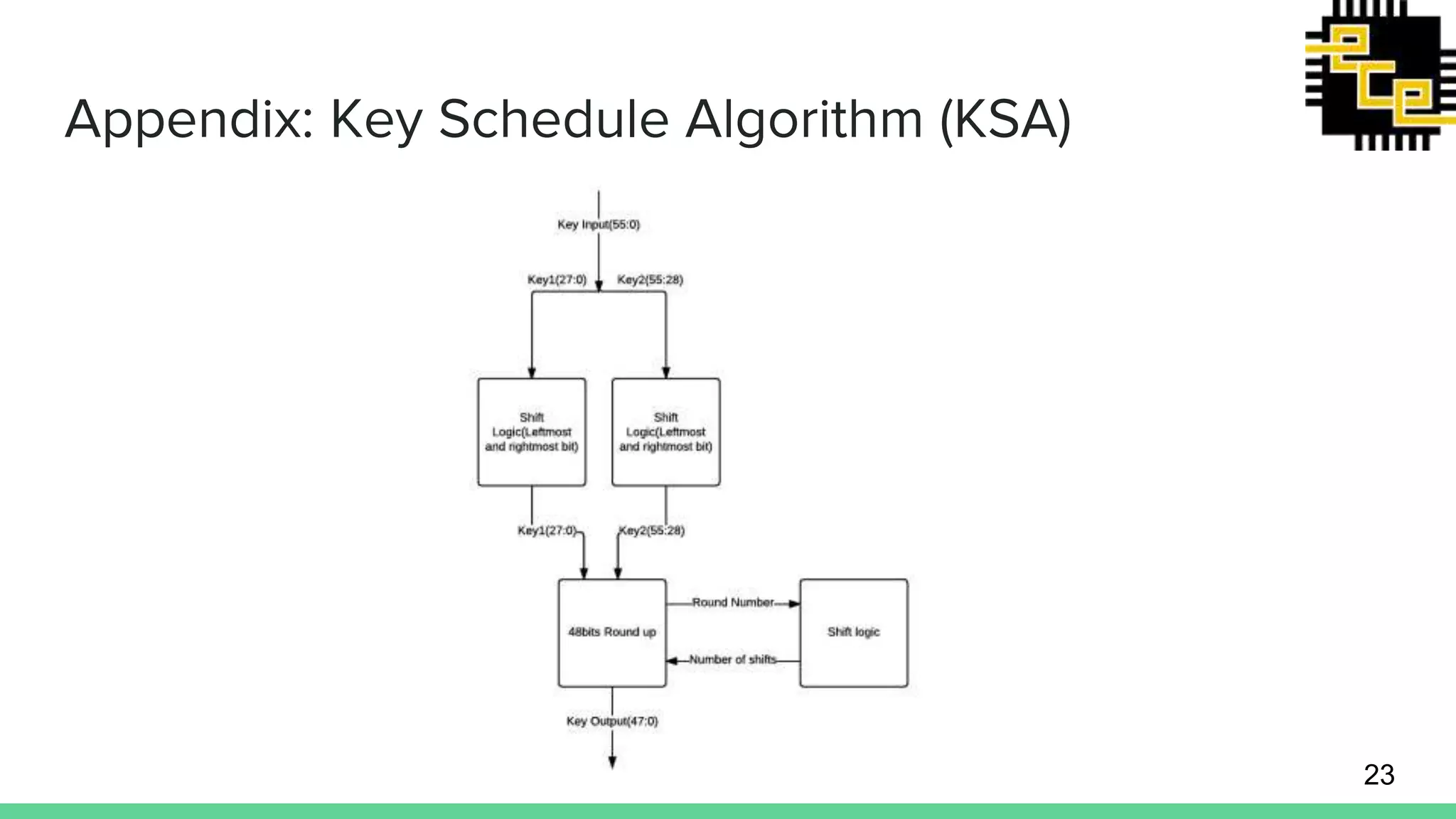

The document outlines the design and implementation of a Triple DES (3DES) encryption system by a team consisting of Junjie Wang, Xiao Xiao, Zhuofan Li, and Ming Huen Lee. It covers the algorithm's operation, system architecture, success criteria for design validation, and details on pipelining and output requirements. Additionally, various design-specific success criteria are provided, along with challenges and improvements for enhanced security.