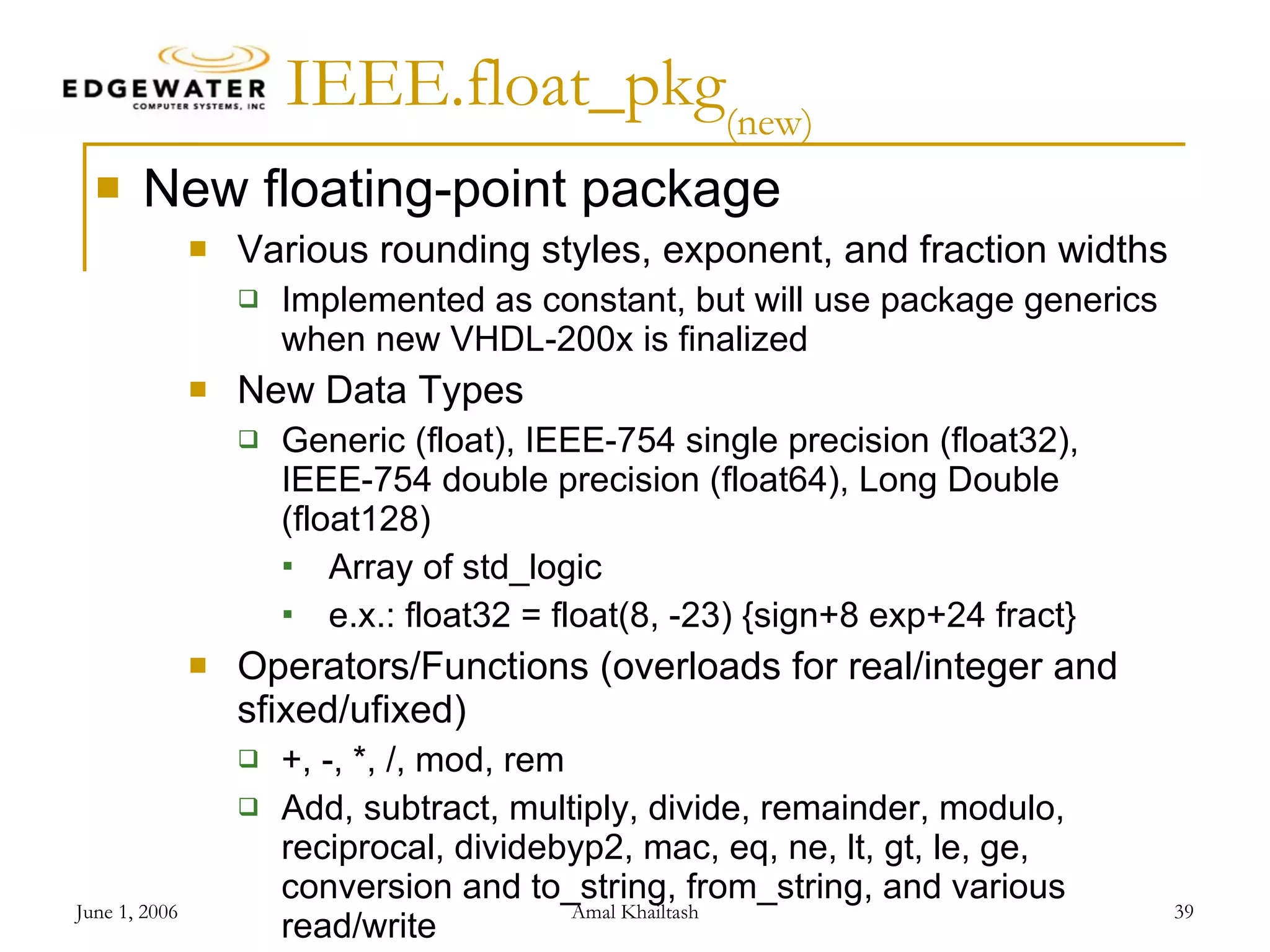

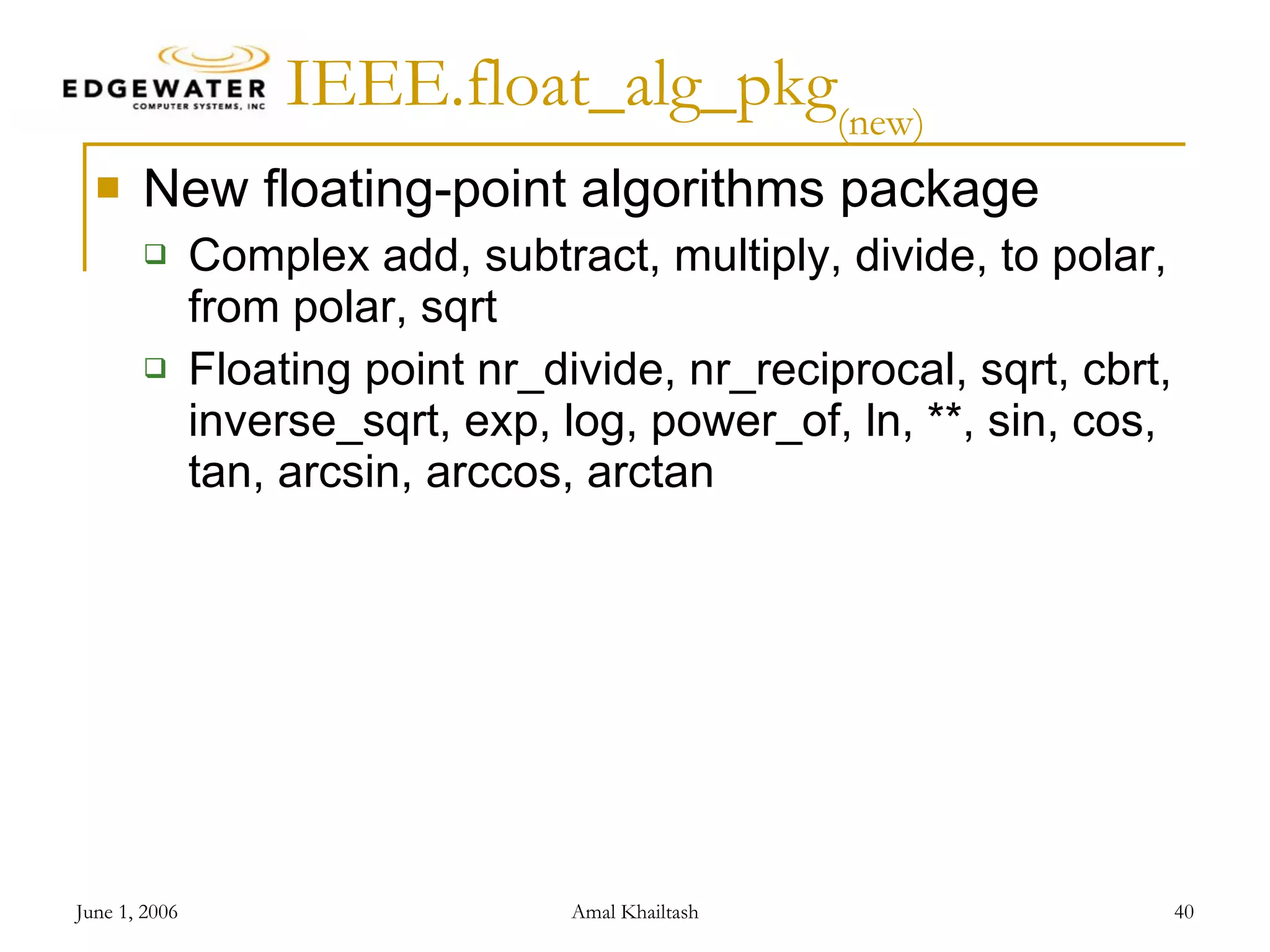

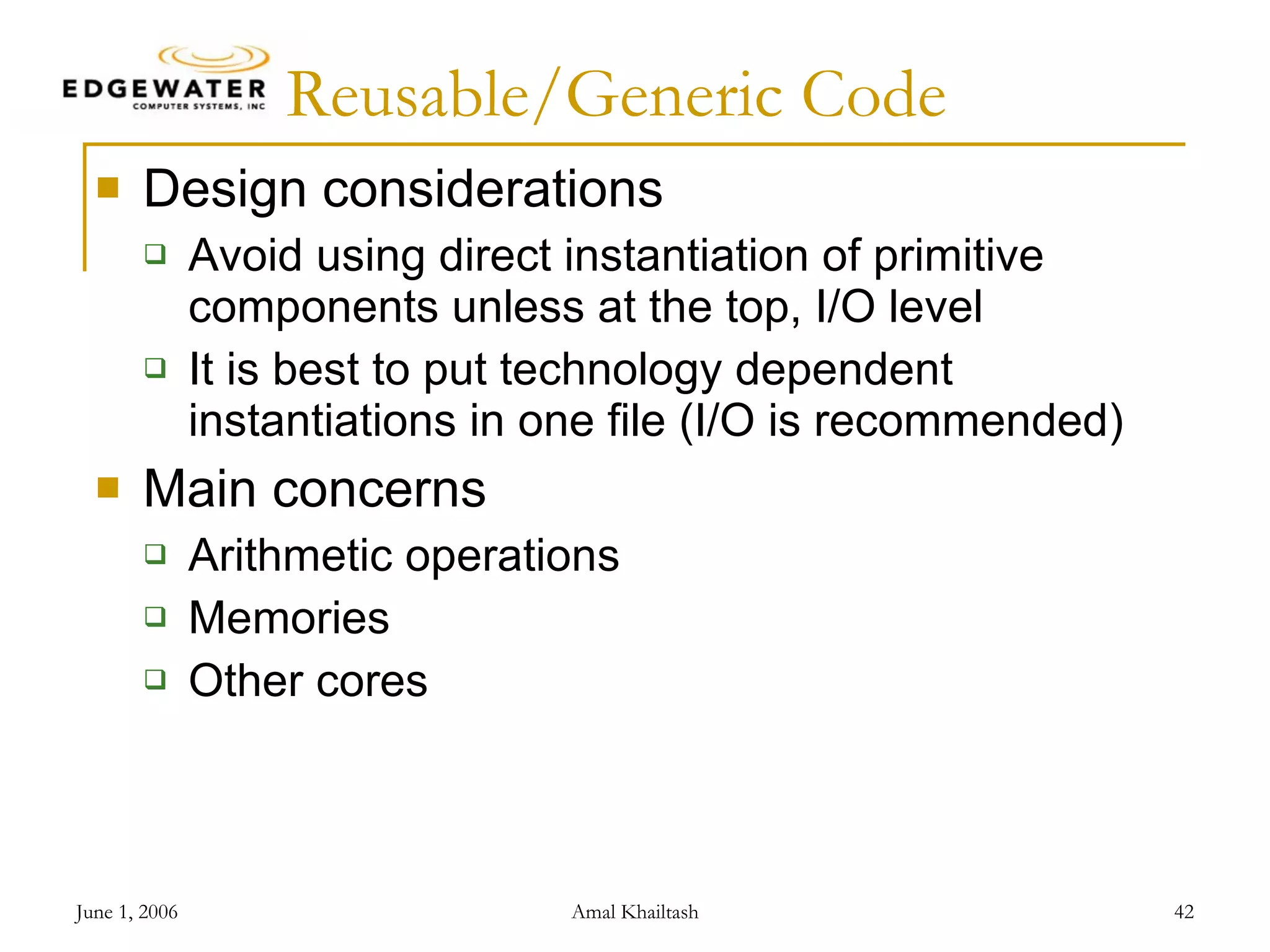

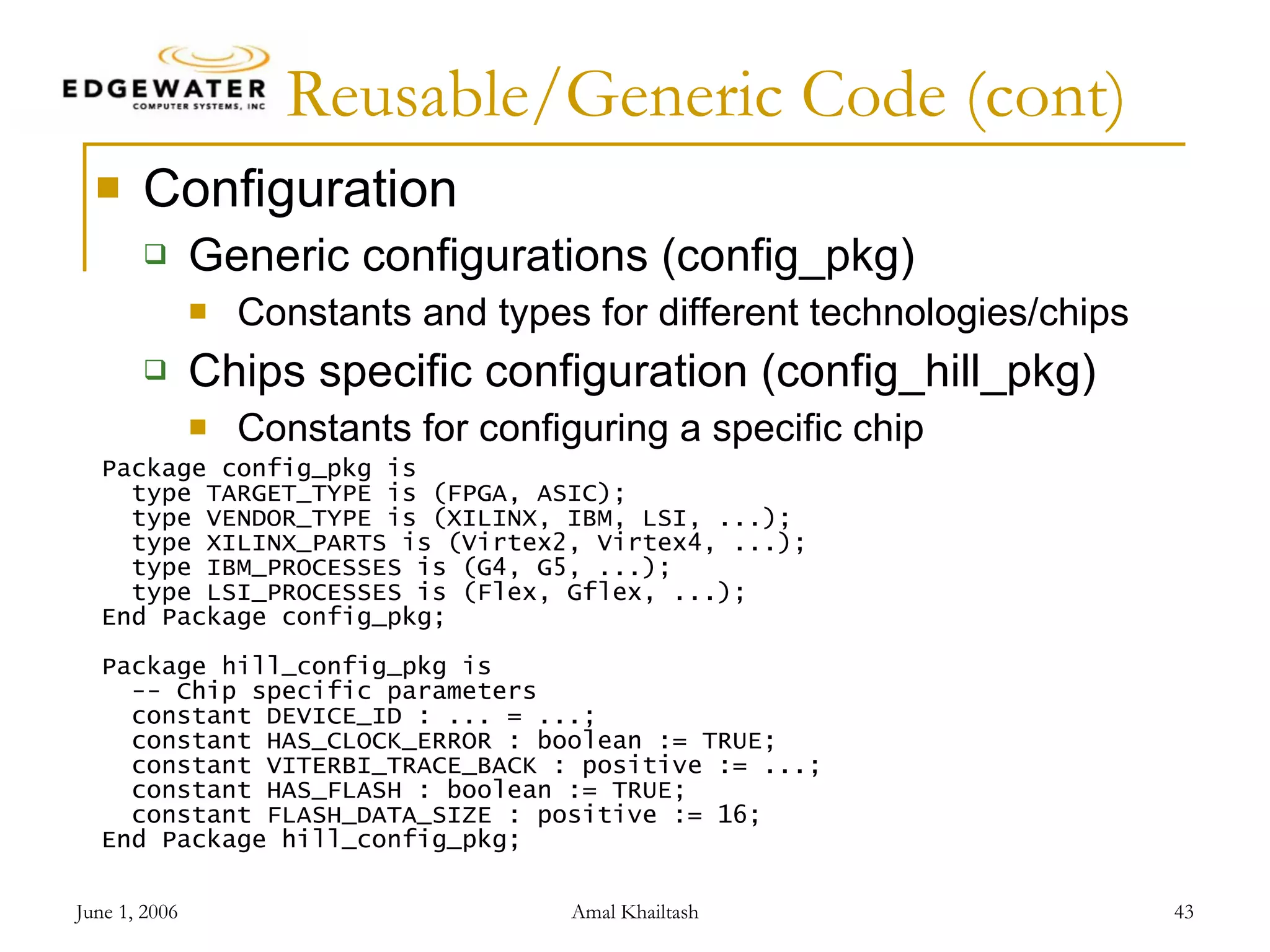

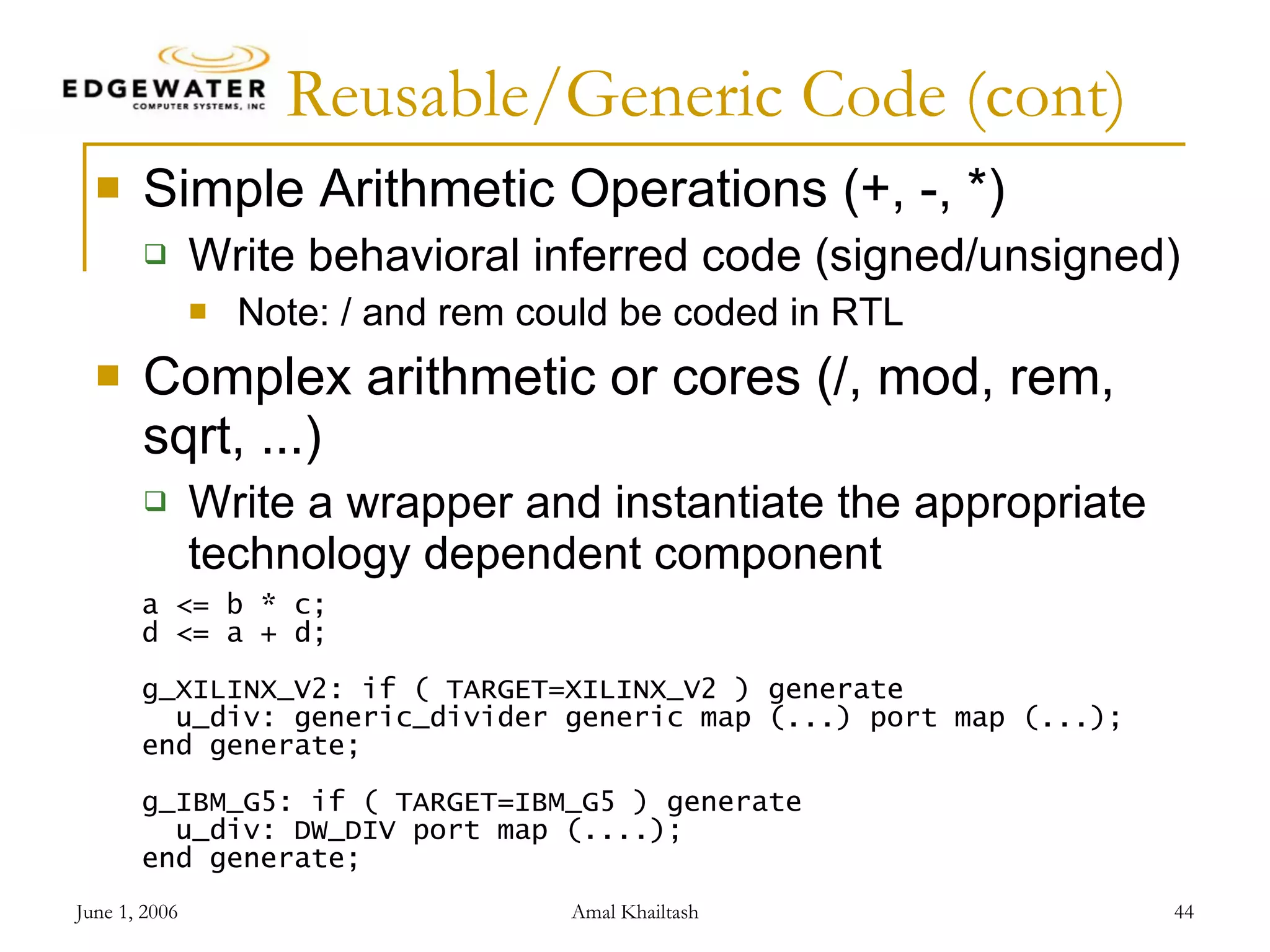

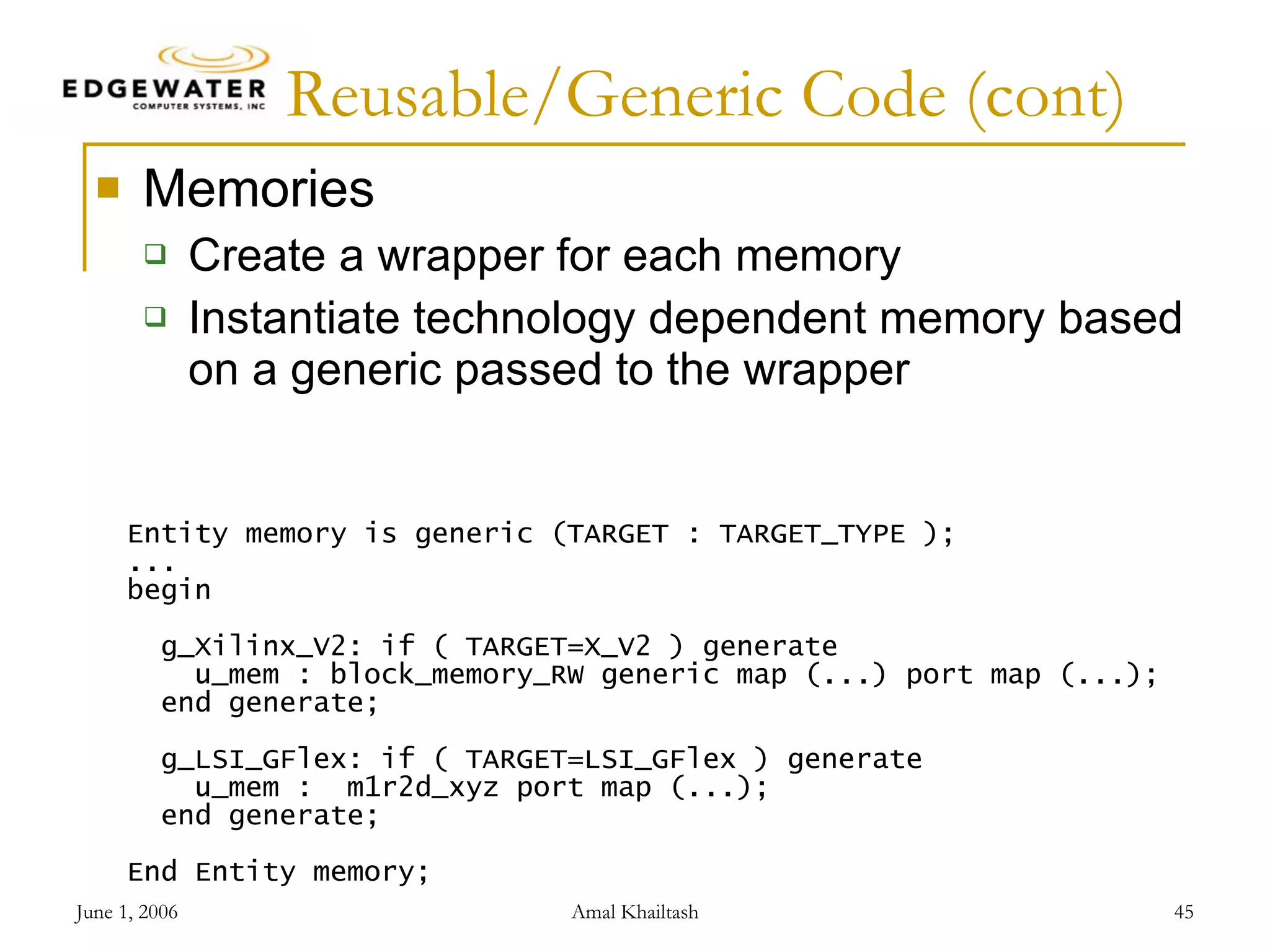

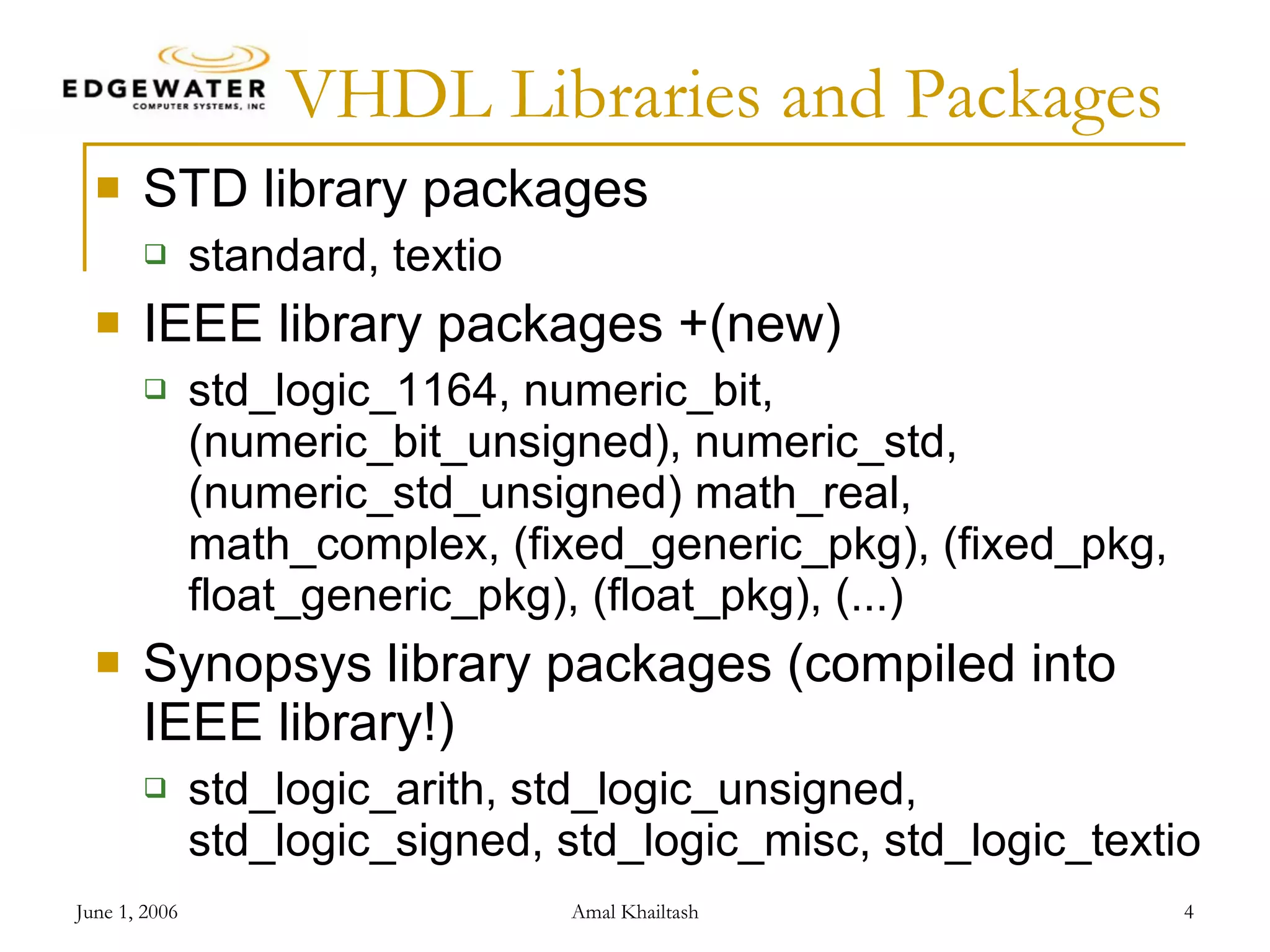

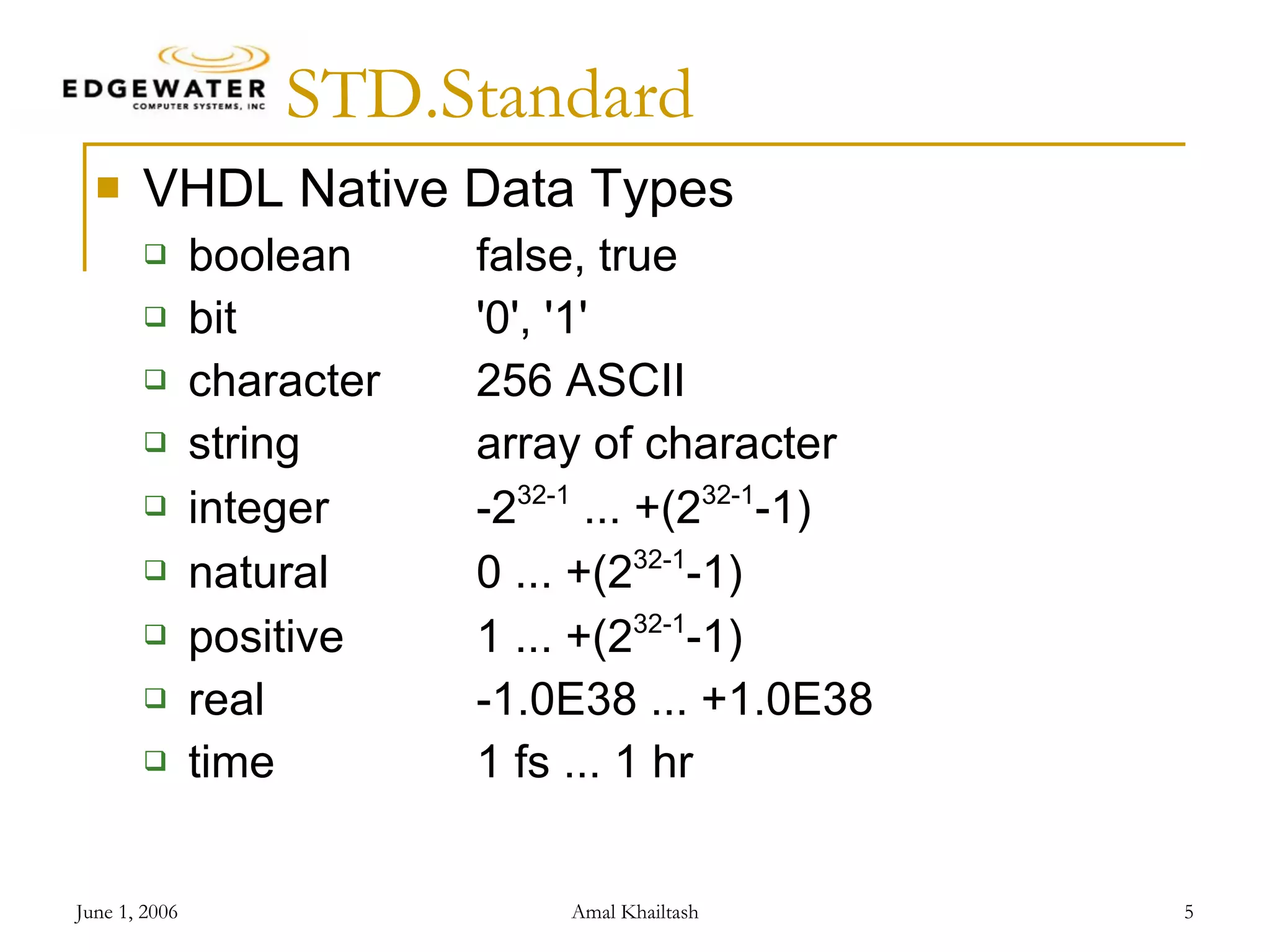

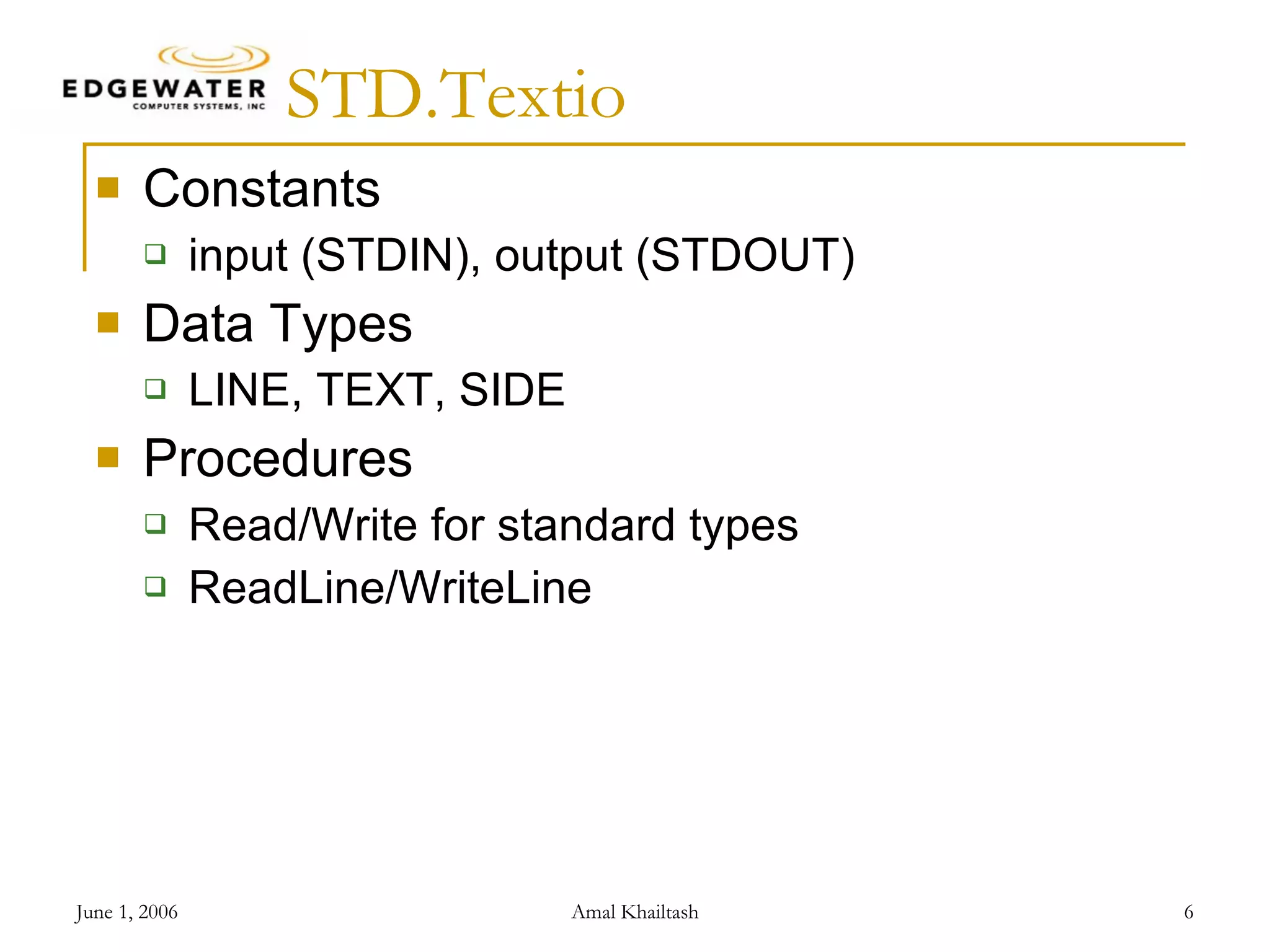

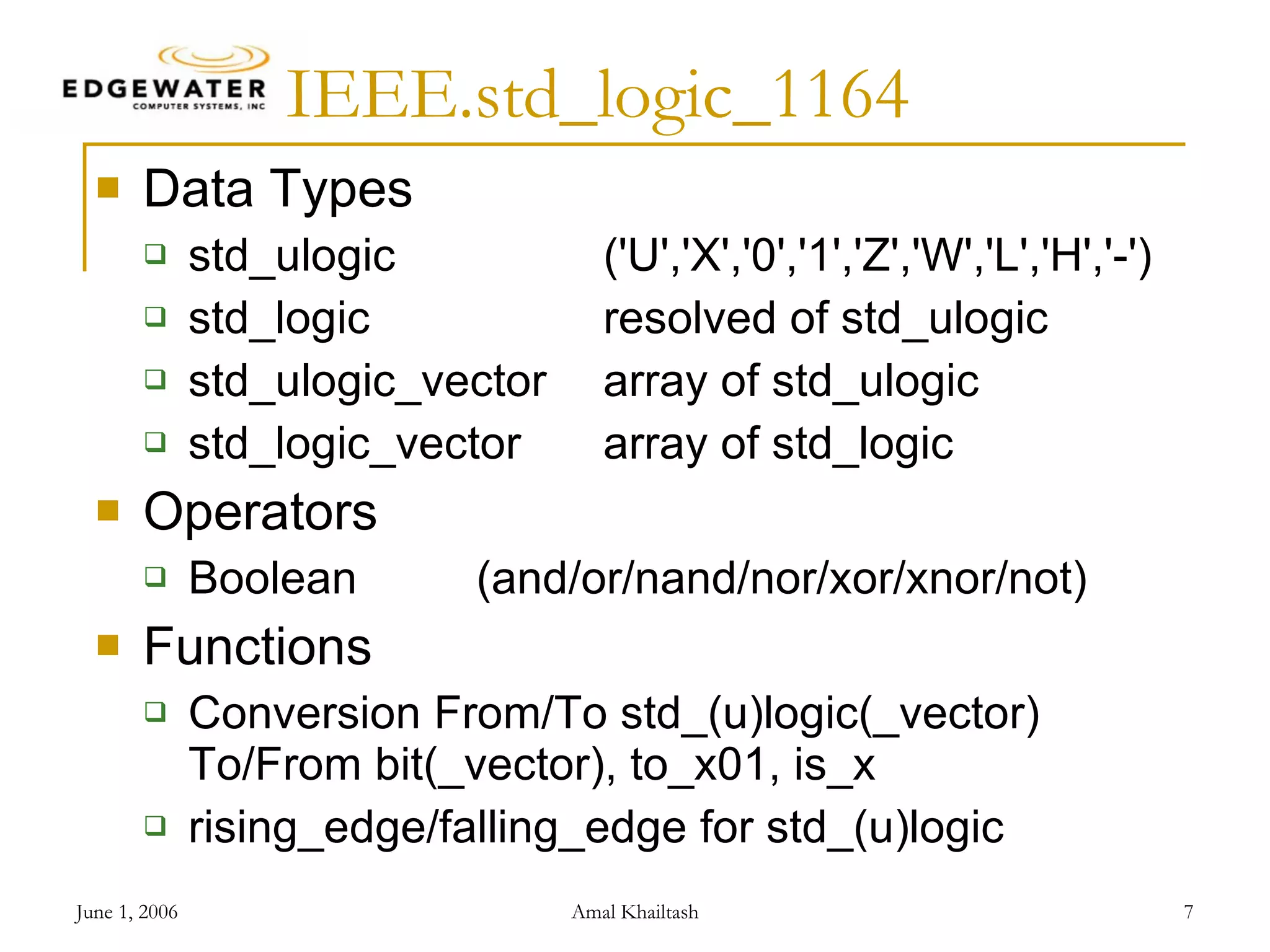

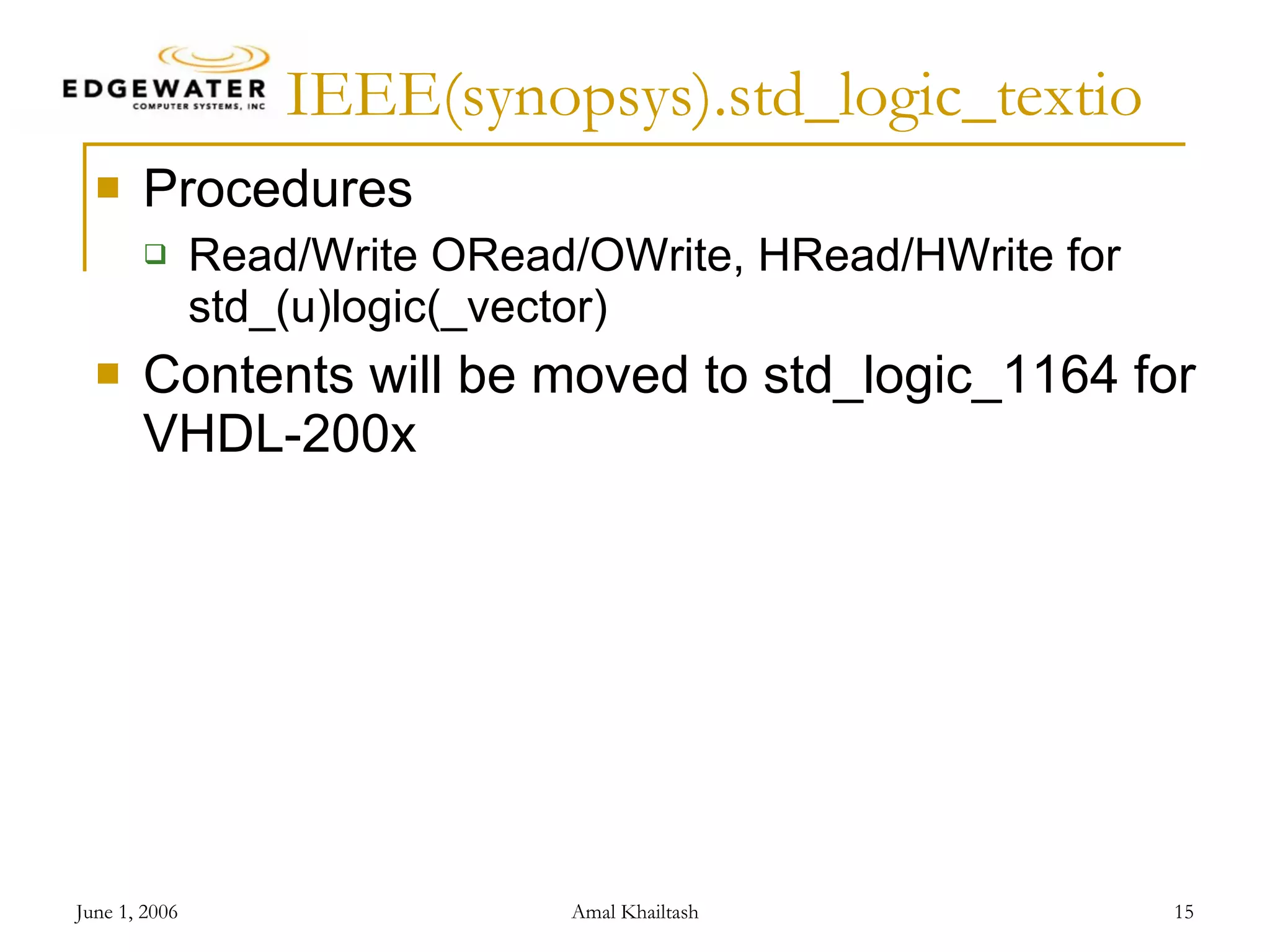

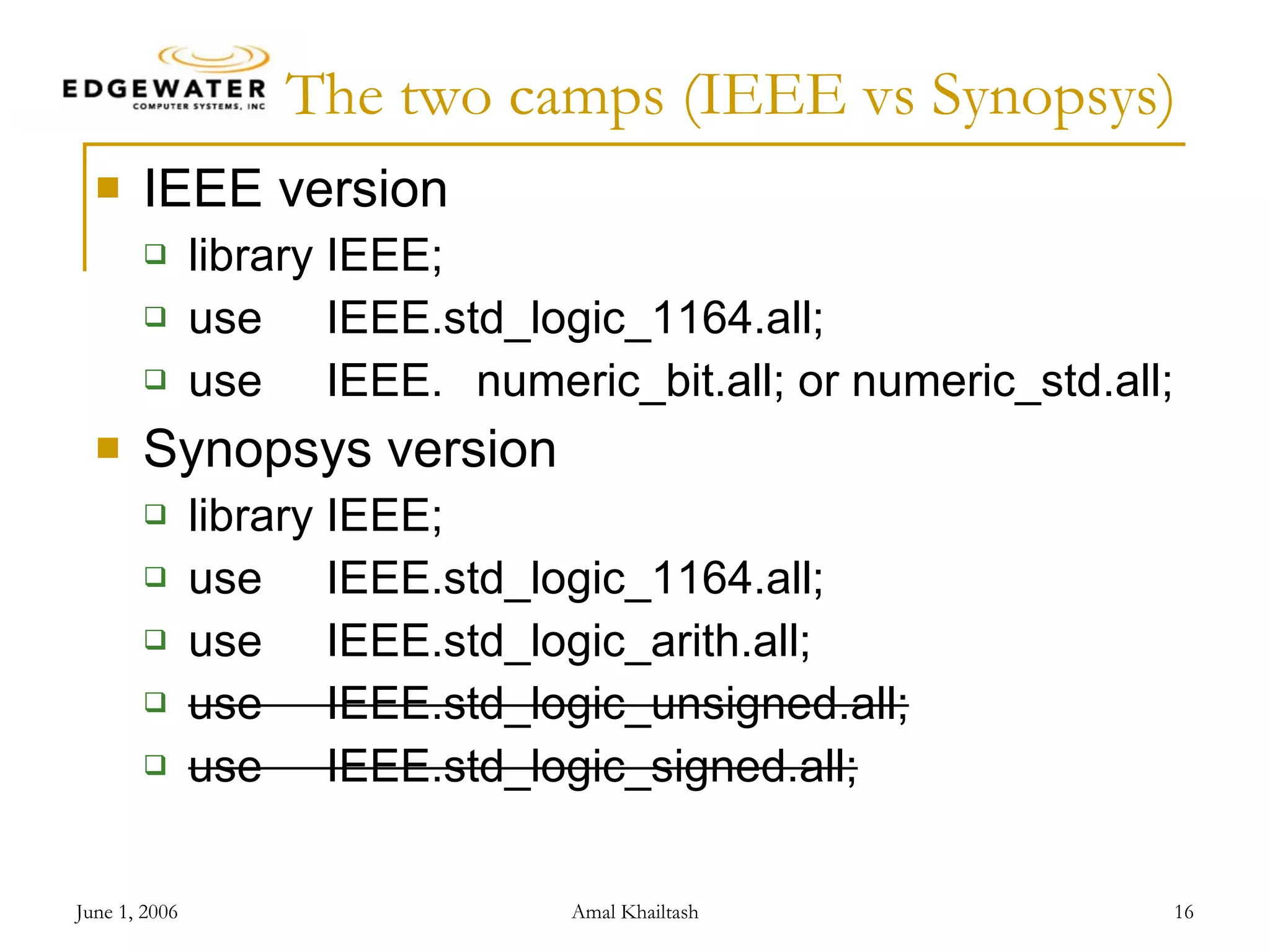

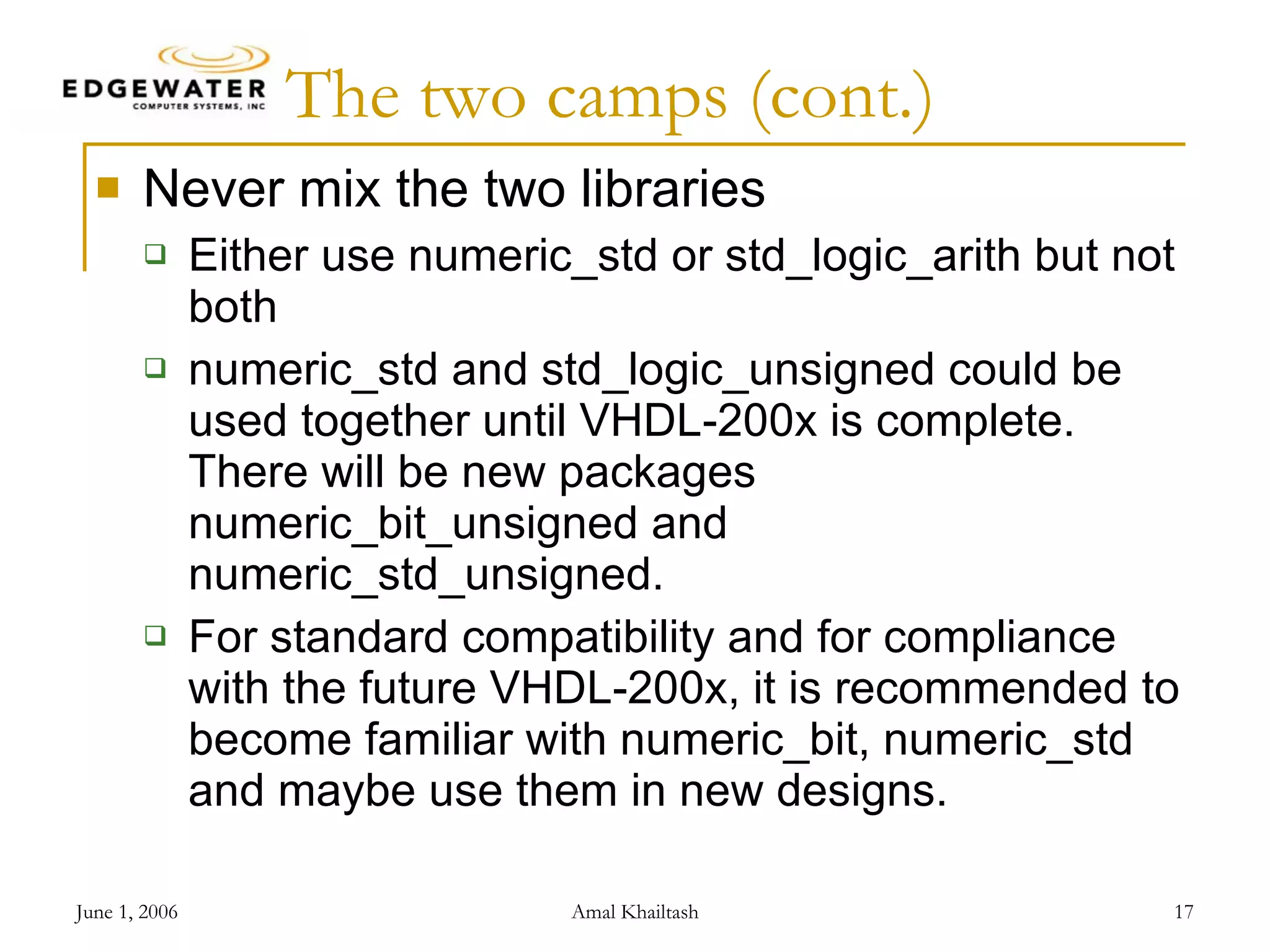

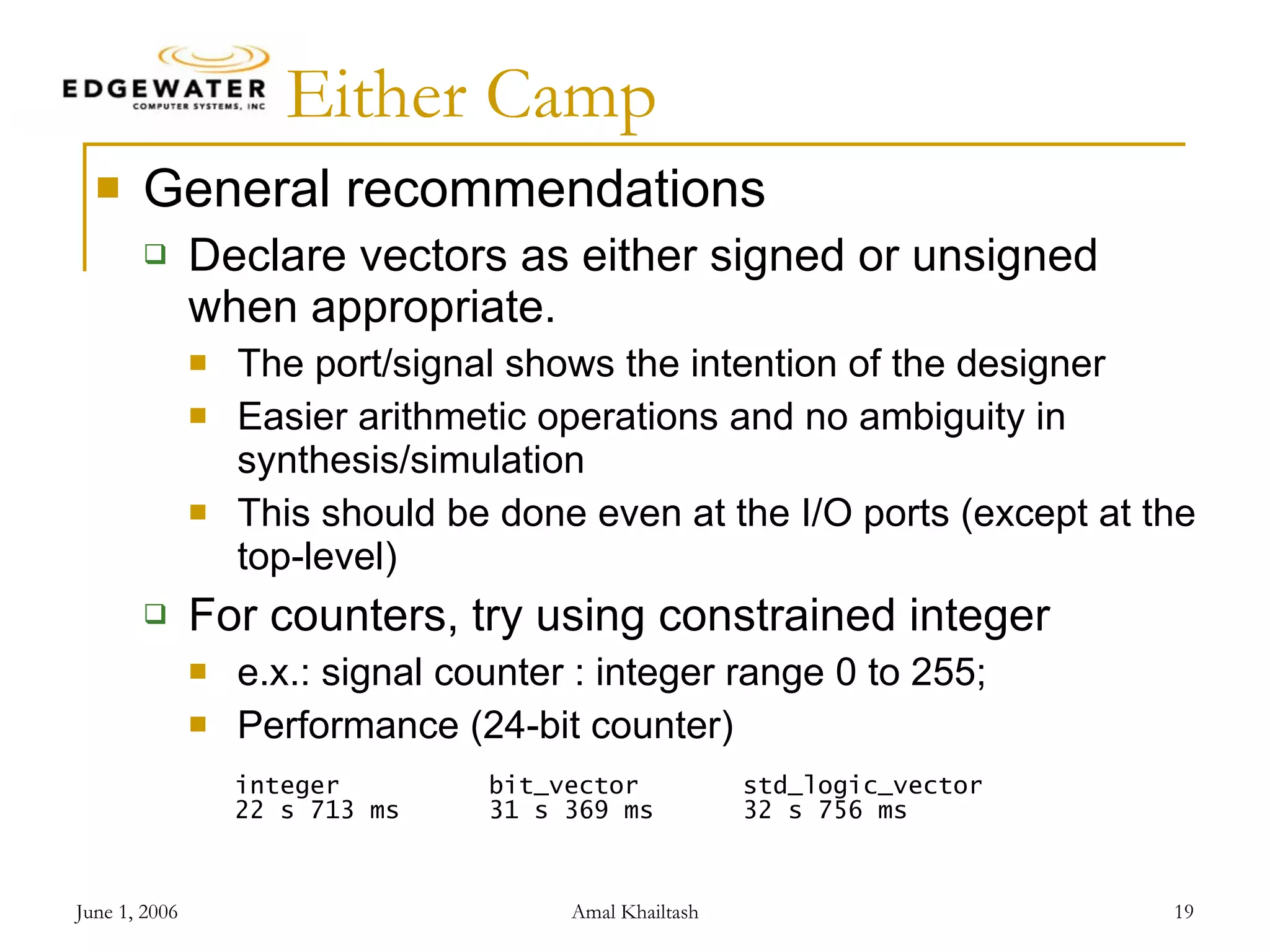

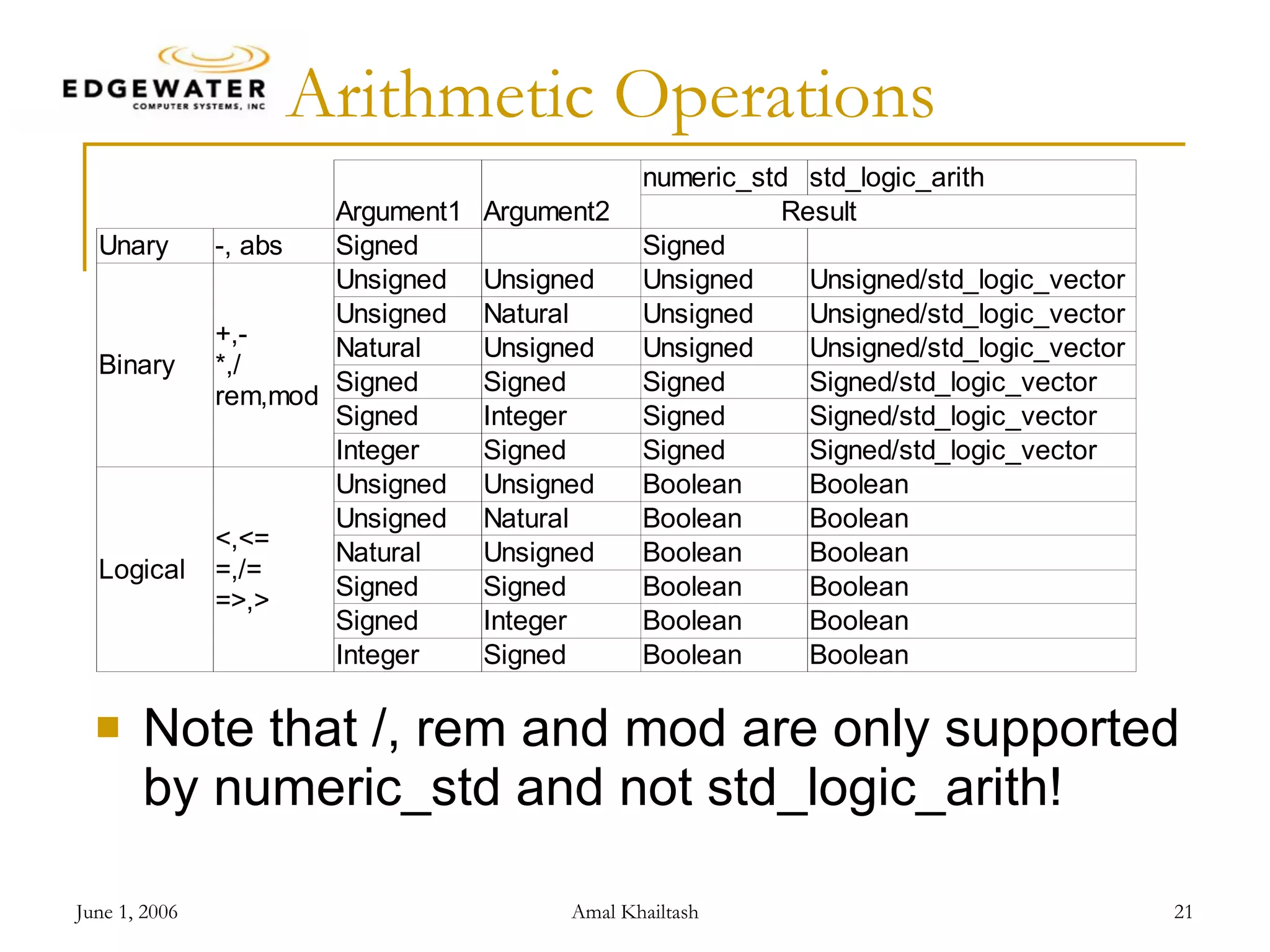

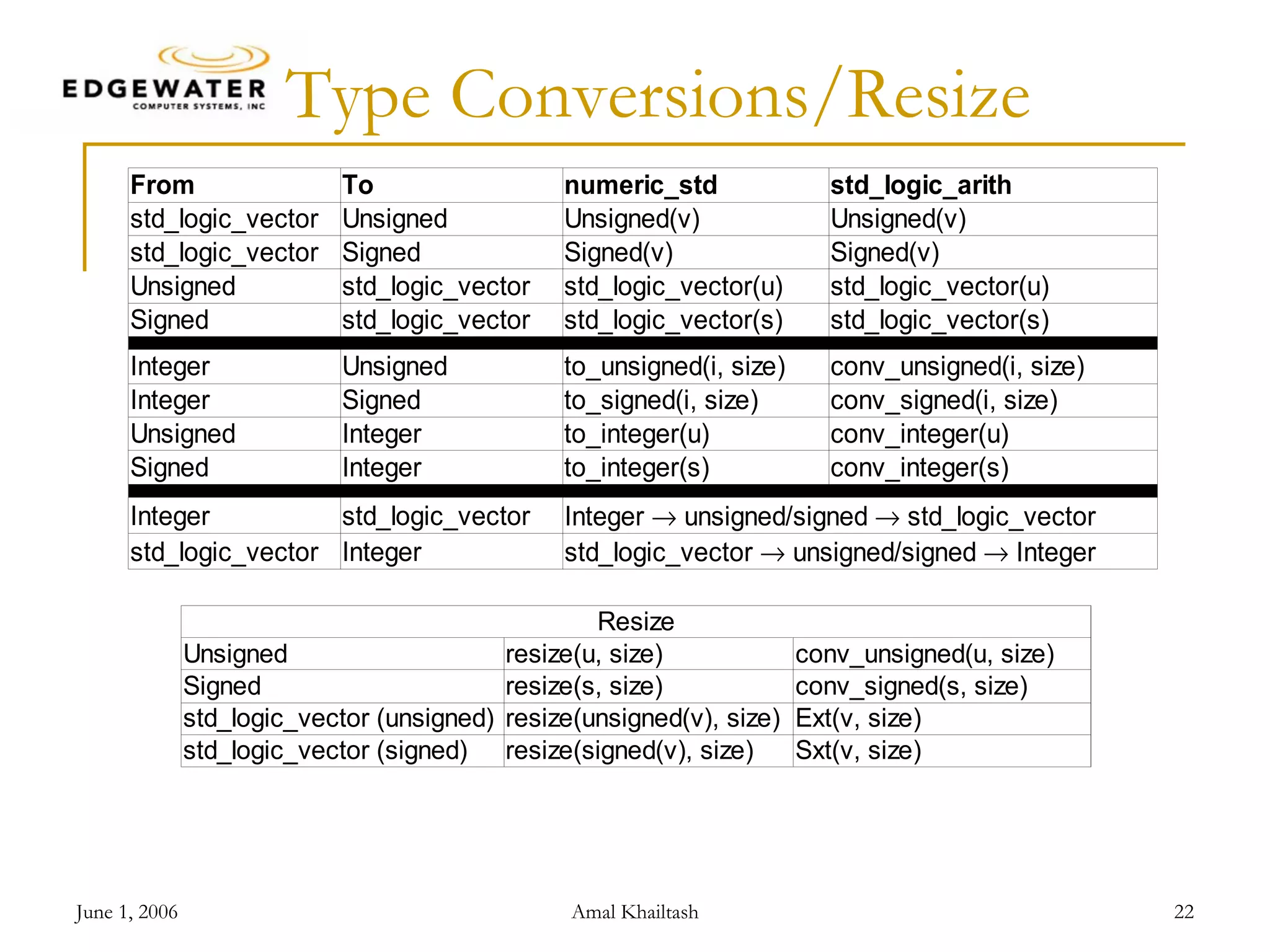

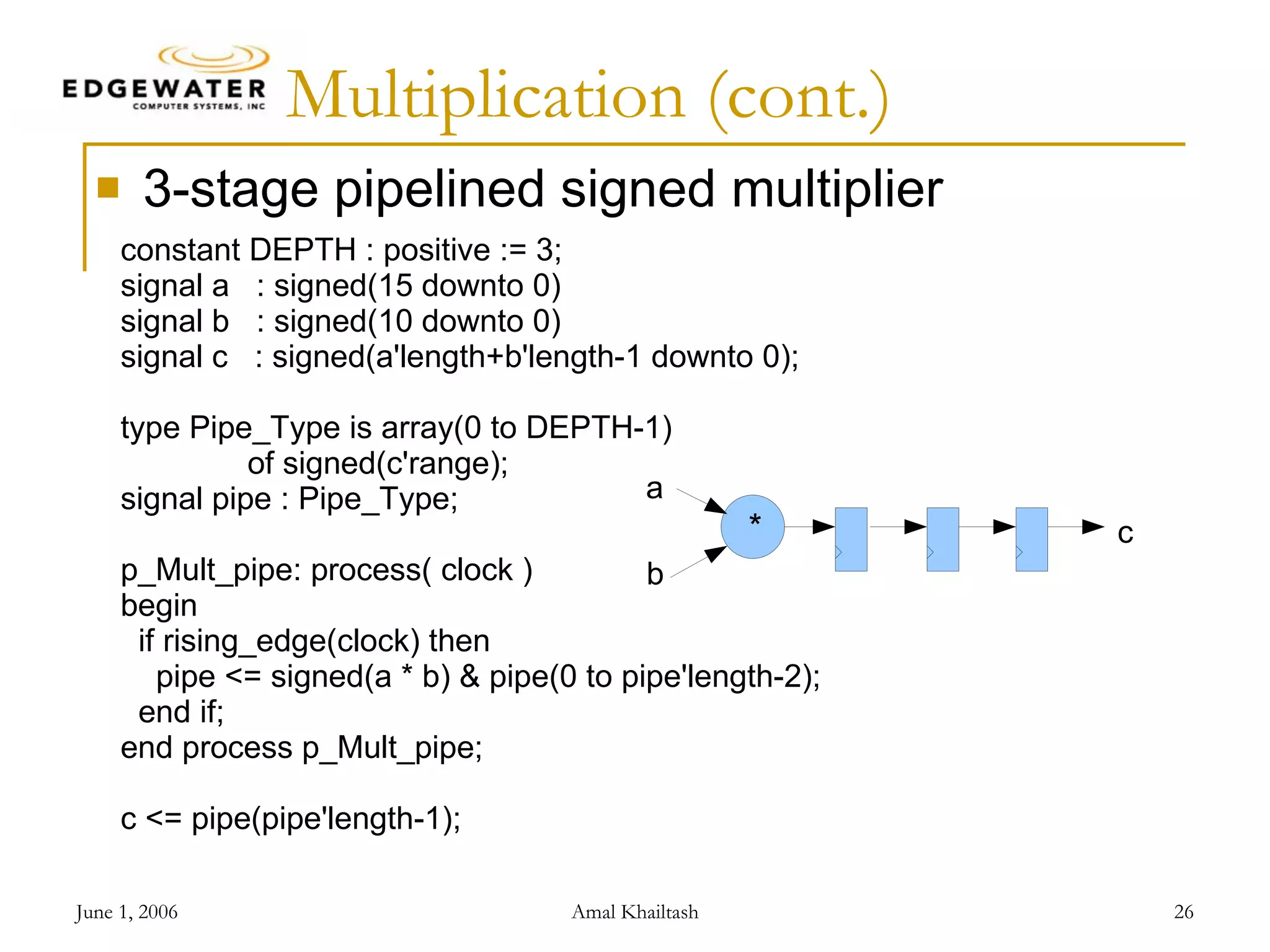

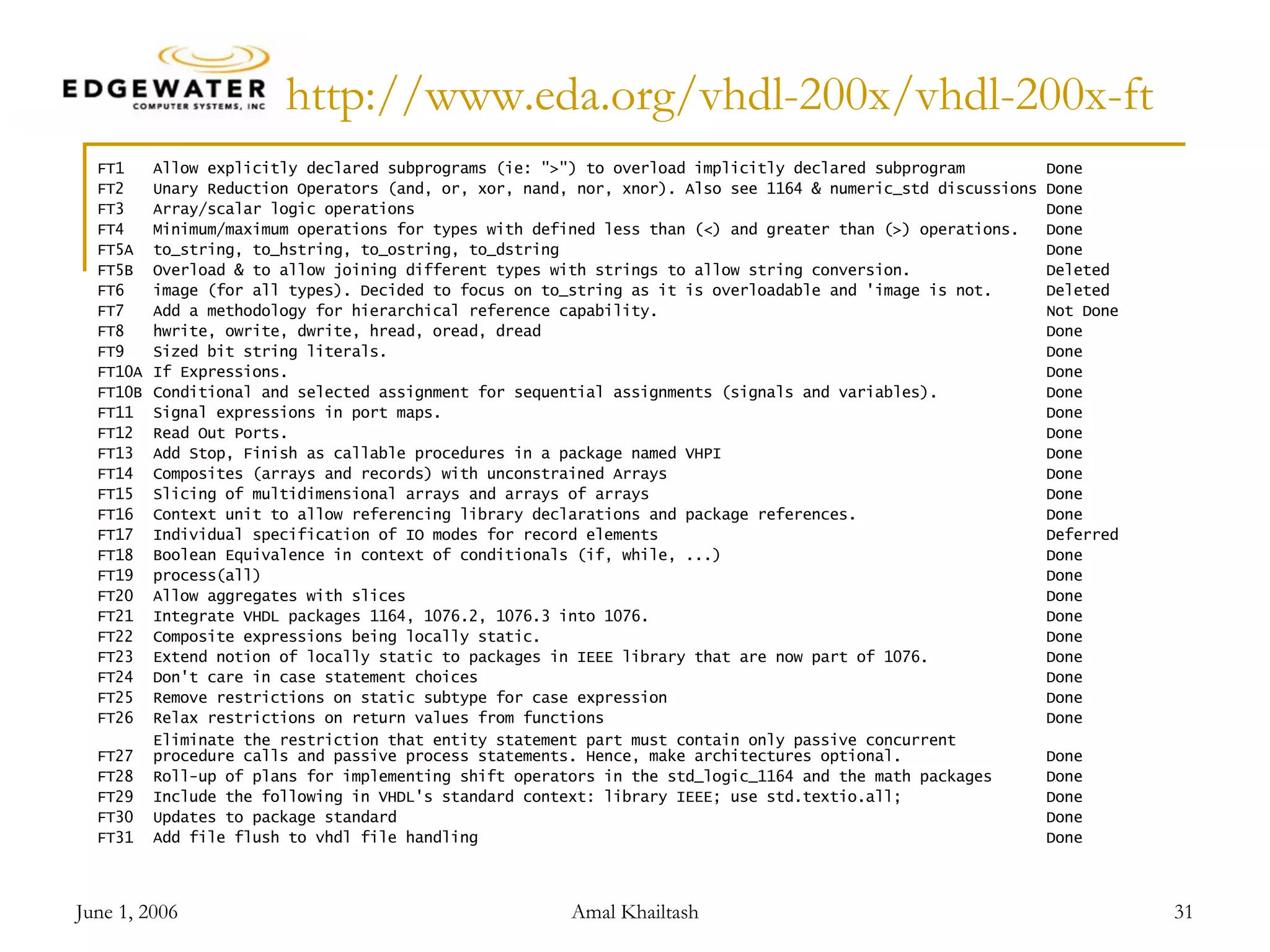

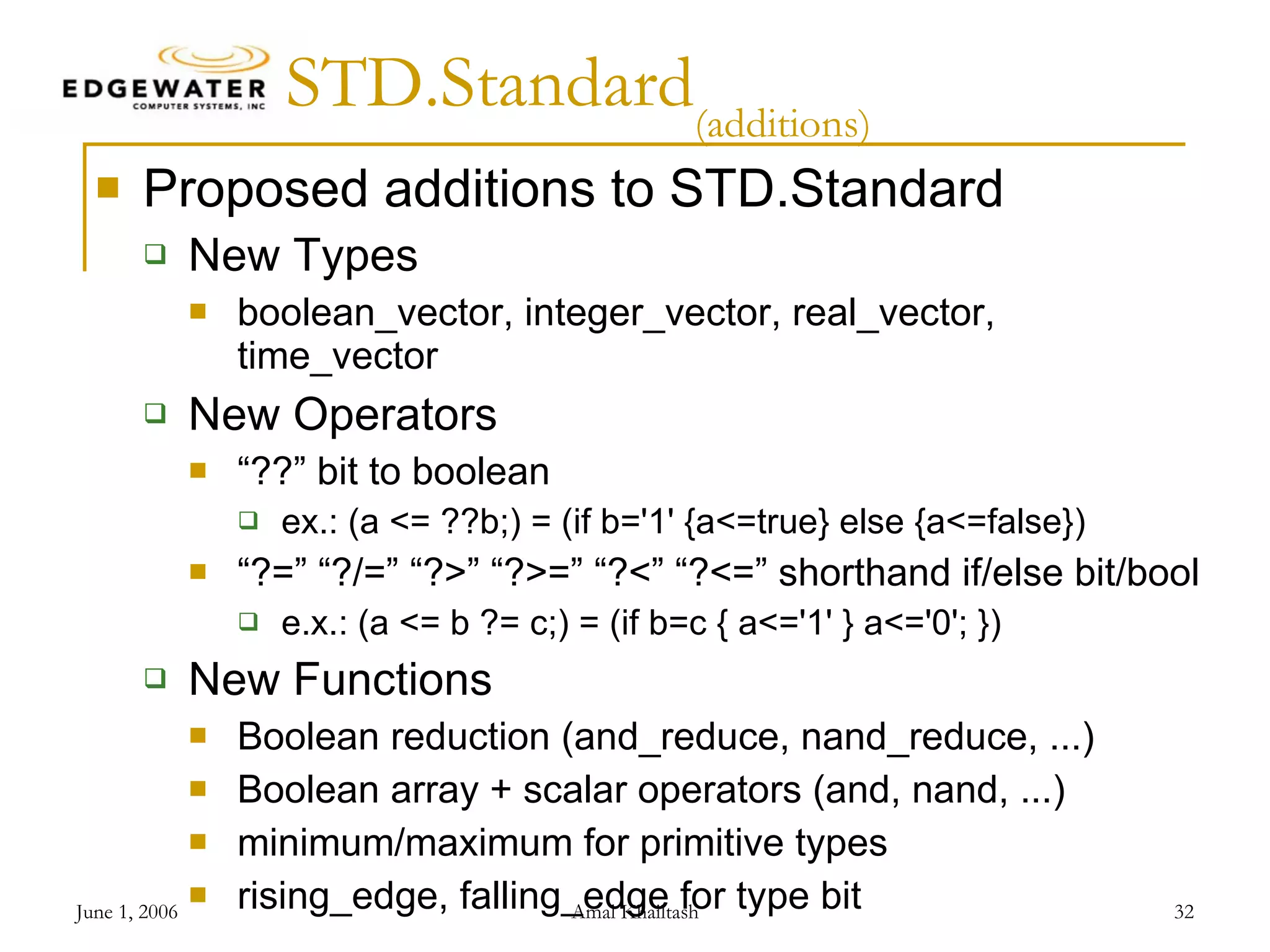

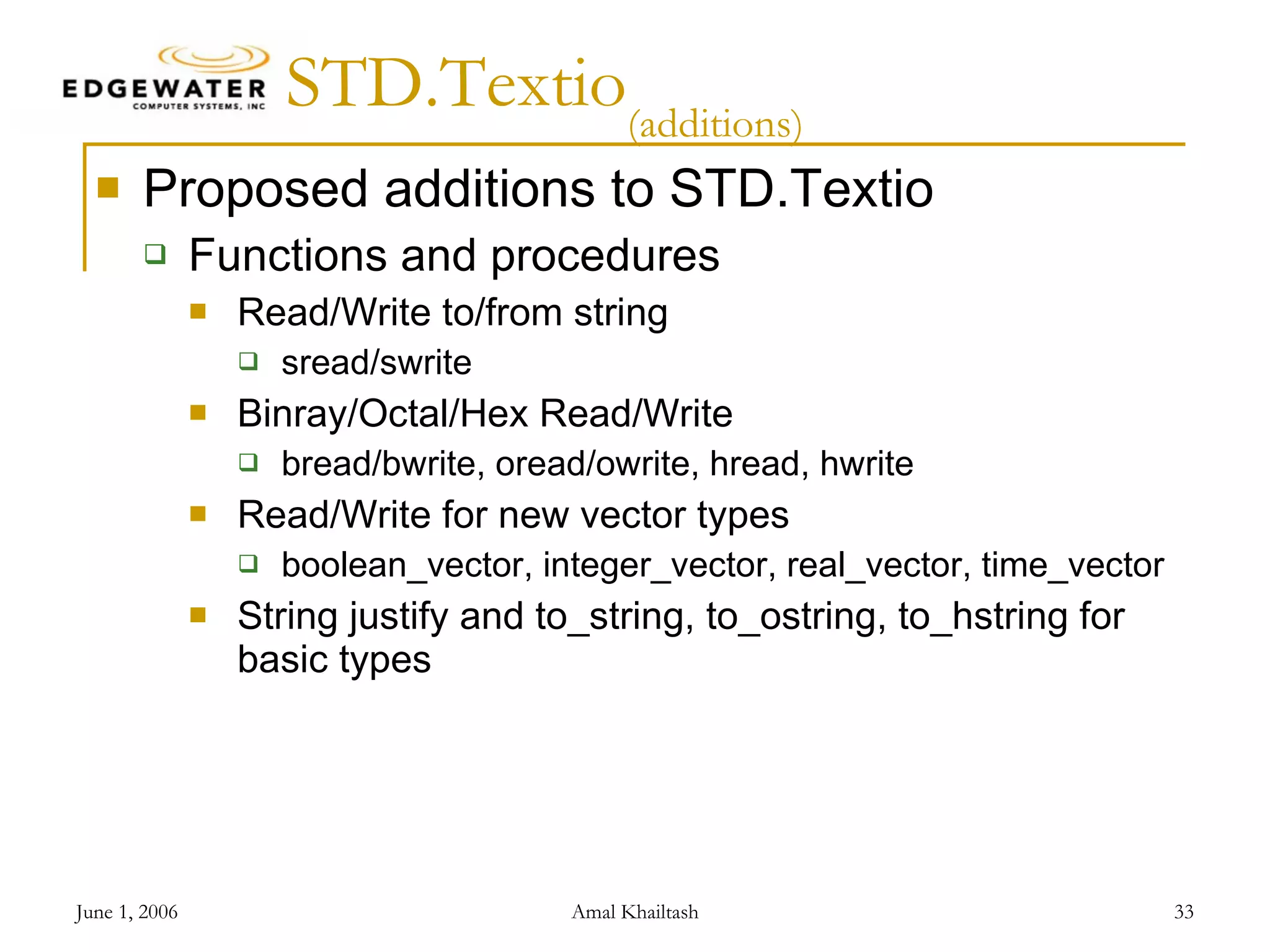

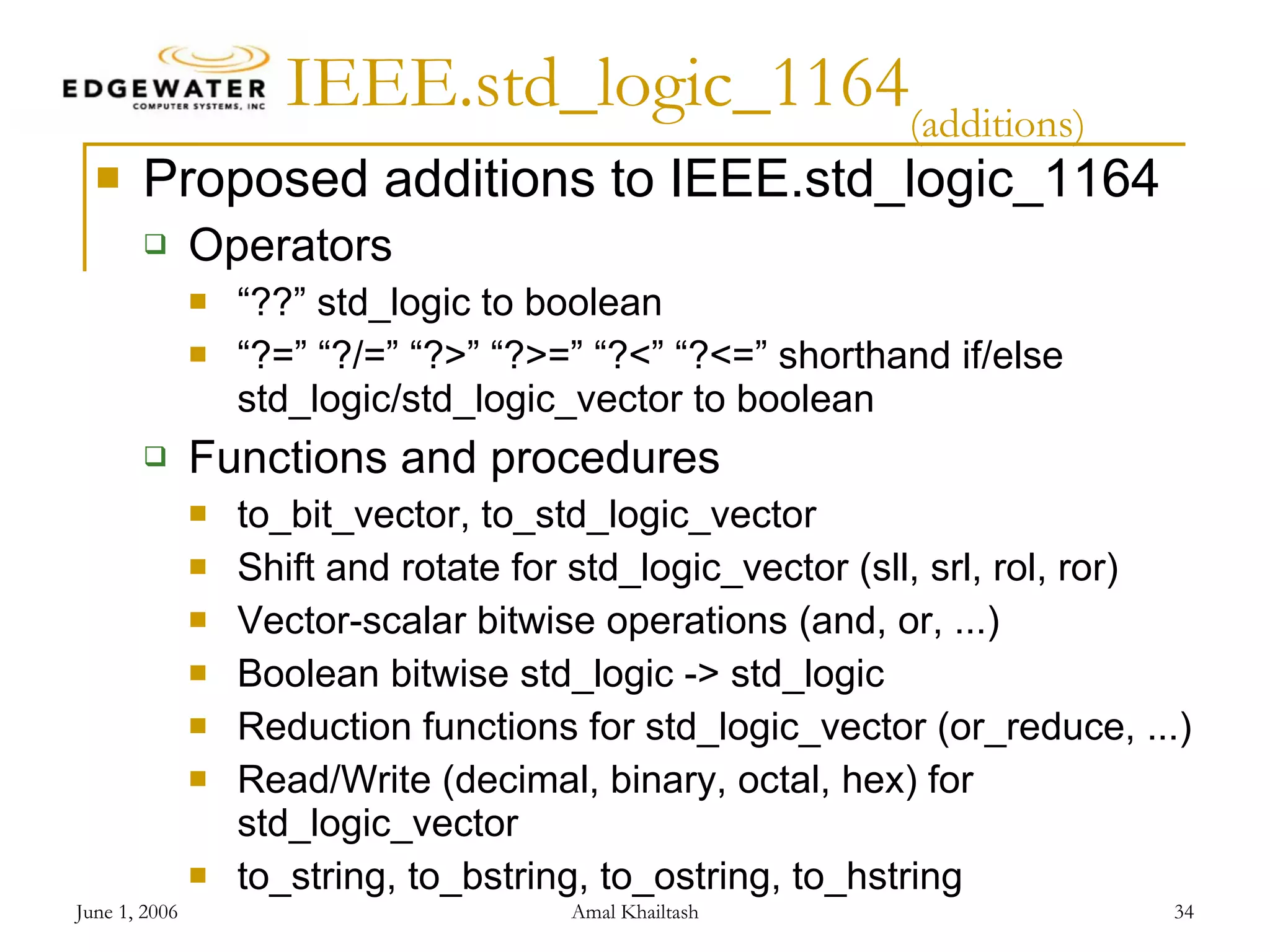

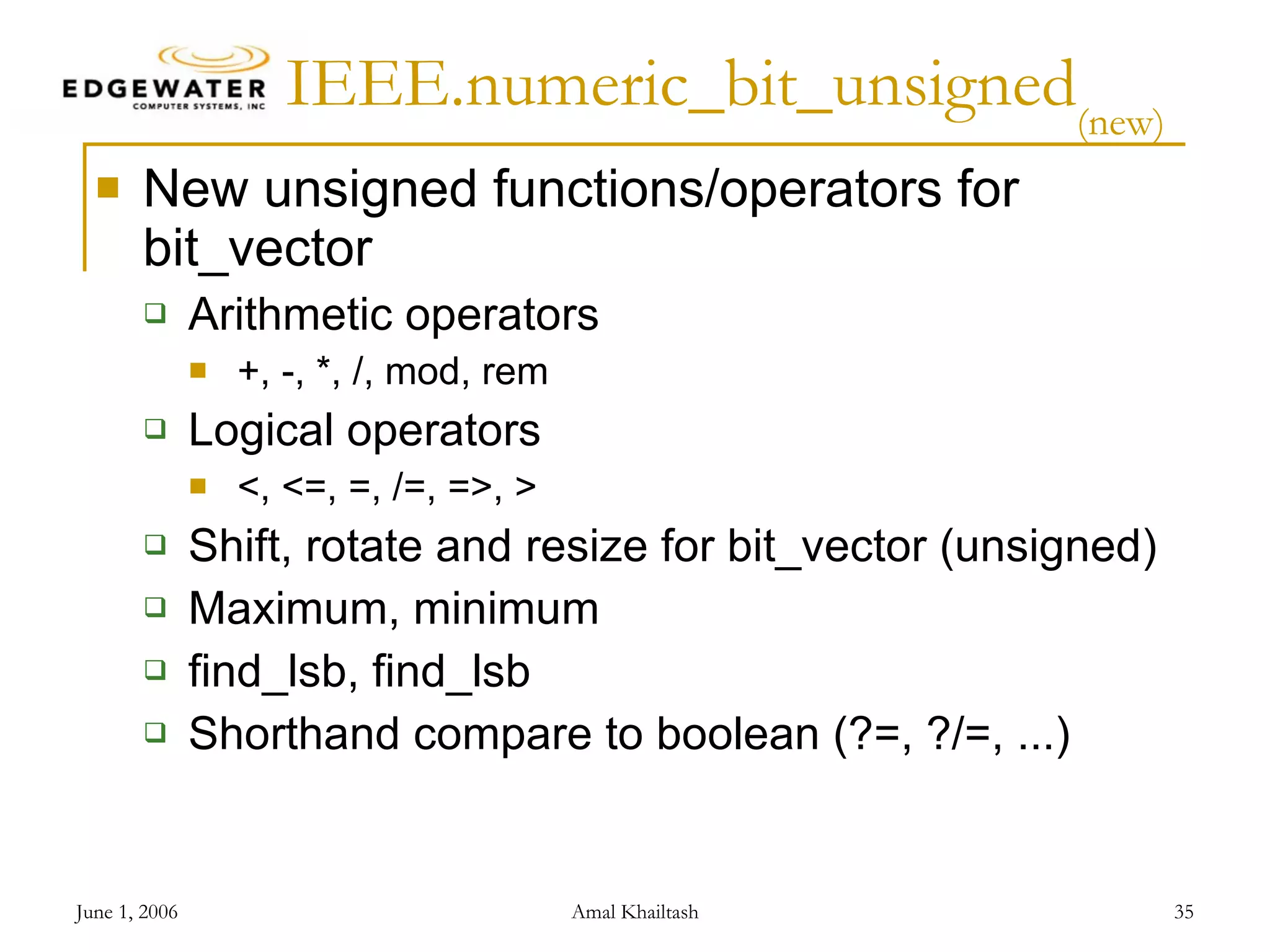

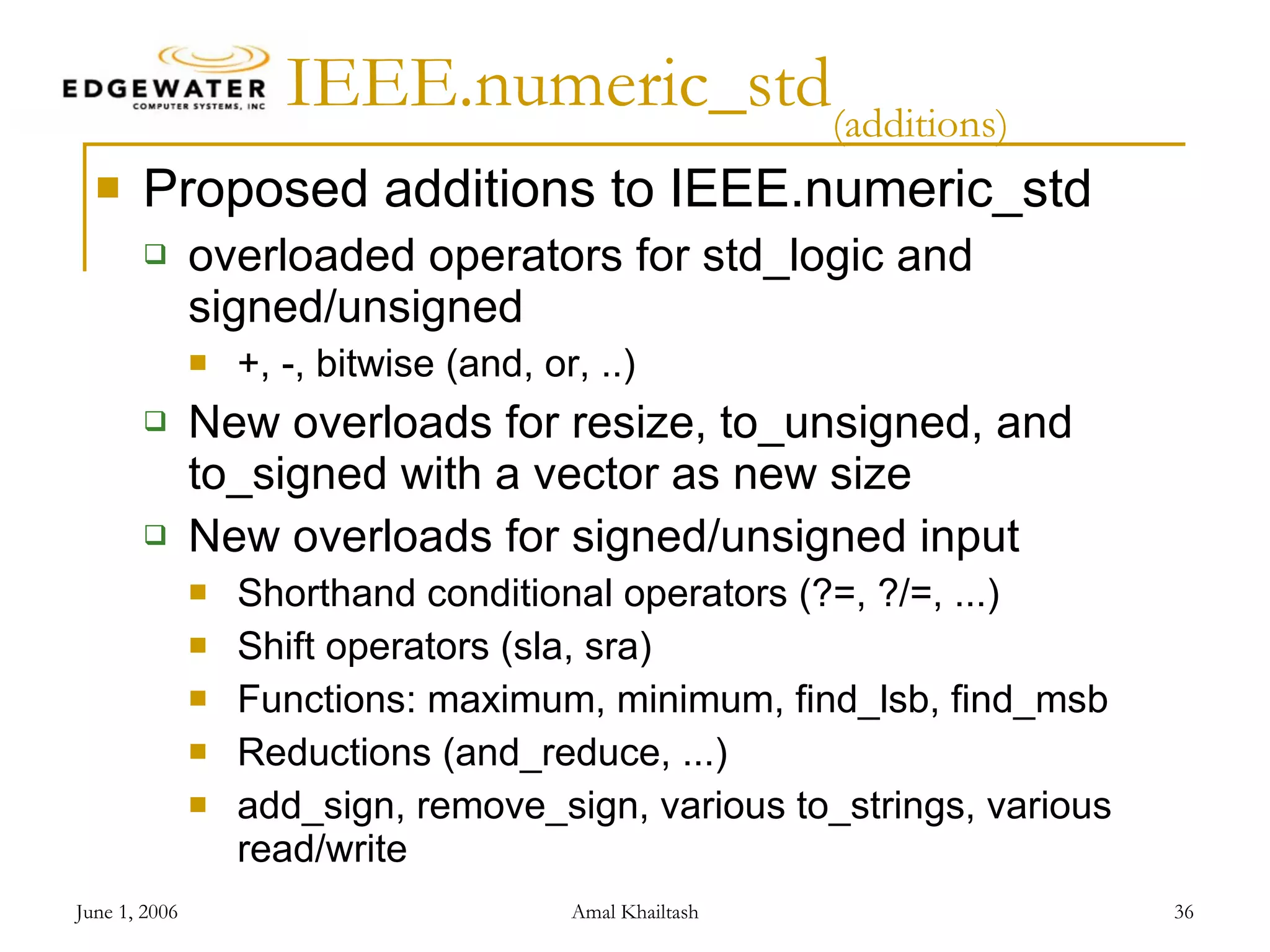

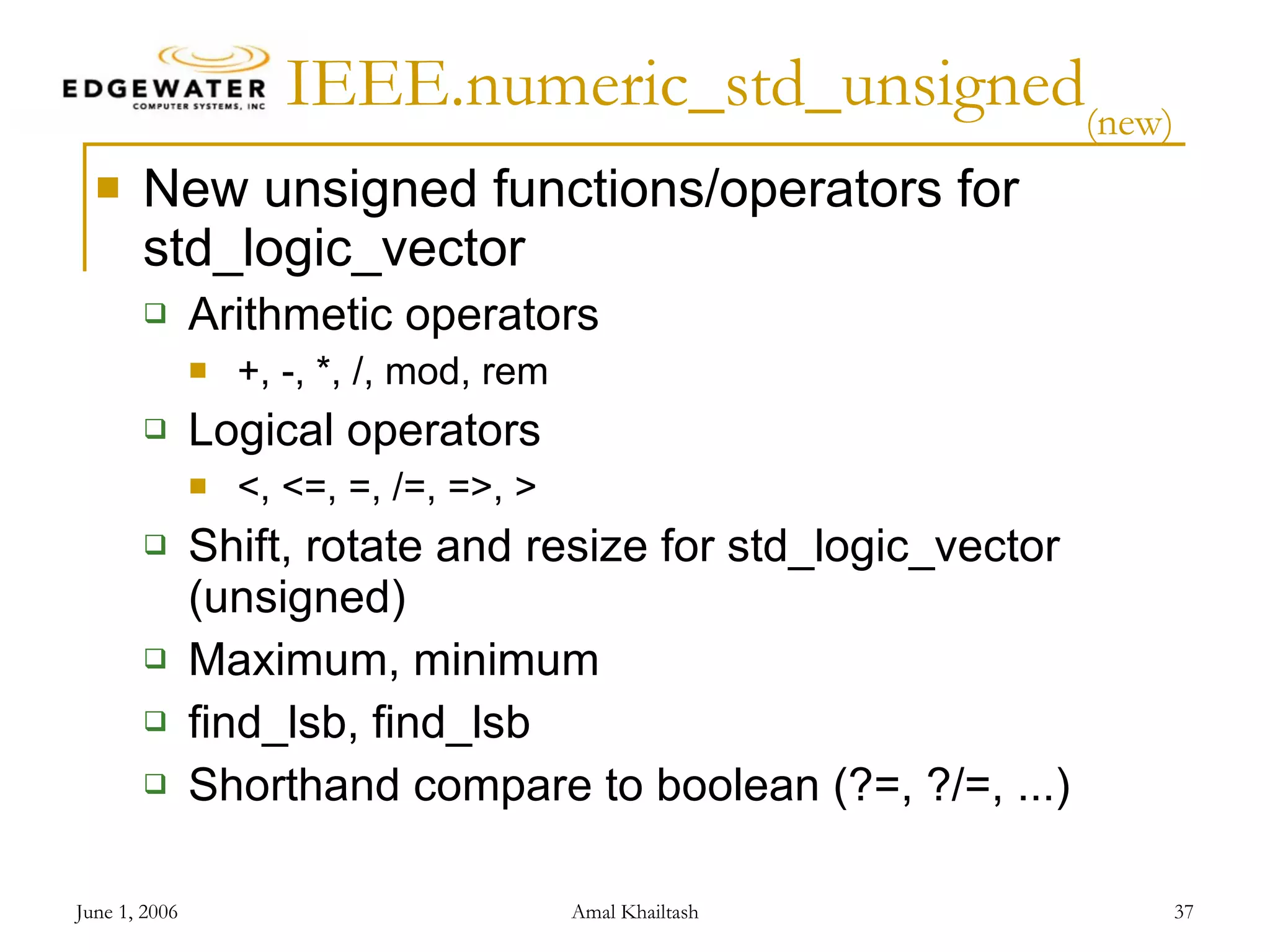

The document discusses various VHDL coding styles for arithmetic operations, emphasizing the differences between IEEE and Synopsys libraries, and providing guidelines on coding practices for arithmetic operations. It covers VHDL data types, operators, and recommended usage of libraries, along with new features introduced in VHDL-200x. The document concludes with best practices for writing generic, technology-independent VHDL code, particularly in arithmetic and core design.

![IEEE.fixed_pkg (new) New fixed-point package Various rounding, saturations styles Implemented as constant, but will use package generics when new VHDL-200x is finalized New Data Types Unsigned/Signed fixed-point (ufixed, sfixed) Decimal point between index 0 and -1 e.x.: sfixed(1, -2) { “xx.xx” -> range [-2.0 .. +1.75] } Operators/Functions (overloads for real/integer and sfixed/ufixed) Abs, +, -, *, /, mod, rem Divide, reciprocal, remainder, modulo, scalb Logical (<, <=, ...) and shorthand logical (?=, ?/=, ...) Shift/rotate, bitwise, reduction, resize, conversion and to_string, from_string, and various read/write](https://image.slidesharecdn.com/vhdlarithmetic-1228314776303295-9/75/VHDL-Packages-Coding-Styles-for-Arithmetic-Operations-and-VHDL-200x-Additions-38-2048.jpg)