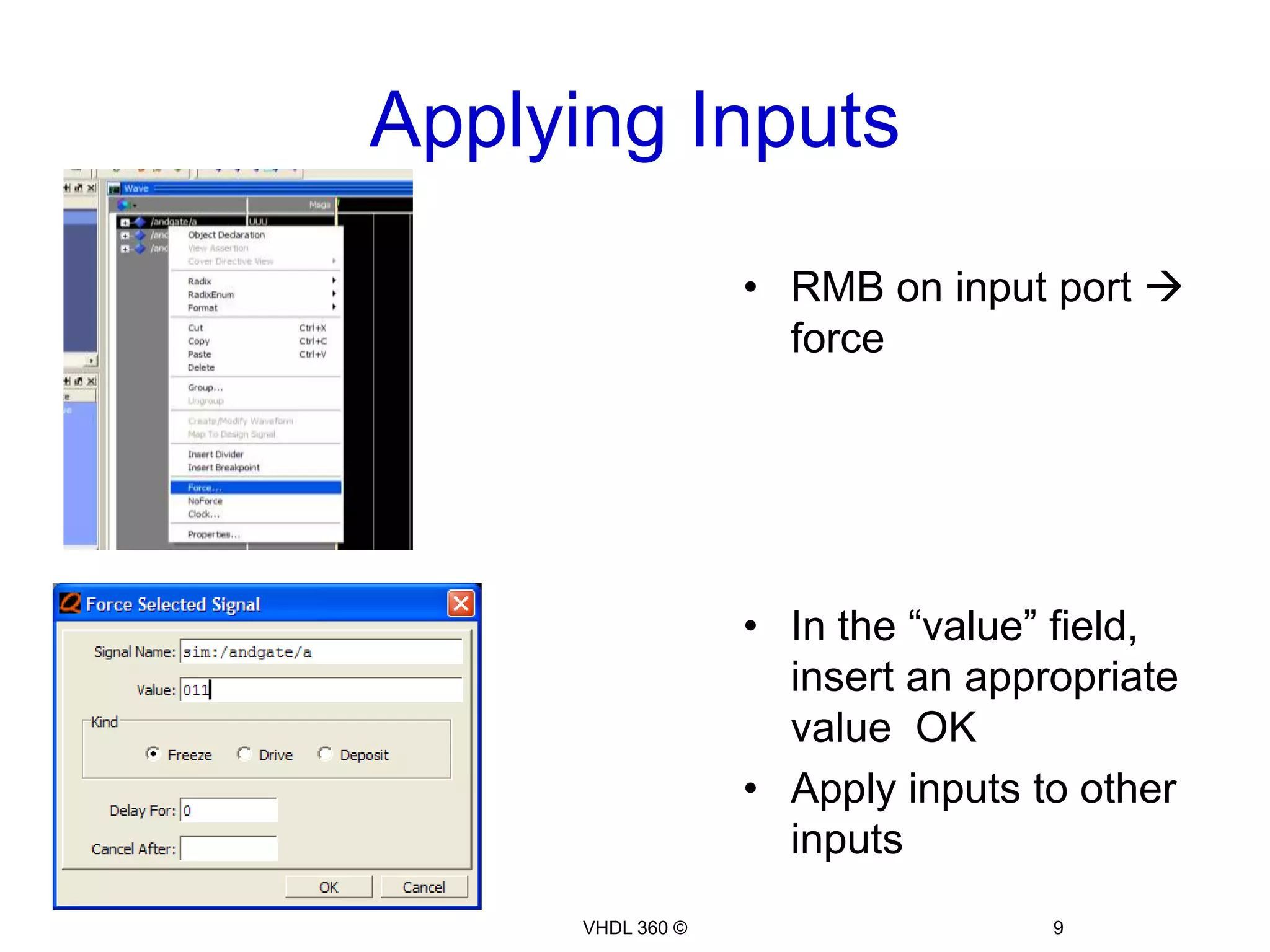

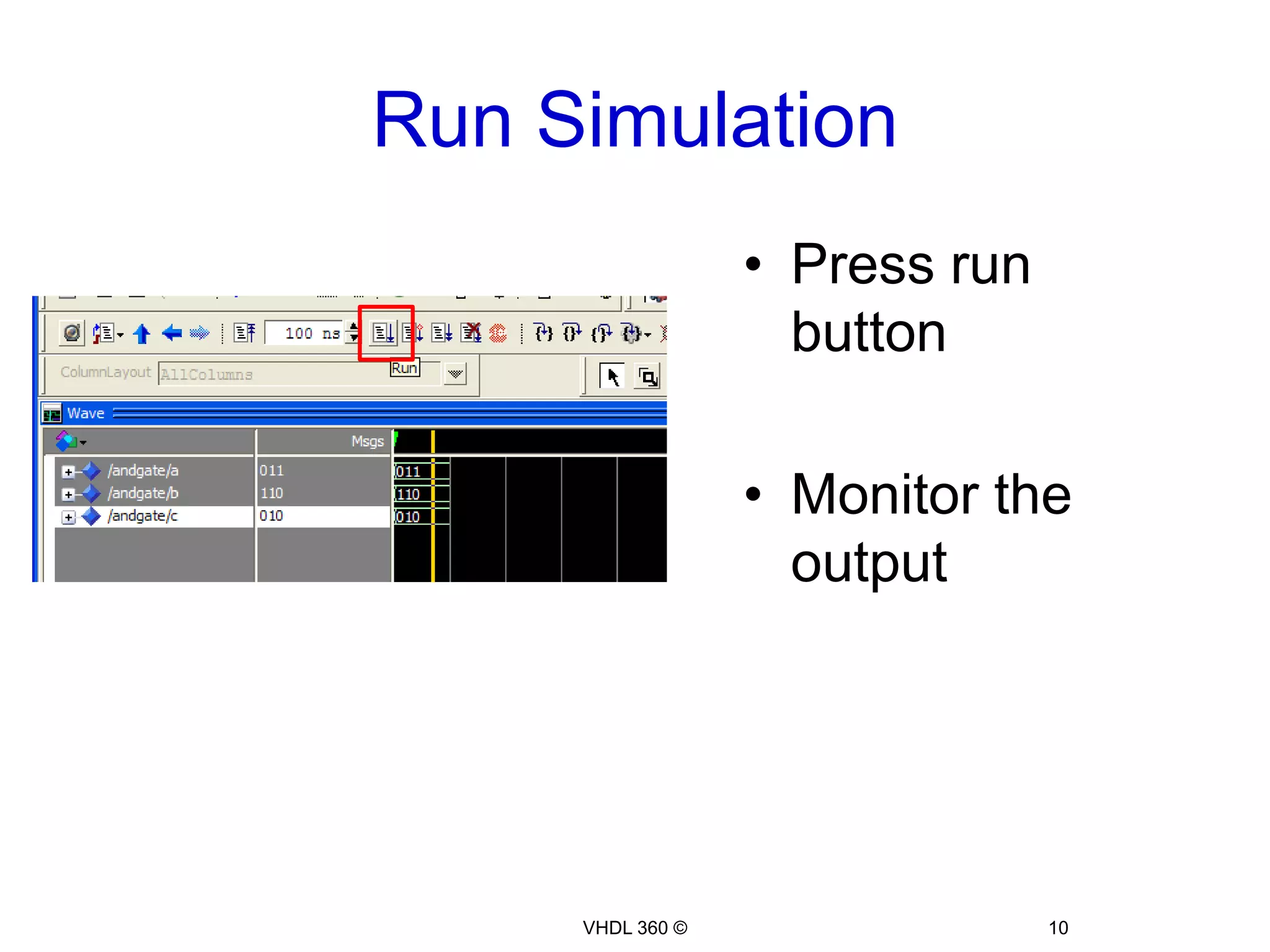

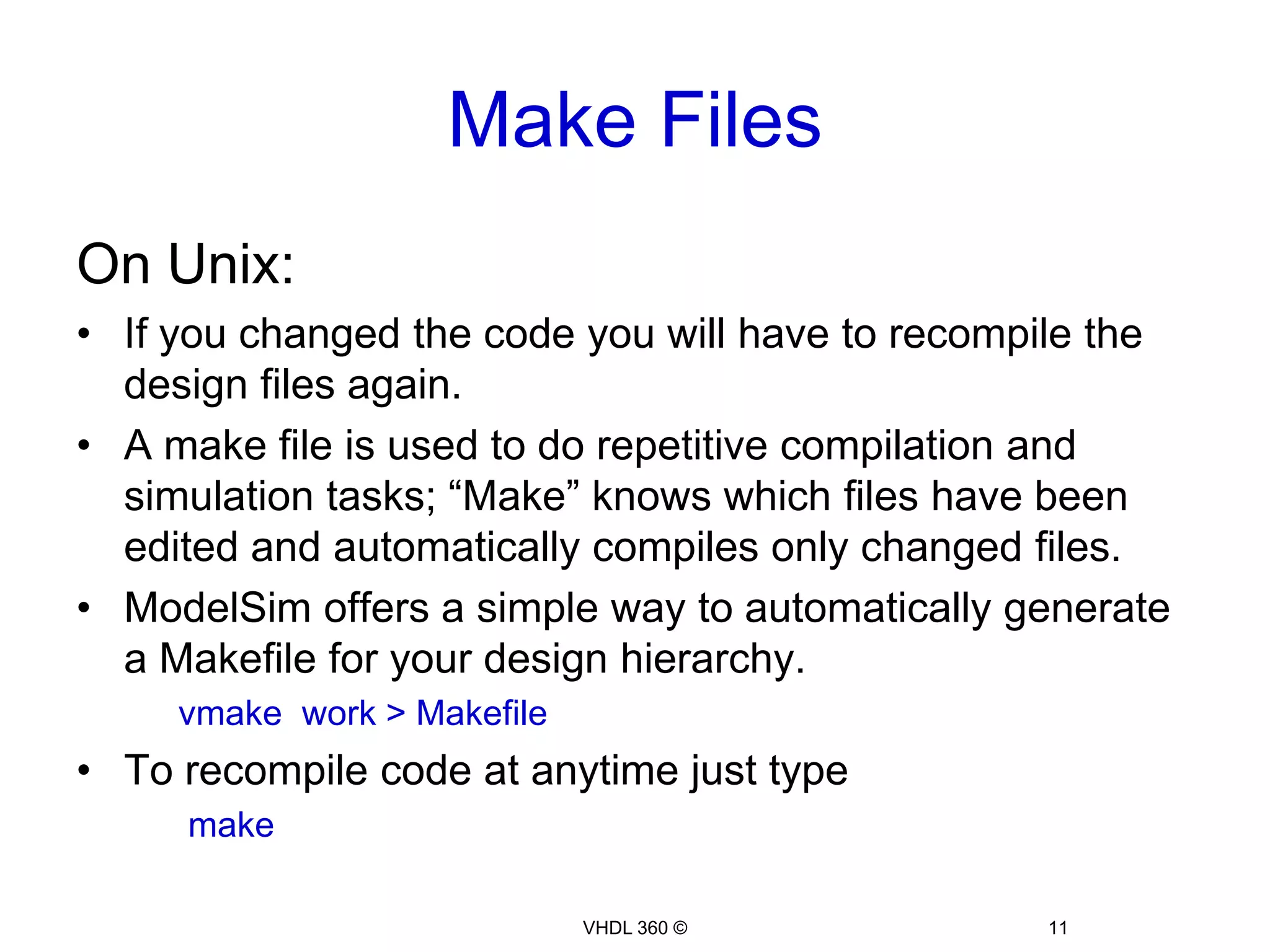

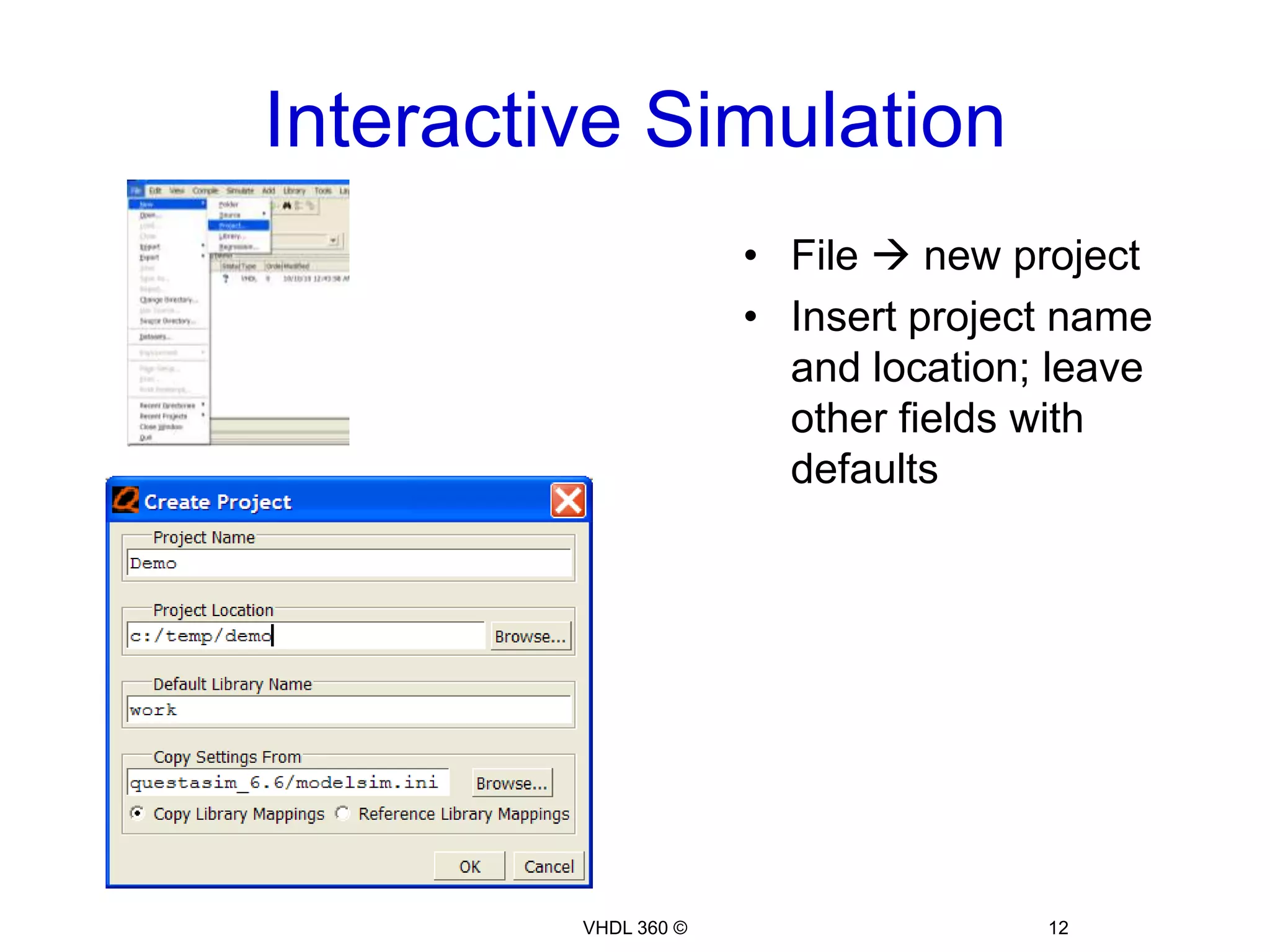

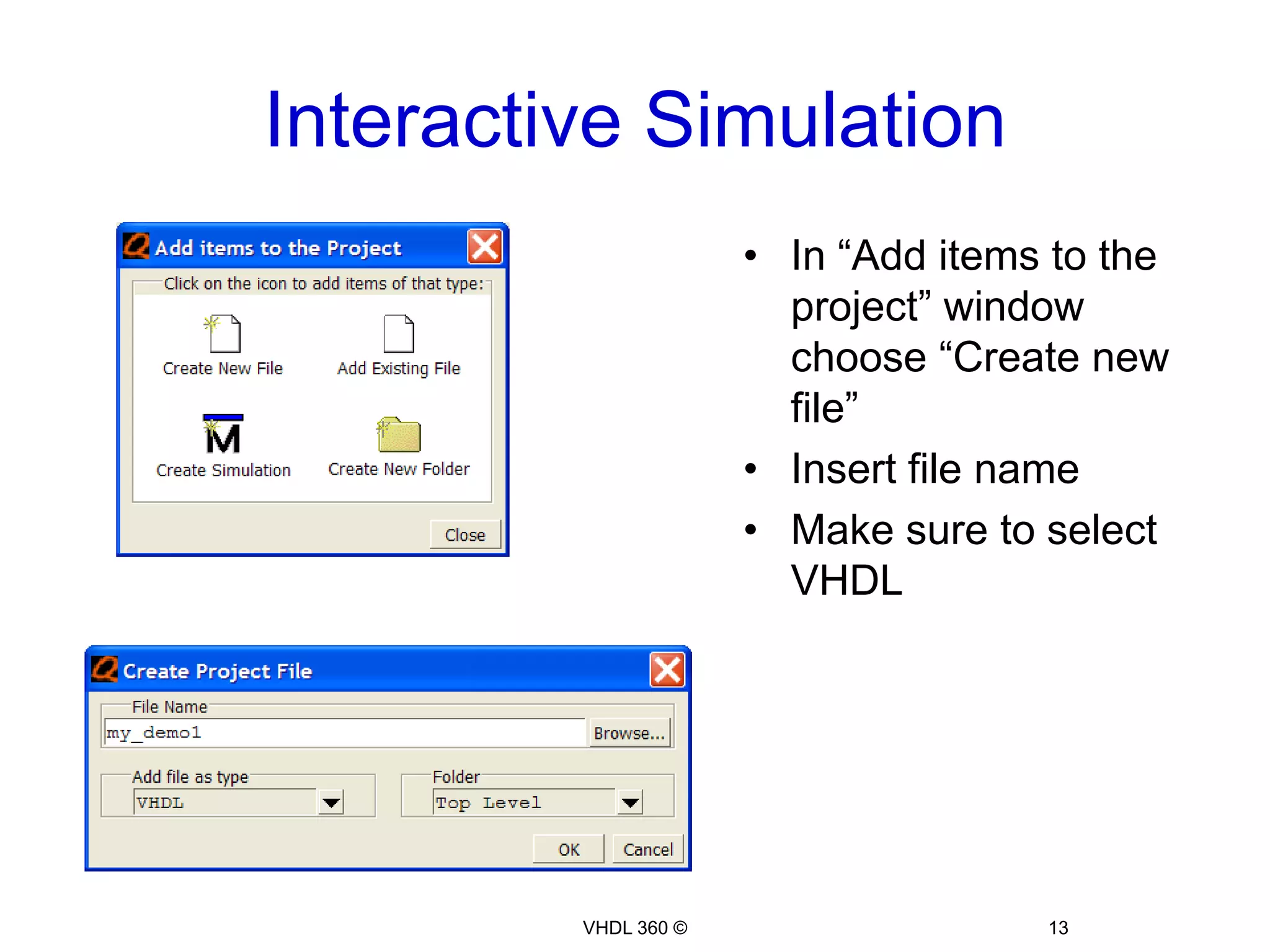

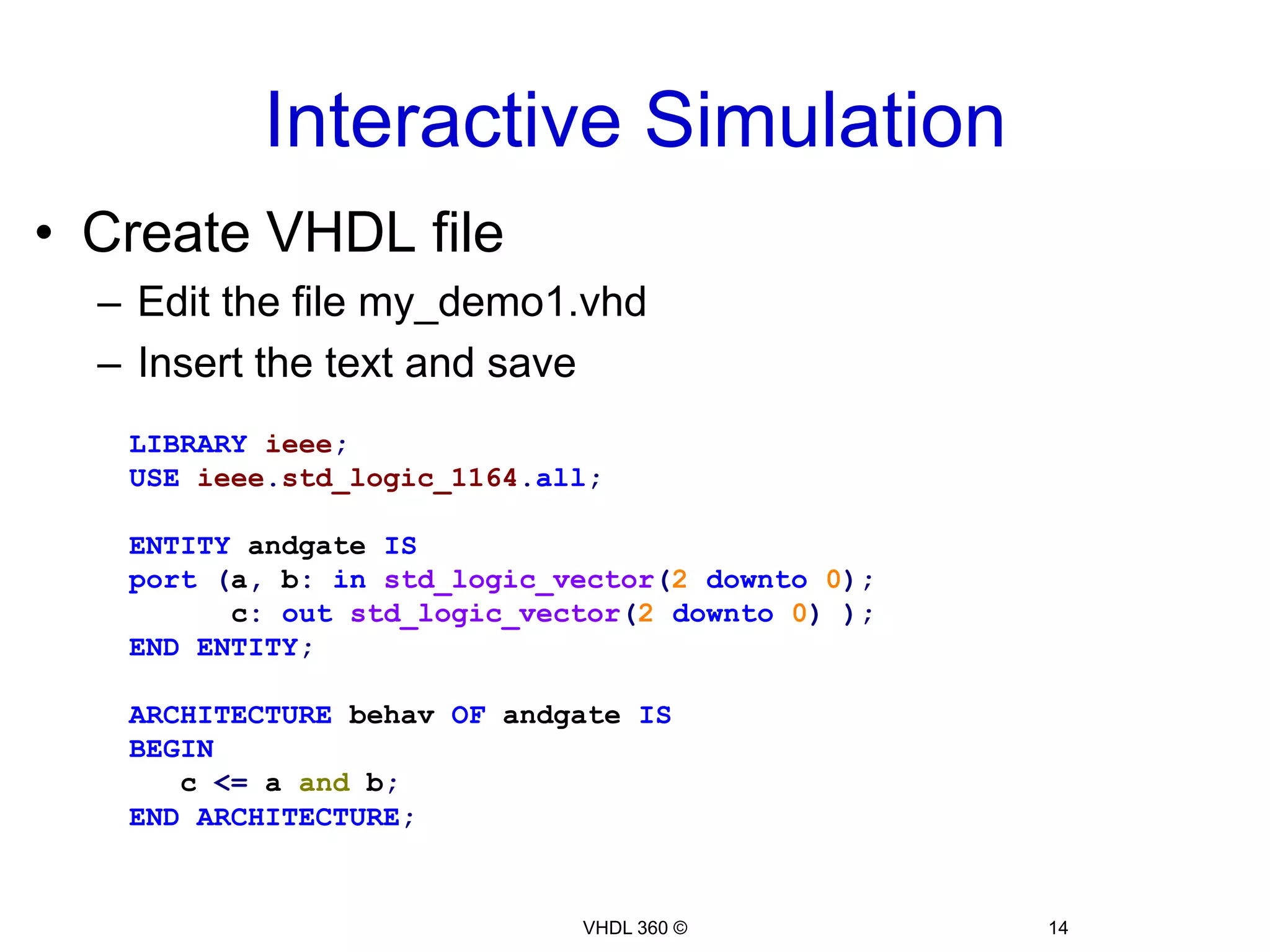

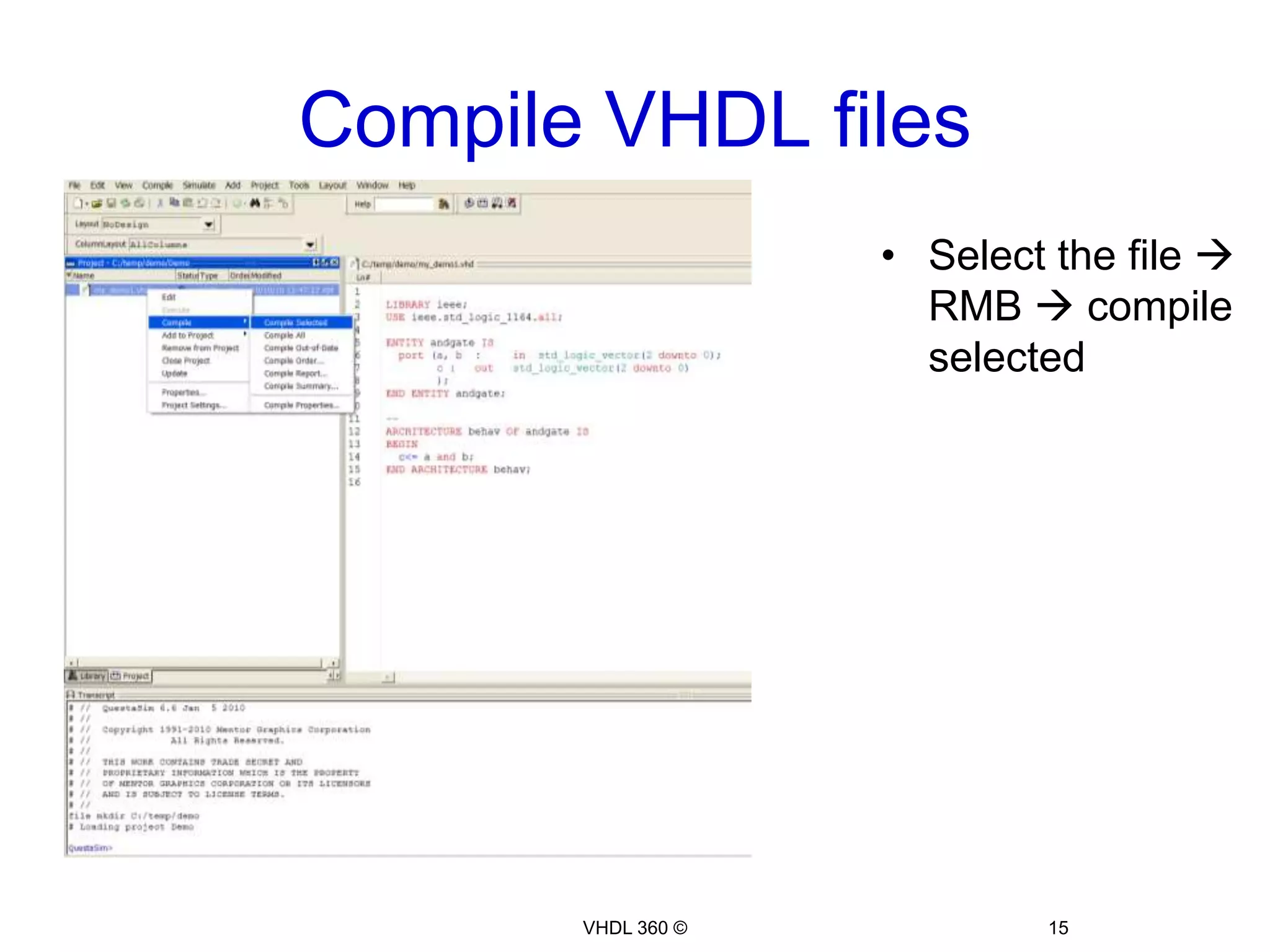

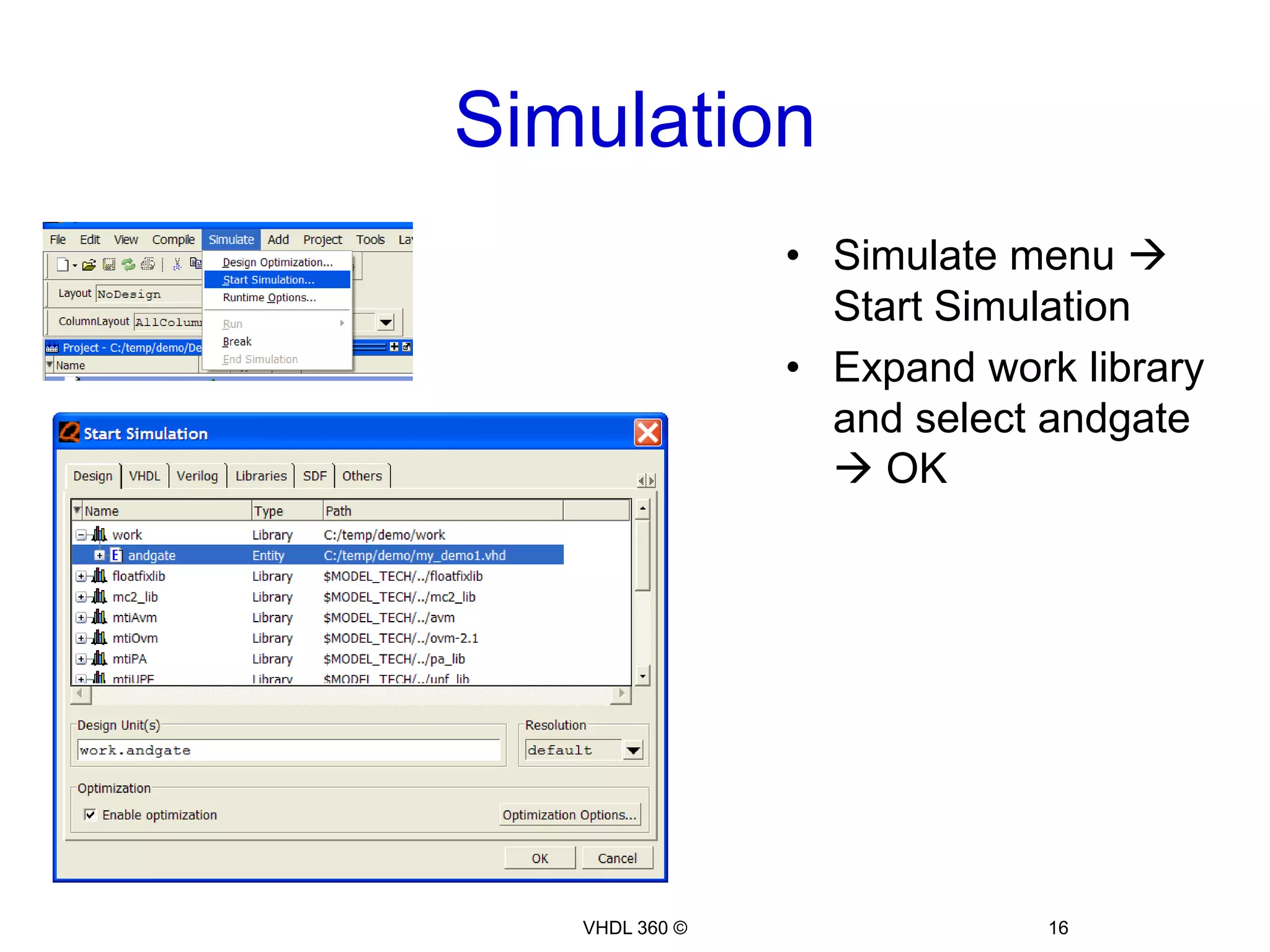

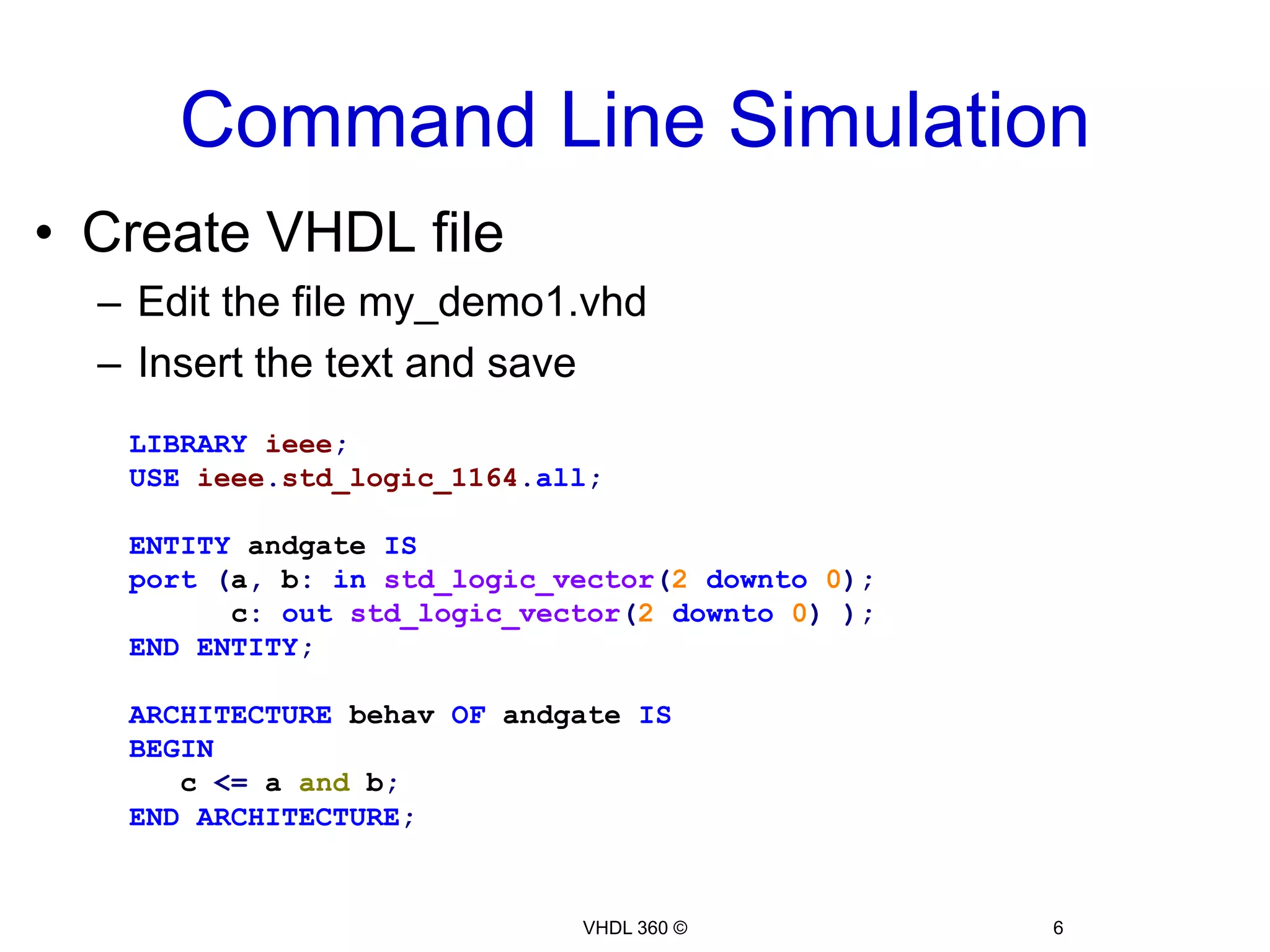

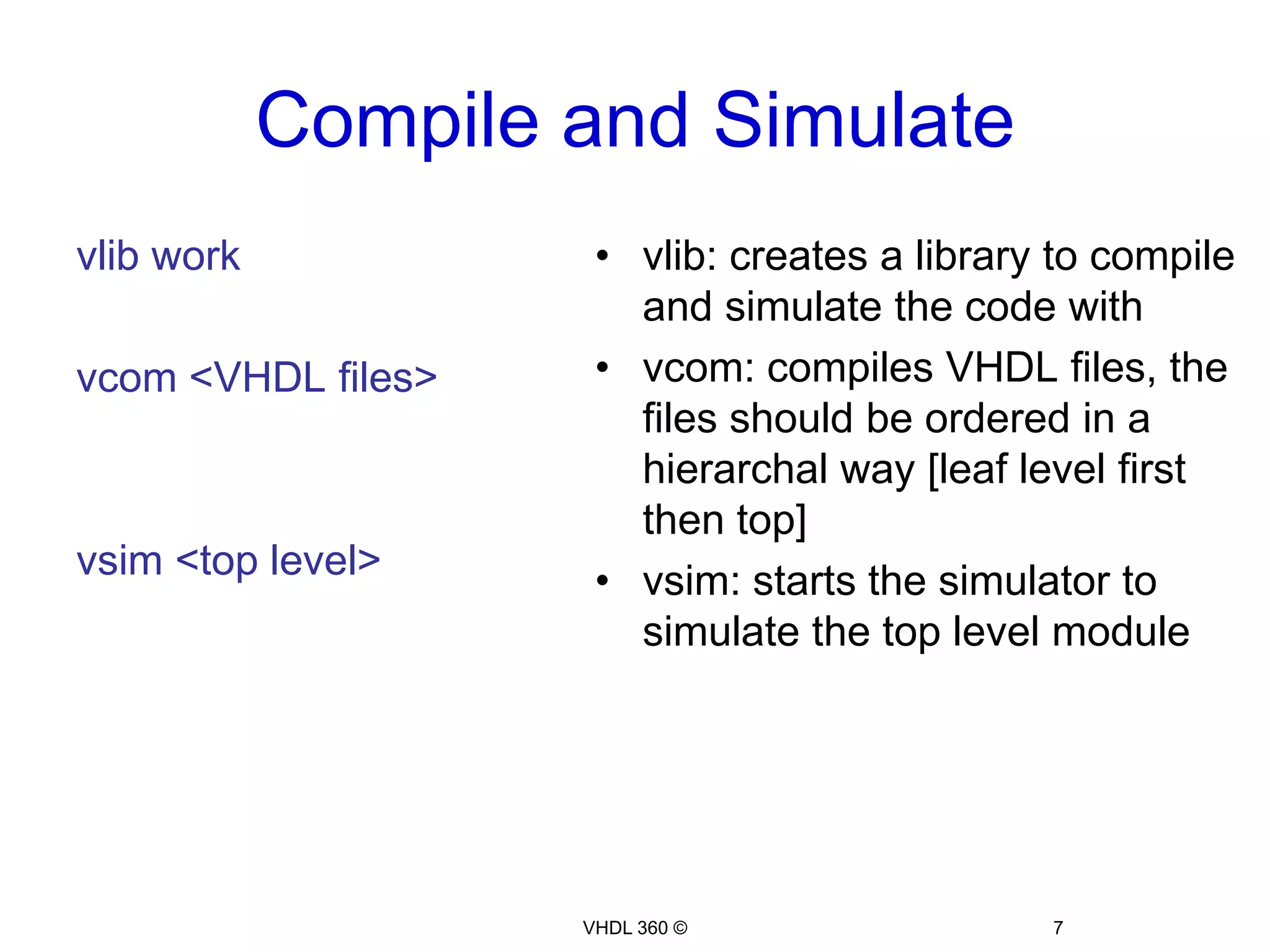

This document provides an overview of using ModelSim to simulate VHDL designs. It discusses compiling and simulating designs from the command line as well as interactively within ModelSim. Key steps covered include compiling VHDL files with vcom, simulating with vsim, adding signals to the waveform window, applying inputs, running simulations, generating makefiles, and creating and simulating designs within the ModelSim GUI. The document aims to teach basic ModelSim simulation commands and workflow.

![vcom: compiles VHDL files, the files should be ordered in a hierarchal way [leaf level first then top]](https://image.slidesharecdn.com/simulationusingmodelsimversion1-1-101217113928-phpapp01/75/Simulation-using-model-sim-8-2048.jpg)