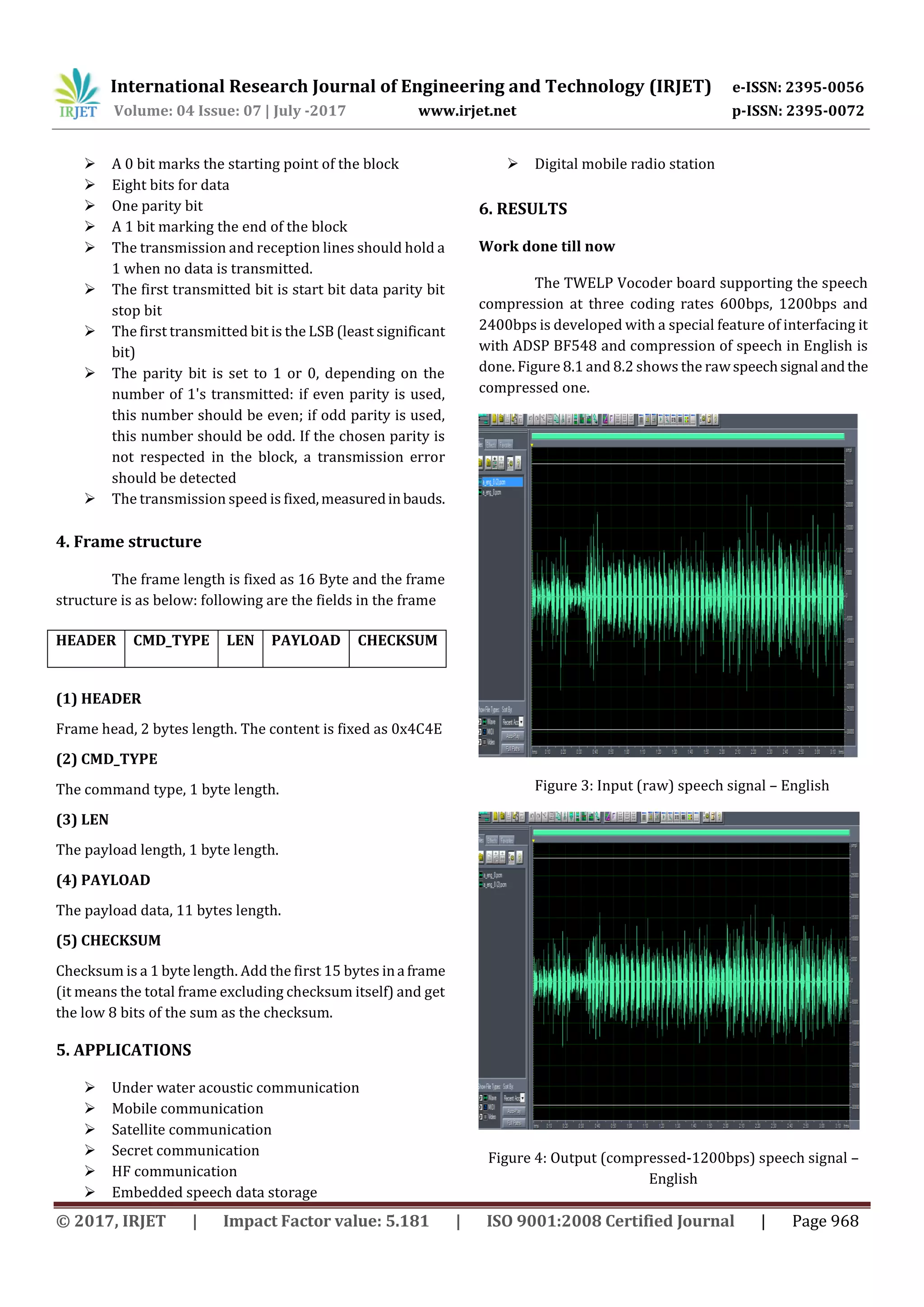

This document summarizes a research paper that presents the implementation of a low bit rate vocoder for speech compression. The vocoder board was designed using a Blackfin BF548 digital signal processor. The board includes components for speech encoding, decoding, and compression. It was tested by inputting speech in different languages and calculating the perceptual evaluation of speech quality score of the original and compressed speech. The goal of the project is to design a hardware vocoder that can compress speech efficiently at a low bit rate for applications with limited bandwidth such as military communications.

![International Research Journal of Engineering and Technology (IRJET) e-ISSN: 2395-0056 Volume: 04 Issue: 07 | July -2017 www.irjet.net p-ISSN: 2395-0072 © 2017, IRJET | Impact Factor value: 5.181 | ISO 9001:2008 Certified Journal | Page 969 PESQ result PESQ result for the English speech signal is obtained VECINPP50b_eng_8.pcm VECOUT_1b_eng_8.pcm 2.826 2.569 7. Future work The compression of speech in different other languages has to perform. The PESQ results for input (raw) and output (compressed) has to find out to compare the quality of compressed speechwithoriginal speech.Thesame thing has to be performed at the rate of 2400 bps. REFERENCE [1] T. E. Tremain, “The Government Standard Linear Predictive Coding LPC-10”, Speech Technology, pp.40-49, 2014 [2] A. McCree, T. Kwan, E. B. George and V. Viswanathan, “A 2.4 kbit’s MELP coder candidate for the new U.S. Federal Standard”, Acoustics, Speech, and Signal Processing, IEEE International Conference, vol.1, pp. 200-203, 2015. [3] L. M. Supplee, R. P. Cohn, J. S. Collura and A. McCree, “MELP: the new Federal Standard at 2400bps”, Acoustics, Speech, and Signal Processing, IEEE International Conference, vol.2, pp. 1591-1594, 2011. [4] J. Wang, J, Zhao, J. Yang and Y. Yang, “The research for the MELP Vocoder and its real-time replementation”, in Journal of the Institution of Engineers, vol. 44, pp.38-58, 2004. [5] ADSP-BF537 Blackfin Processor Hardware Reference manual, Revision 3.4, 2013. [6] M. Olausson and L. Dake, “The ADSP-21535 Blackfin and Speech Coding”, Proceedings of the Swedish System-on-chip Conference (SSoCC), 2003. [7] Blackfin DSP Instruction Set Reference, 2002. [8] ADSP-21535 Blackfin DSP Hardware Reference, 2002. [9] ITU-t recommendationong.723.1,dual ratespeechcoder for multimedia communications transmitting at 5.3 and 6.3 kbit/s, 2013 [10] ITU-t recommendation g.729, coding of speech at 8 kbit/s using conjugate-structure algebraic-codeexcited-linear-prediction (cs-acelp), 2014 [11] ETSI GSM Fullrate Speech Codec for Analog Devices Blackfin, Bayer DSP Solutions, 2008. [12] G. Bertini, F. Fontata, D. Gonzalez, L. Grassi and M. Magrini, “Voice Transformation Algorithms with Real Time DSP Rapid Prototyping Tools”, 2004, unpublished. [13] Y. Shaked and A. L. Cole, “Implementation of MELP based Vocoder for 1200/2400 bps”, The EE Project Contest 2000, Technion Signal and Image Processing Lab, 2000, unpublished. [14] J. M. Valin , “Speex: A Free Codec for Free Speech”, available at http://jmvalin.ca/papers/speex_lca2006.pdf (Last Accessed: May 2015). [15] Vorbis codec, available at http://www.vorbis.com/ (Last Accessed: May 2015). [16] ITU-T Recommendation P.800 Methods for subjective determination of transmission quality, available at http://www.itu.int/ITU-T/ recommendations/rec.aspx?rec=3638 (Last Accessed: May 2015). [17] J. M. Gibson, “Speech coding methods, standards, and applications”, in Circuits and Systems Magazine,IEEE,vol.5, pp. 30-49, 2005.](https://image.slidesharecdn.com/irjet-v4i7226-170830105533/75/Implementation-of-Low-Bit-Rate-Vocoder-for-Speech-Compression-5-2048.jpg)