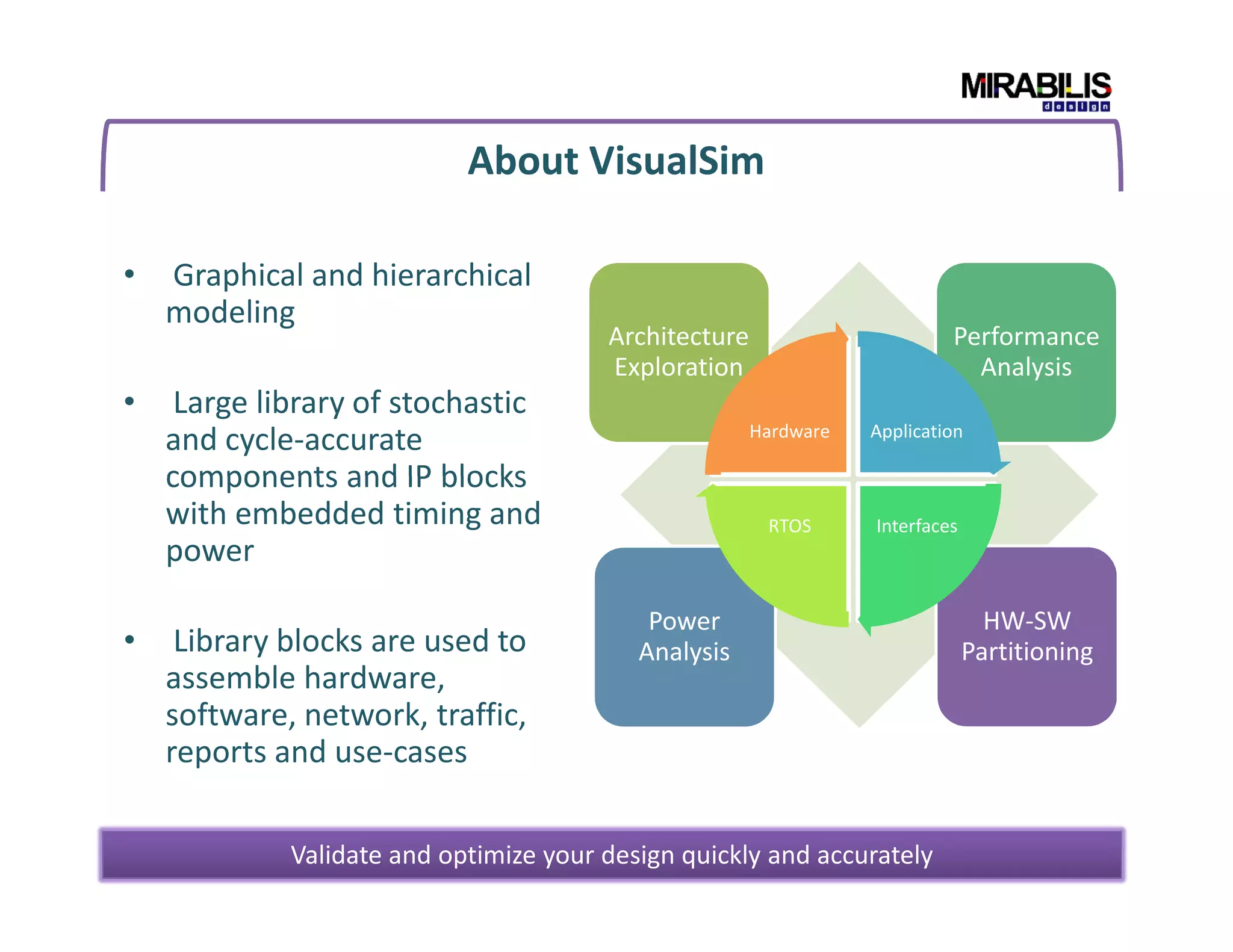

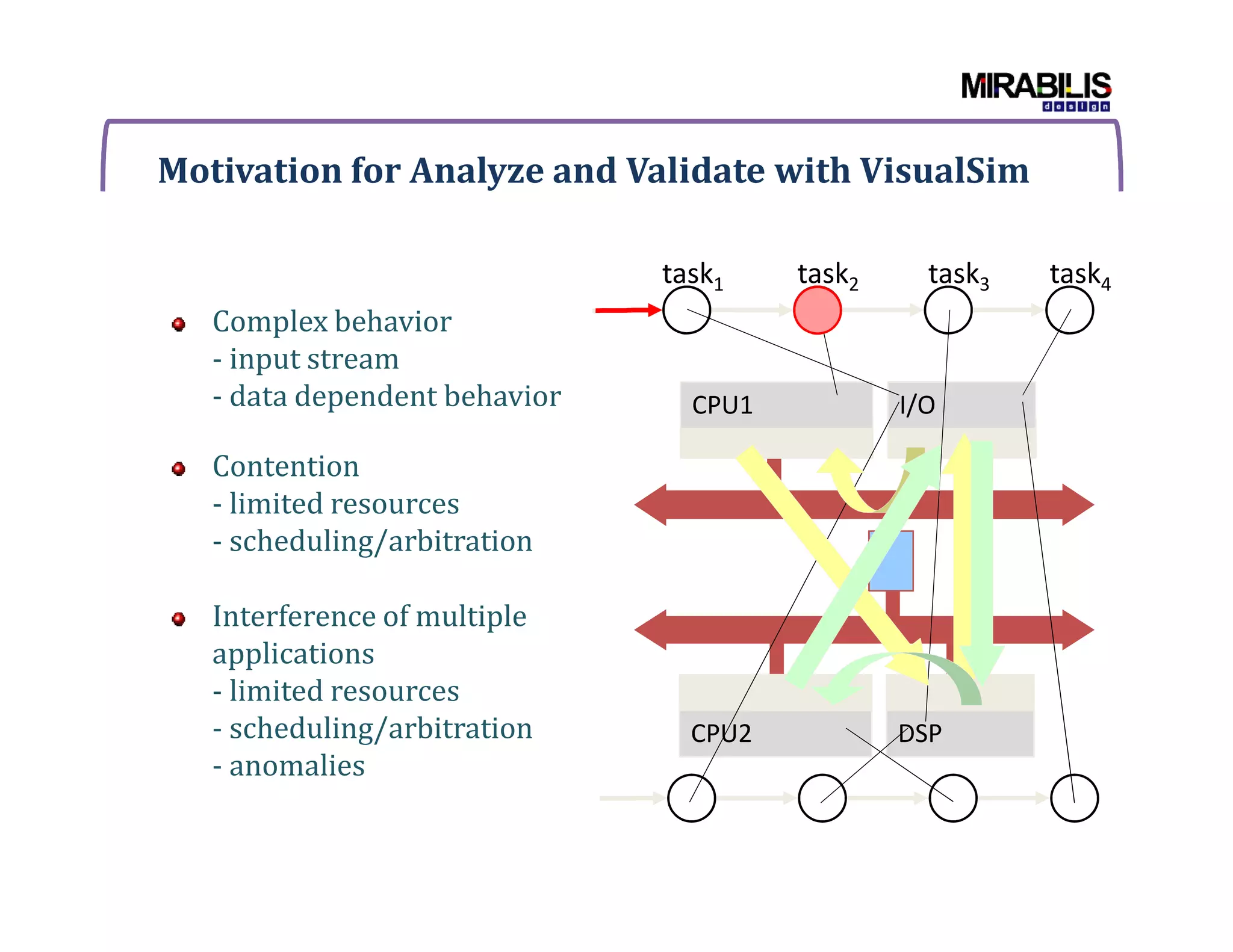

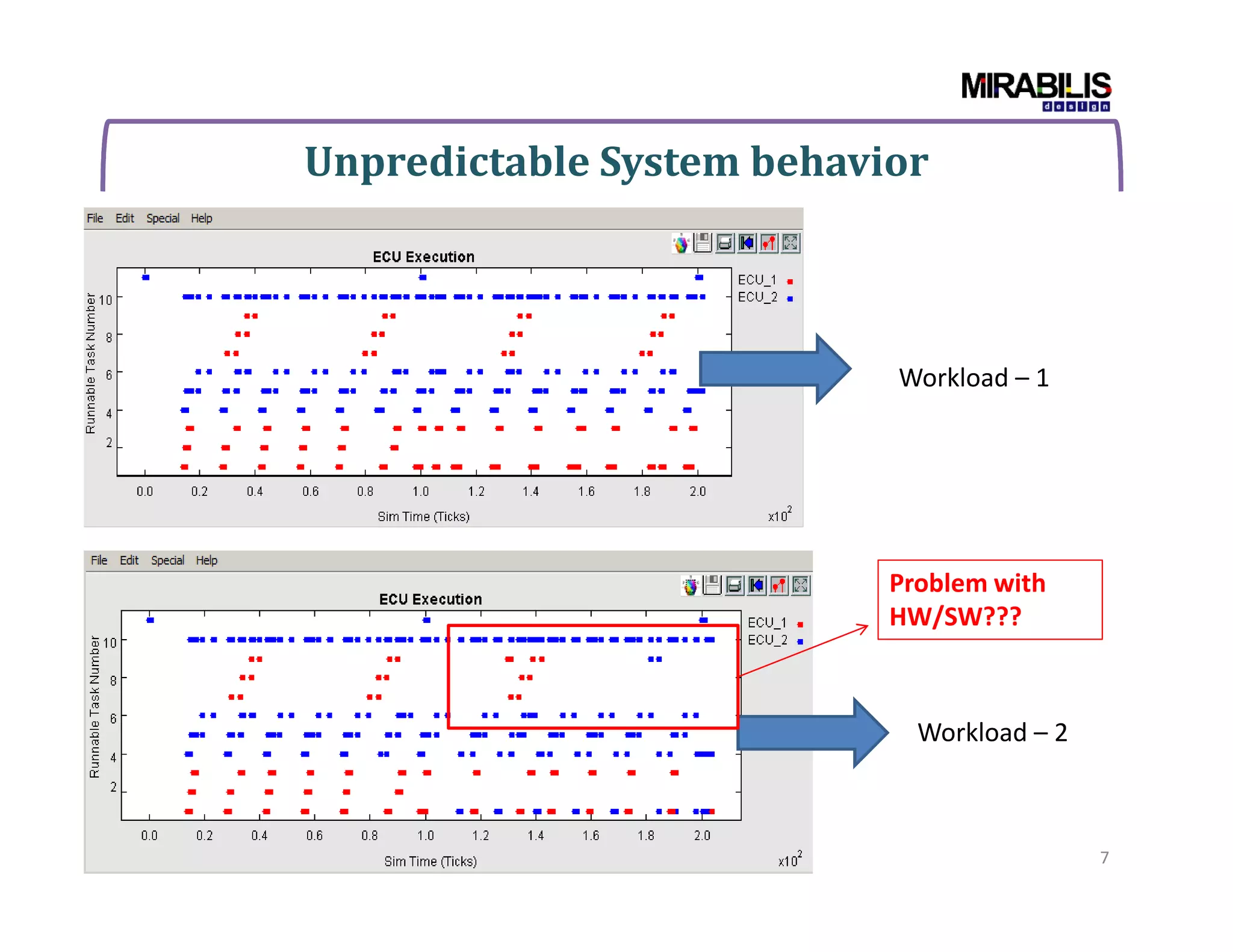

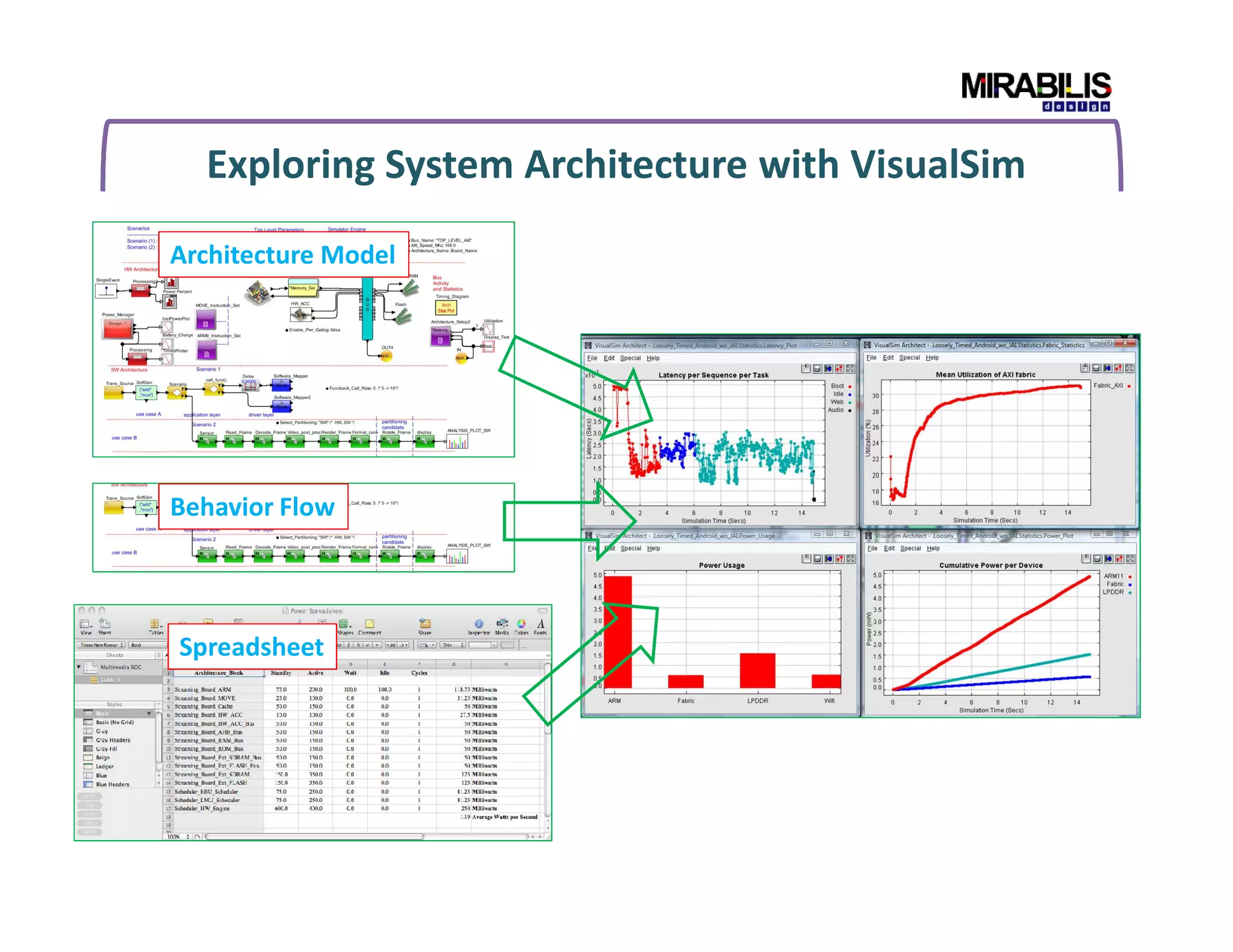

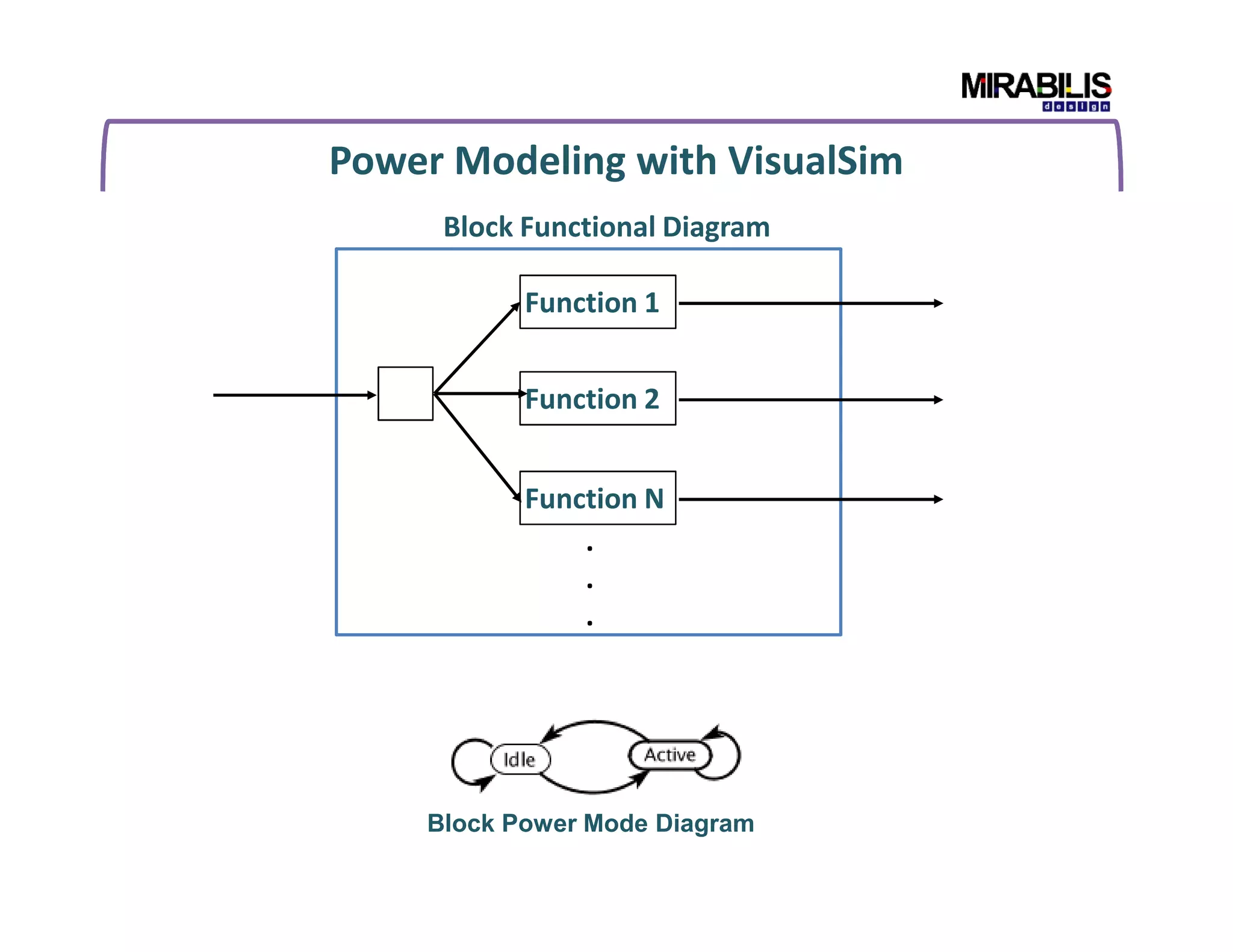

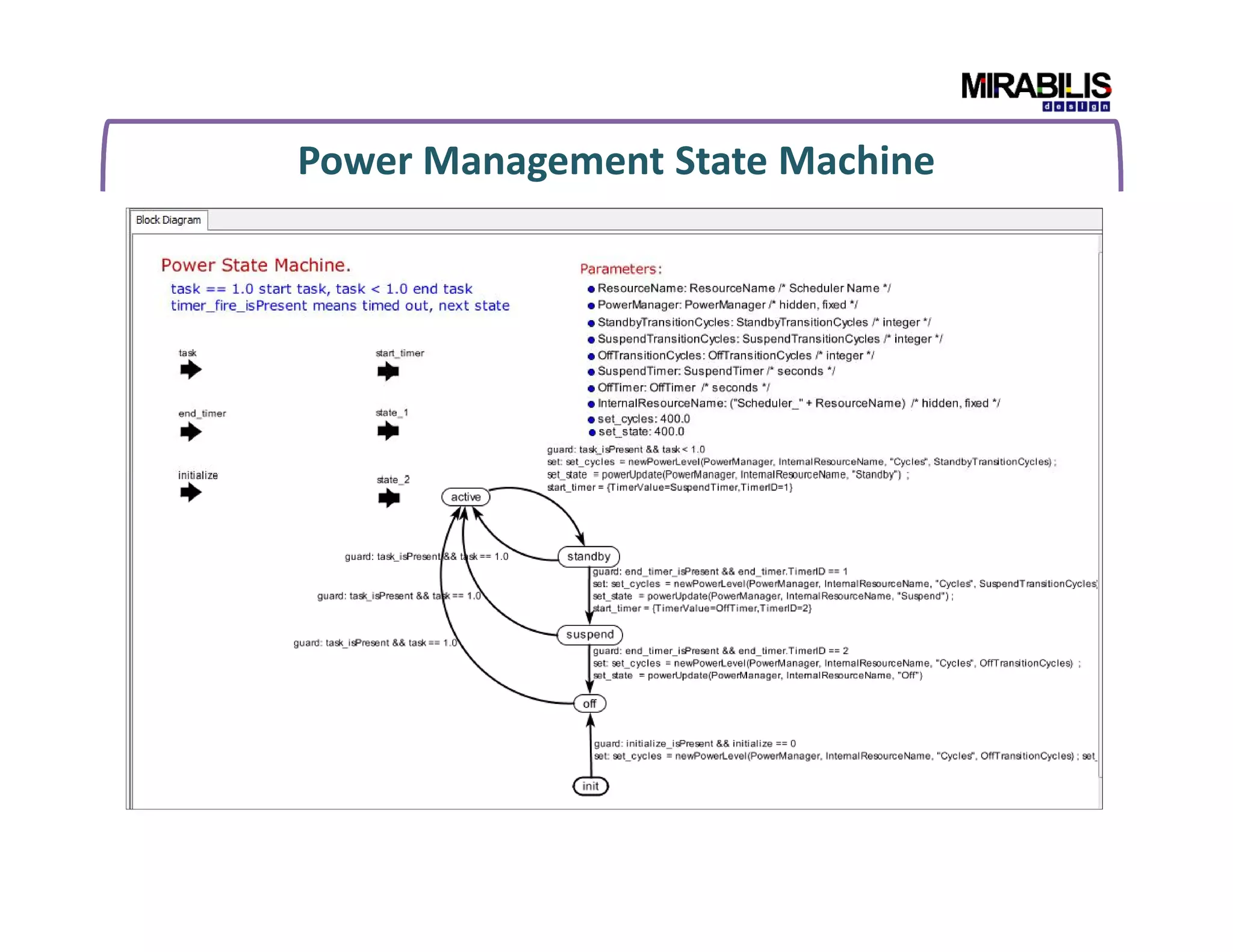

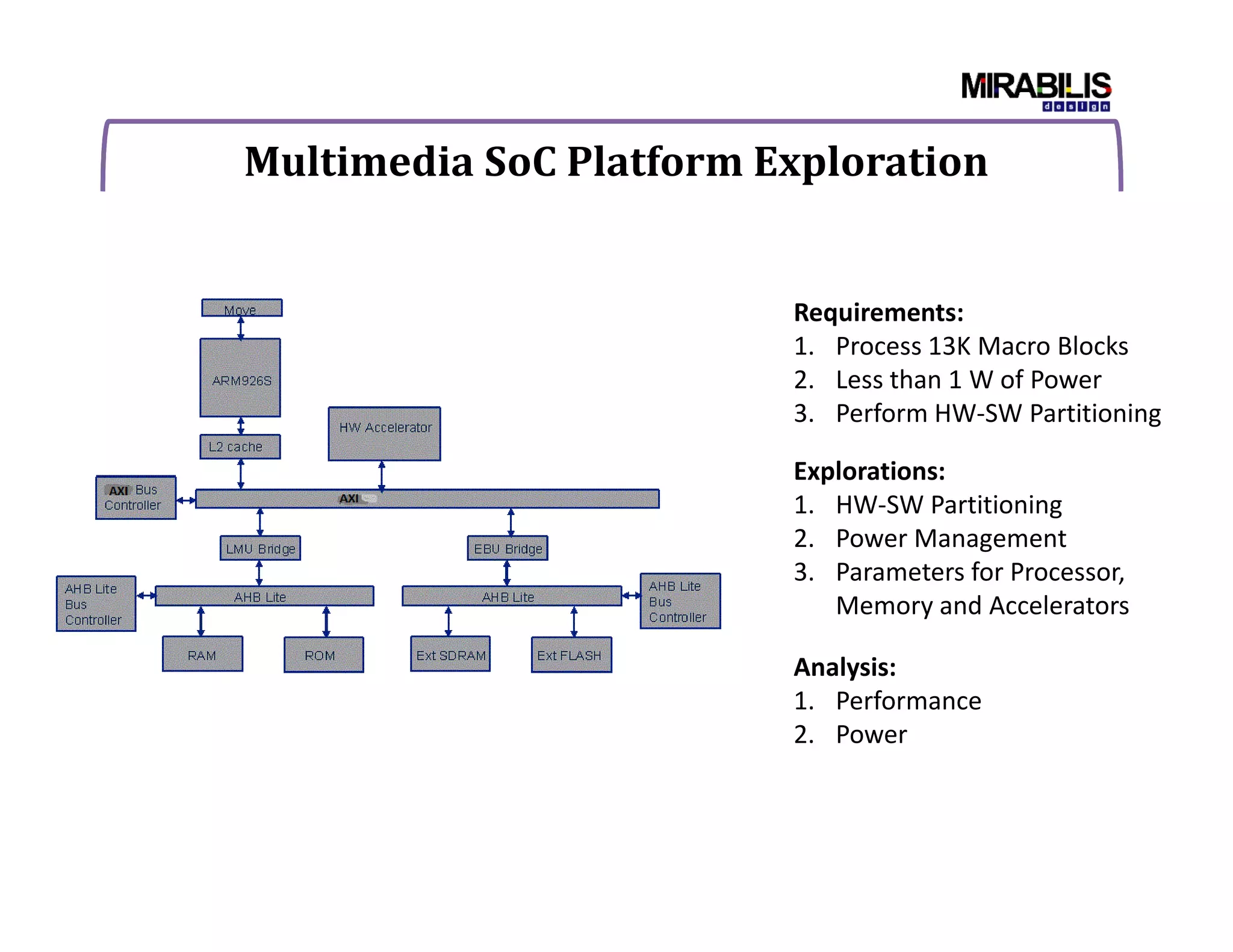

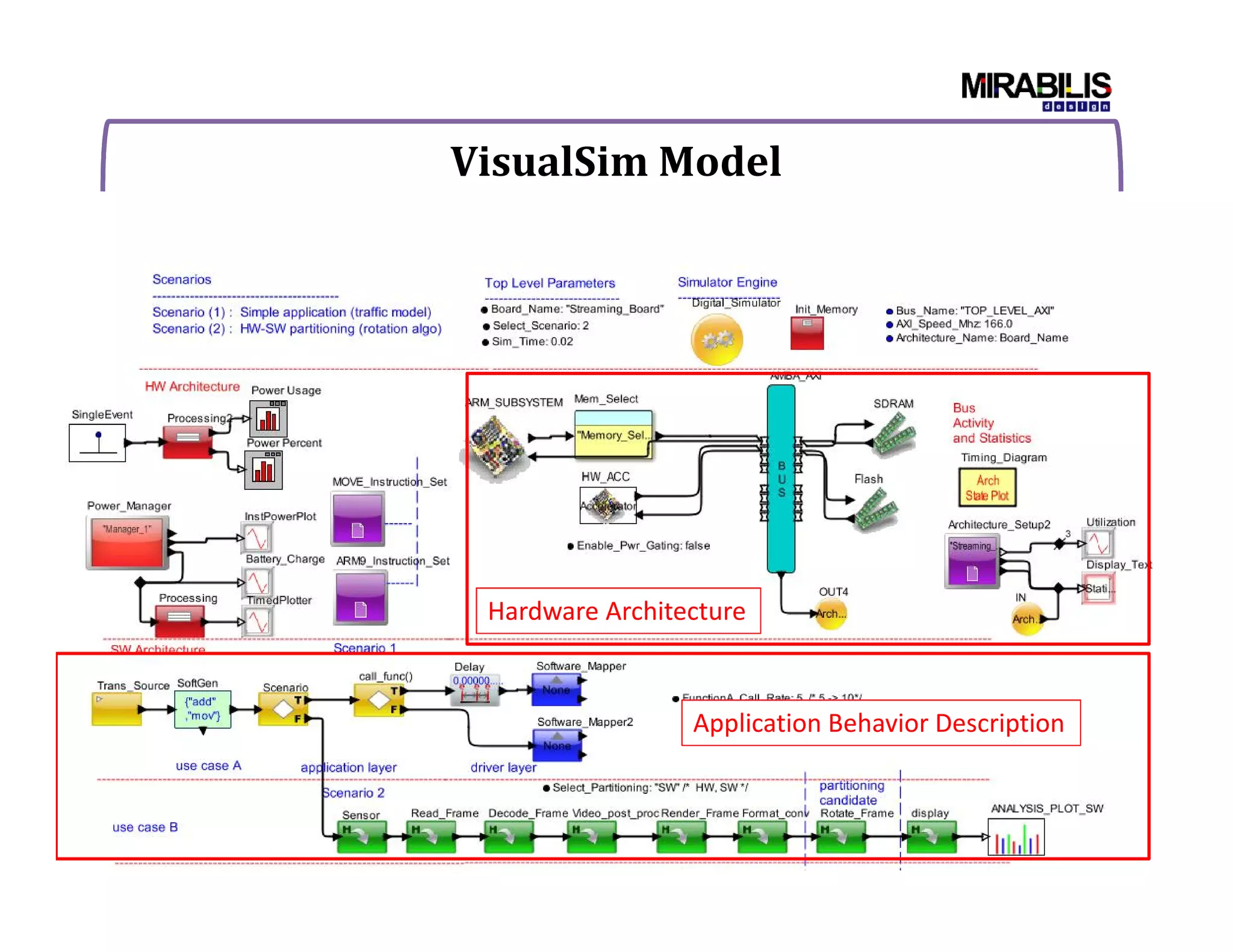

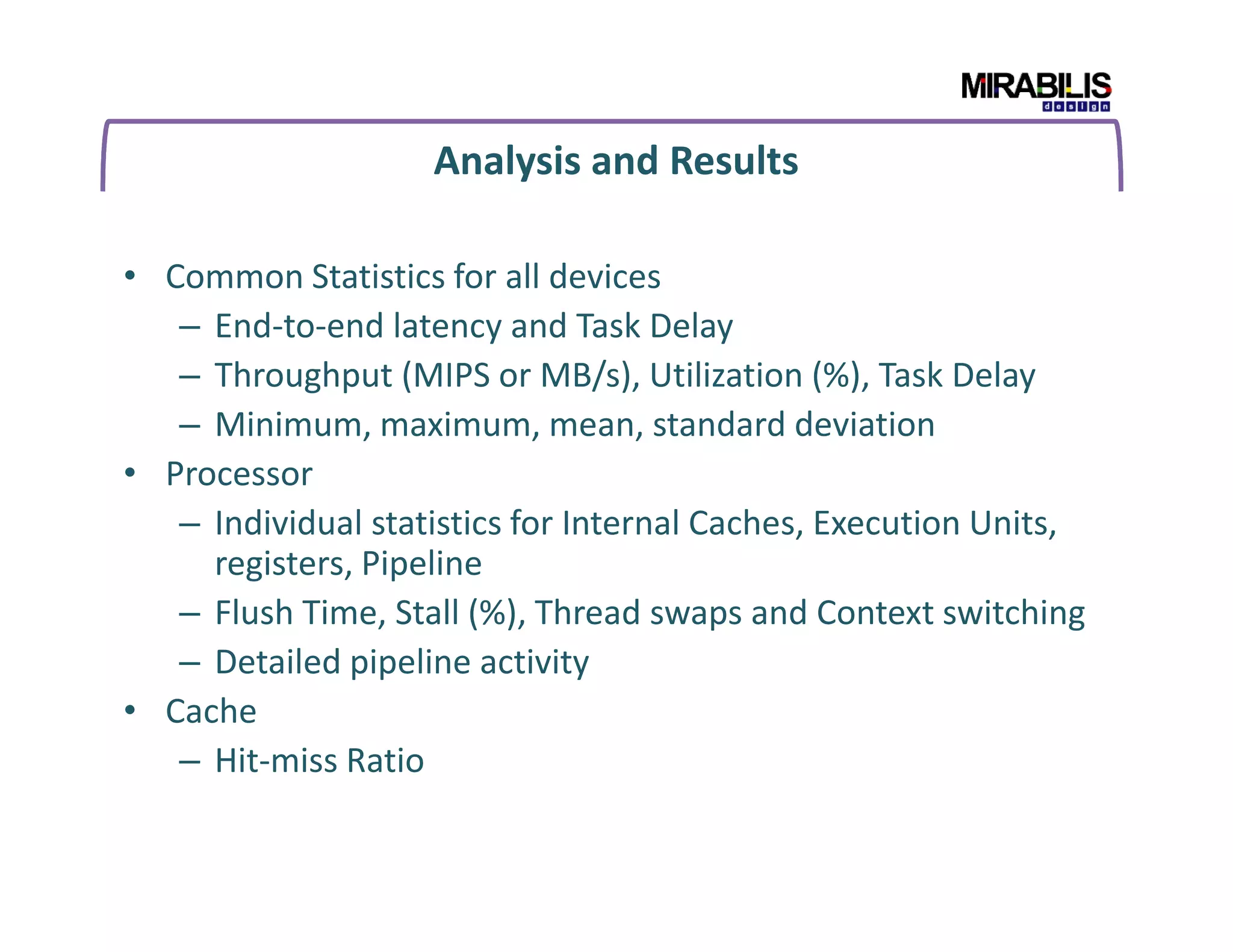

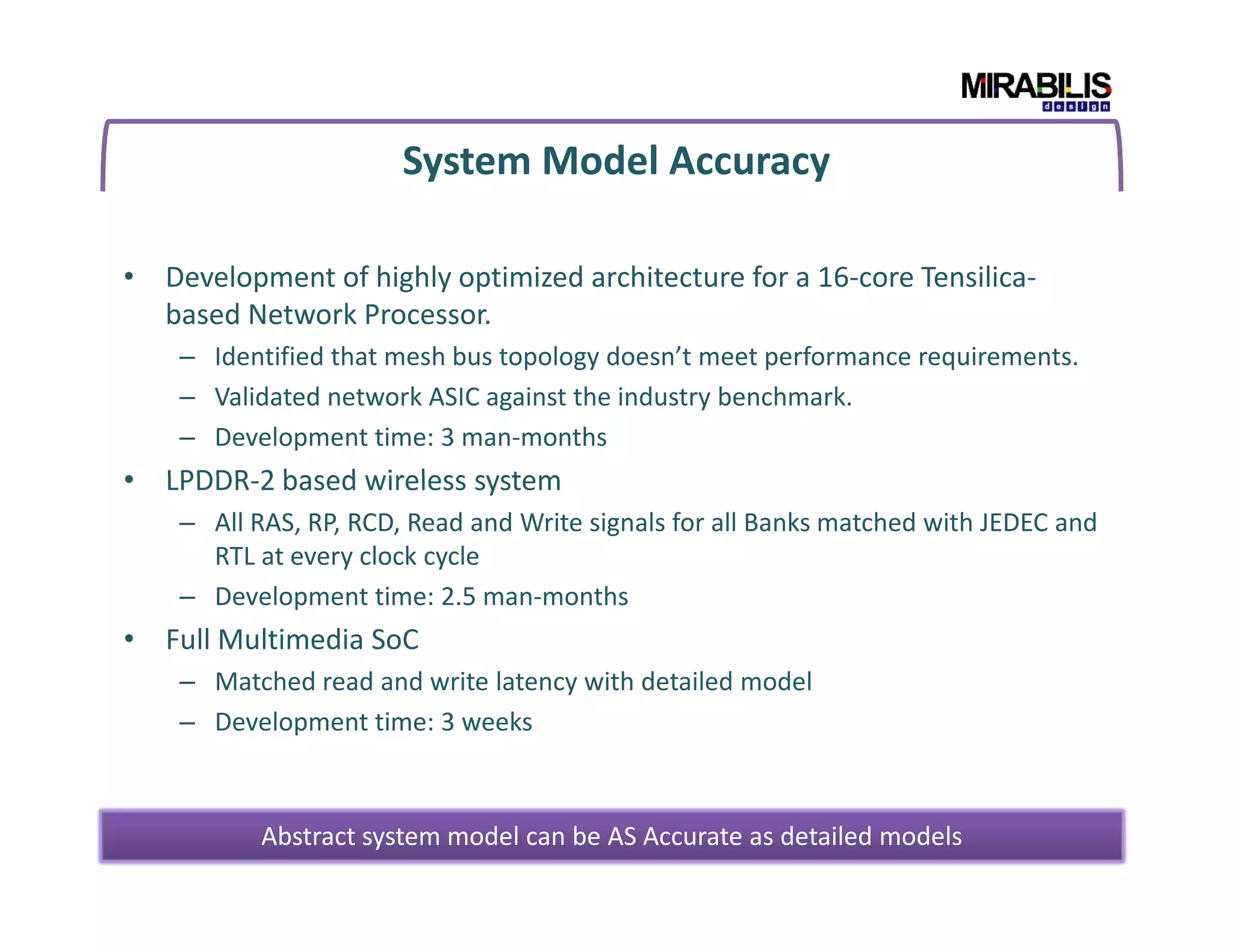

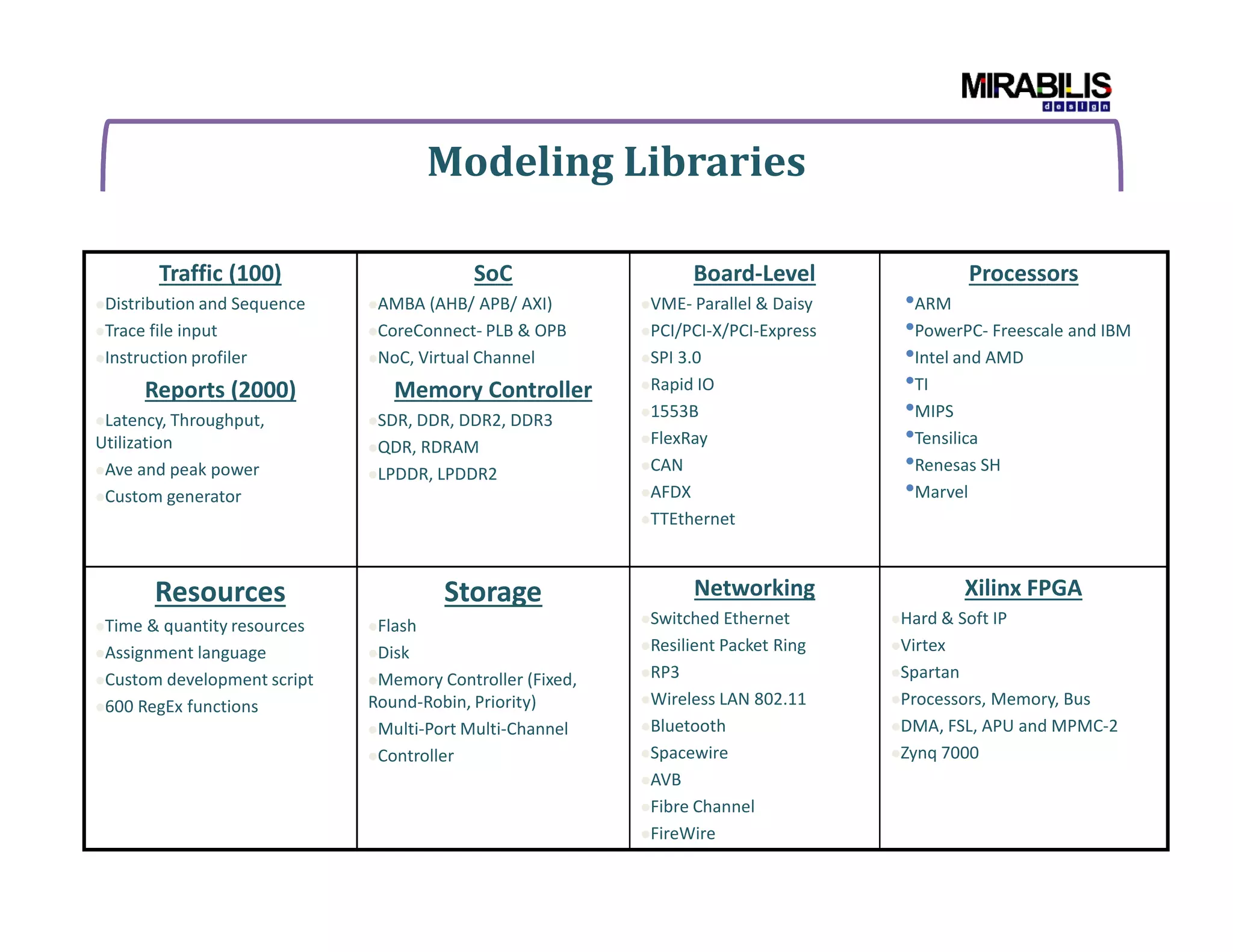

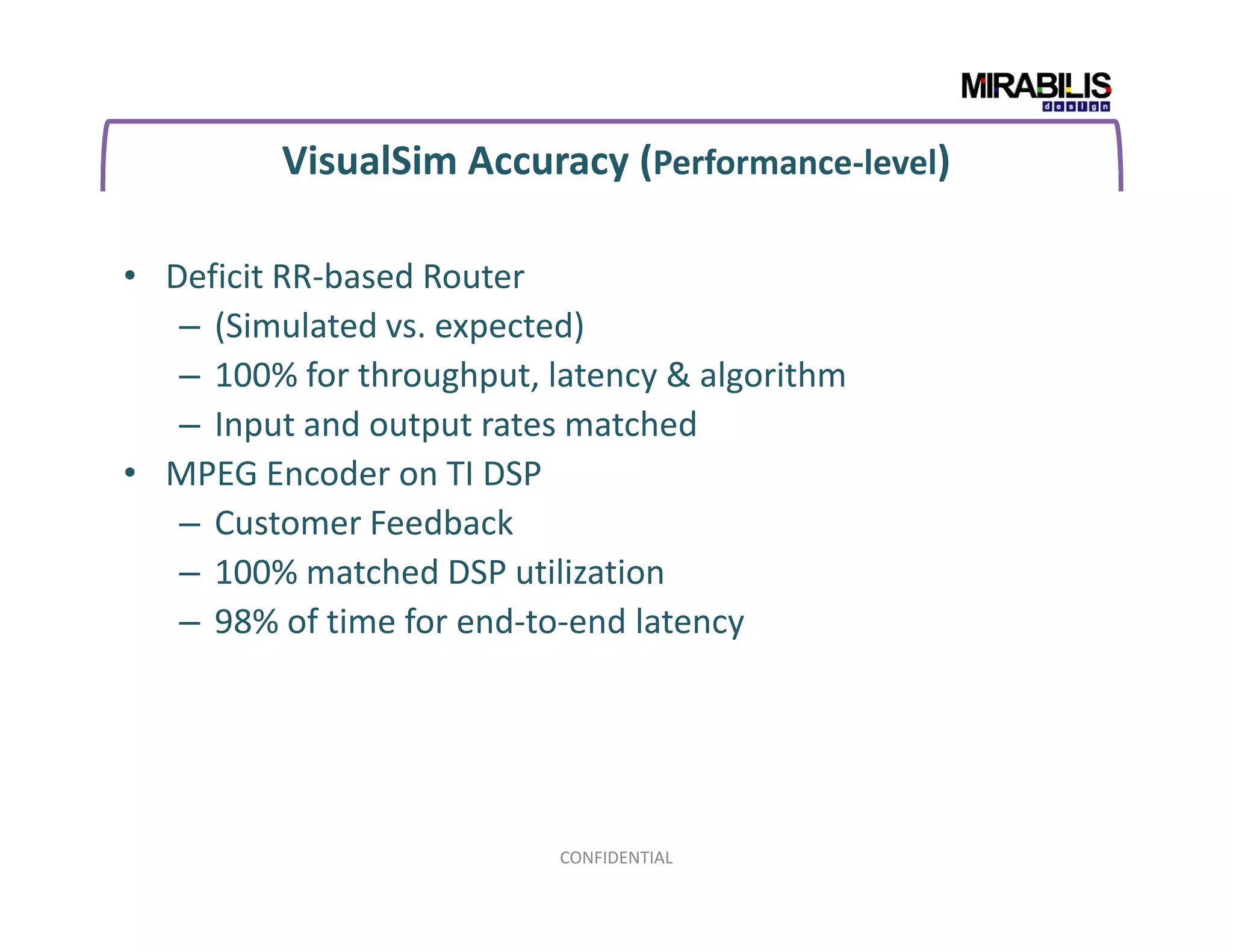

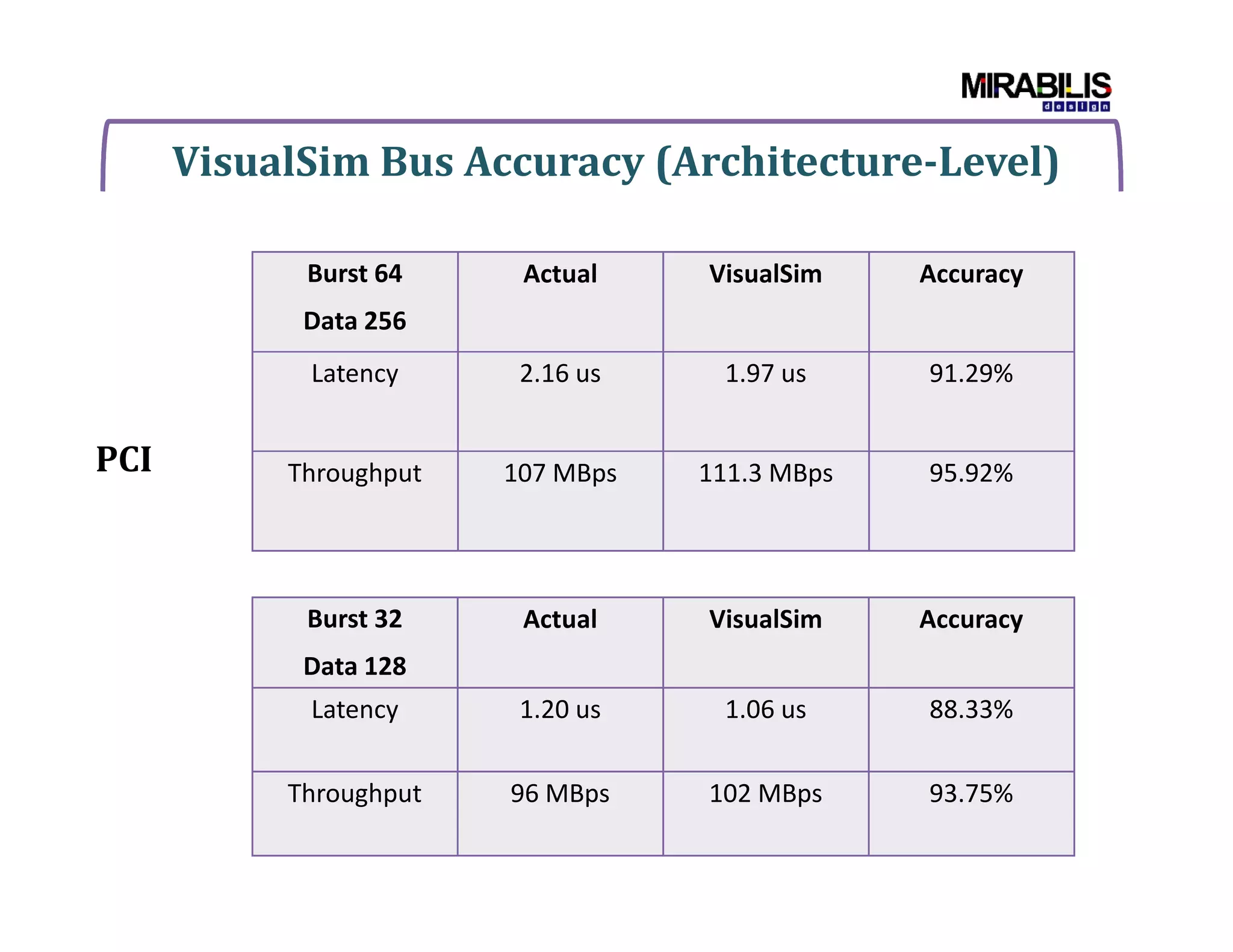

The webinar hosted by Ranjith K. R. from Mirabilis Design focuses on utilizing VisualSim for innovative architecture in system-level modeling and simulation, highlighting its tools for performance and power analysis. Key benefits include graphical modeling capabilities, extensive libraries for hardware and software integration, and the ability to perform accurate bottleneck assessments and dynamic behavior simulations. The session emphasizes early design exploration, enabling users to validate their architecture against performance requirements efficiently.