The document describes various digital logic circuits including flip-flops, counters, and serial-parallel converters. It provides code examples in Verilog and VHDL for implementing D flip-flops, JK flip-flops, T flip-flops, SR flip-flops, up/down counters, and serial-in serial-out, serial-in parallel-out, parallel-in parallel-out converters. The examples show how to describe the logic functions and simulate the behavior of basic digital circuits using hardware description languages.

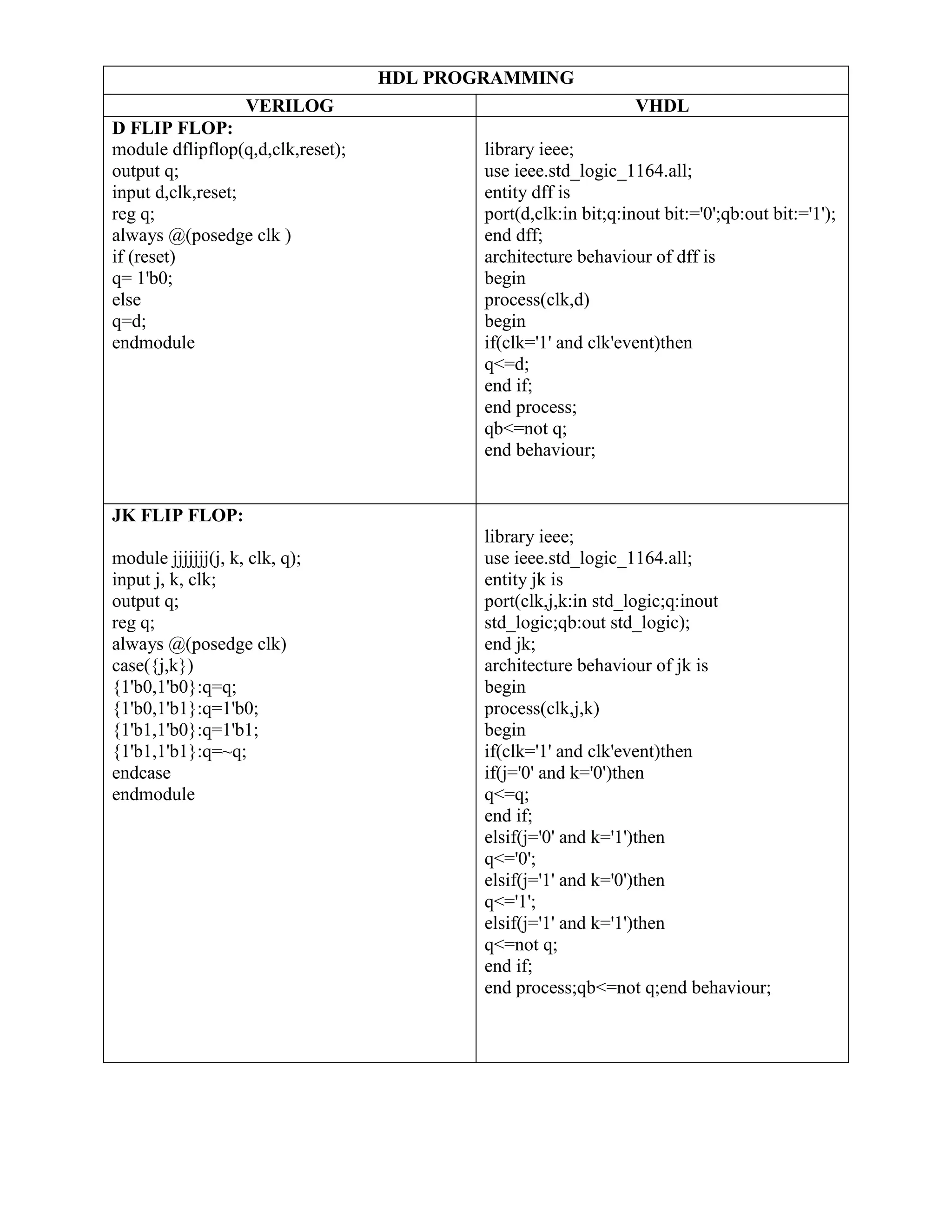

![SERIAL IN PARALLEL OUT : module sipo( din ,clk ,reset ,dout ); output [3:0] dout ; wire [3:0] dout ; input din ; wire din ; input clk ; wire clk ; input reset ; wire reset ; reg [3:0]s; always @ (posedge (clk)) begin if (reset) s = 0; else begin s[3] = din; s[2] = s[3]; s[1] = s[2]; s[0] = s[1]; end end assign dout = s; endmodule library ieee; use ieee.std_logic_1164.all; entity sipo is port(clk:in bit;s:in bit; q:inout bit_vector(3 downto 0)); end sipo; architecture sipo_pgm of sipo is component dff1 is port(d,clk:in bit; q:out bit); end component; begin d1:dff1 port map(s,clk,q(3)); d2:dff1 port map(q(3),clk,q(2)); d3:dff1 port map(q(2),clk,q(1)); d4:dff1 port map(q(1),clk,q(0)); end sipo_pgm; entity dff1 is port(d,clk:in bit; q:out bit); end dff1; architecture dff_pgm of dff1 is begin process(d,clk) begin if(clk='1' and clk'event)then q<=d; end if; end process; end dff_pgm; PARELLEL IN PARELLEL OUT: module pppiiiooo(sout,sin,clk); output [3:0]sout; input [3:0]sin; input clk; dflipflop u1(sout[0],sin[0],clk); dflipflop u2(sout[1],sin[1],clk); dflipflop u3(sout[2],sin[2],clk); dflipflop u4(sout[3],sin[3],clk); endmodule library ieee; use ieee.std_logic_1164.all; entity pipo is port(clk:in bit; s:in bit_vector(3 downto 0); q:inout bit_vector(3 downto 0)); end pipo; architecture pipo_pgm of pipo is component dff1 is port(d,clk:in bit;](https://image.slidesharecdn.com/hdlprogramming-3-230106043925-3f047779/75/HDL-PROGRAMMING-3-pdf-4-2048.jpg)

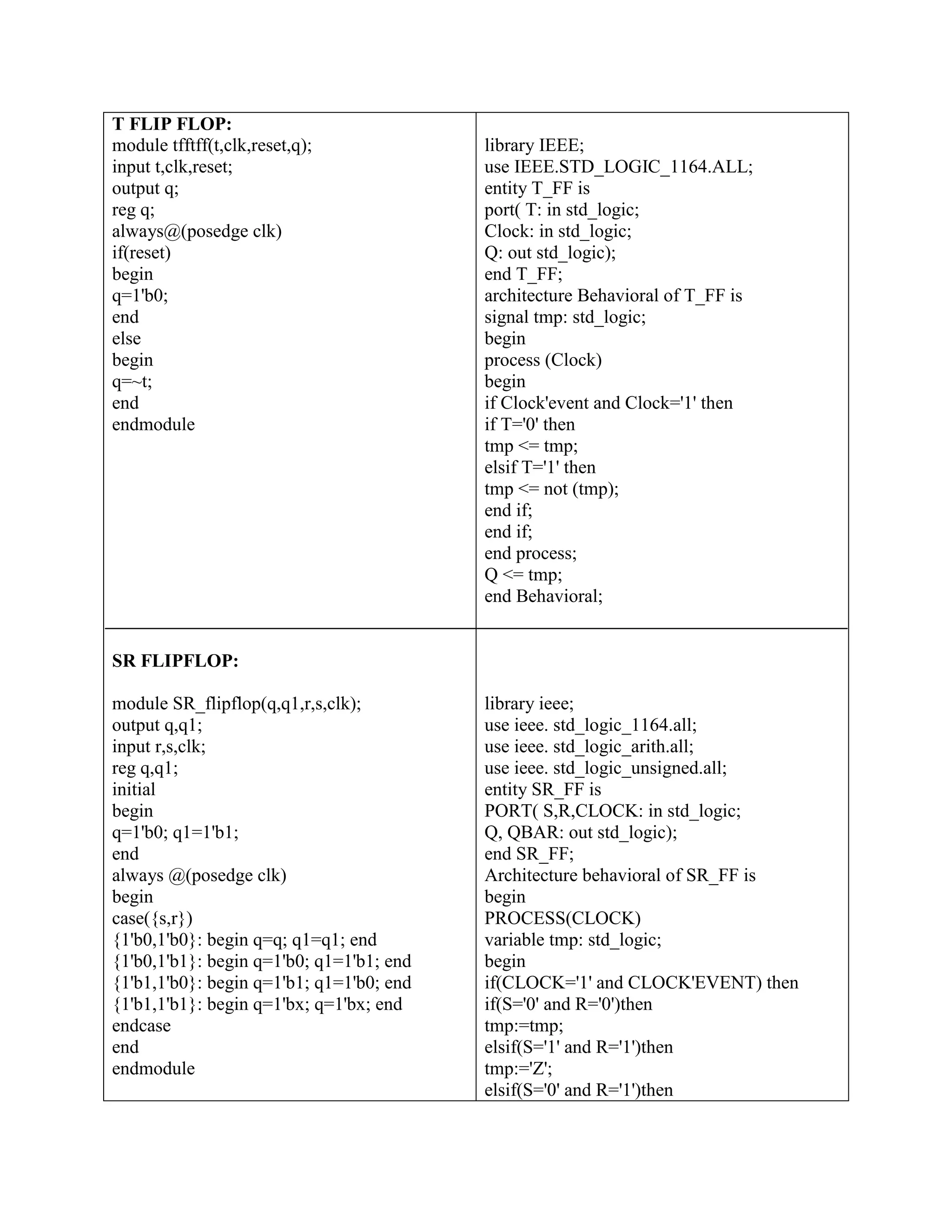

![module dflipflop(q,d,clk,reset); output q; input d,clk,reset; reg q; always @(posedge clk ) if (reset) q= 1'b0; else q=d; endmodule PARALLEL IN SERIAL OUT: module pppiiissssii(clk,rst,a,out); input clk,rst; input [3:0]a; output out; reg out; reg [3:0]temp; always@(posedge clk,posedge rst) begin if(rst==1'b1) begin out=1'b0; temp=a; end else begin out=temp[0]; temp=temp>>1'b1; end end endmodule q:out bit); end component; begin d1:dff1 port map(s(0),clk,q(0)); d2:dff1 port map(s(1),clk,q(1)); d3:dff1 port map(s(2),clk,q(2)); d4:dff1 port map(s(3),clk,q(3)); end pipo_pgm; entity dff1 is port(d,clk:in bit; q:out bit); end dff1; architecture dff_pgm of dff1 is begin process(d,clk) begin if(clk='1' and clk'event)then q<=d; end if; end process; end dff_pgm; library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; entity piso is port(a:in bit_vector(3 downto 0); s,clk:bit; y:out bit); end piso; architecture piso_pgm of piso is signal q0,x,b,c,q1,d,e,f,q2,g,h,i,sb:bit; component dff1 is port(d,clk:in bit; q:out bit); end component; begin sb<=not (s); d1:dff1 port map(a(0),clk,q0); x<=s and q0; b<=(sb and a(1)); c<=x or b; d2:dff1 port map(c,clk,q1);](https://image.slidesharecdn.com/hdlprogramming-3-230106043925-3f047779/75/HDL-PROGRAMMING-3-pdf-5-2048.jpg)

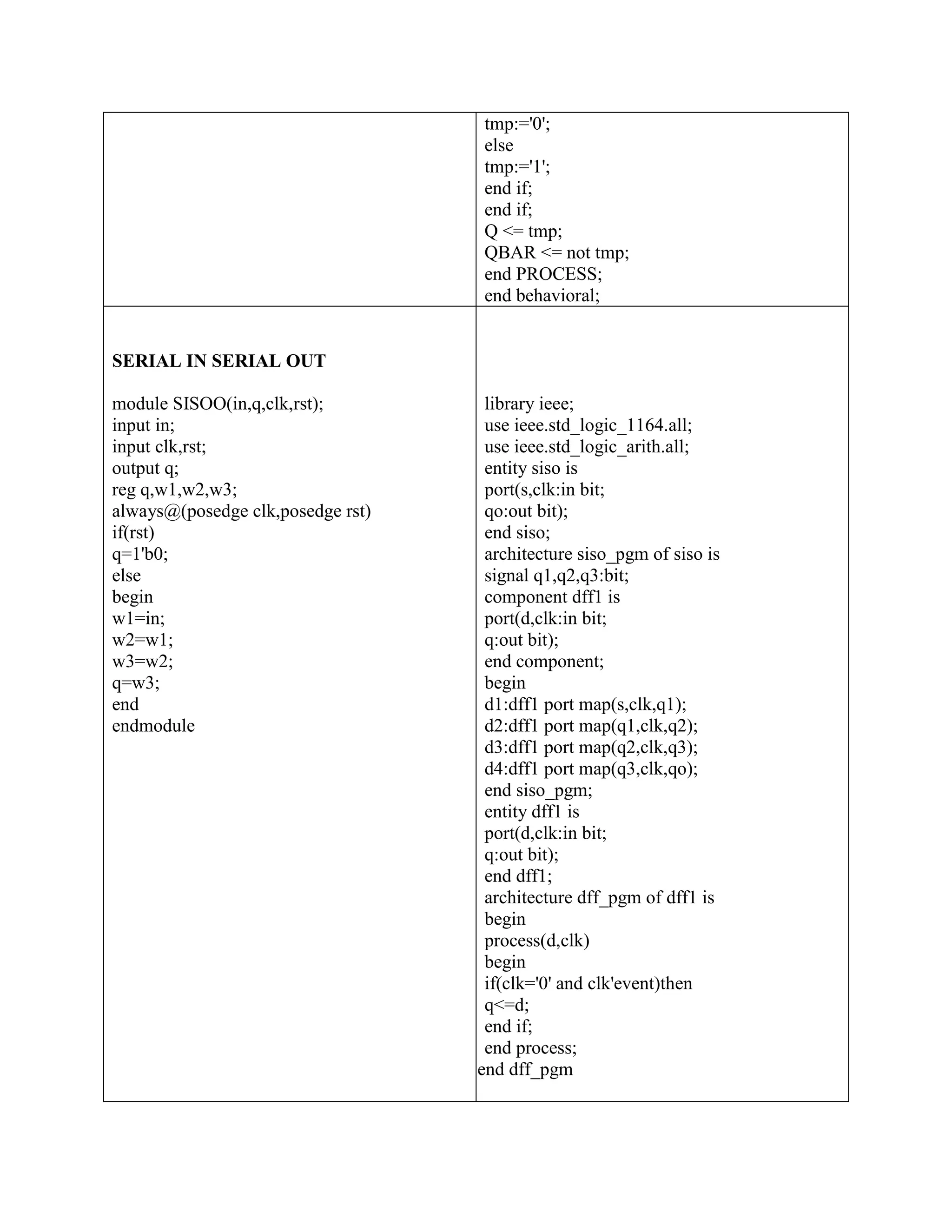

![d<=q1 and s; e<=(sb and a(2)); f<=d or e; d3:dff1 port map(f,clk,q2); g<=q2 and s; h<=(sb and a(3)); i<=g or h; d4:dff1 port map(i,clk,y); end piso_pgm; entity dff1 is port(d,clk:in bit; q:out bit); end dff1; architecture dff_pgm of dff1 is begin process(d,clk) begin if(clk='0' and clk'event)then q<=d; end if; end process; end dff_pgm; UPDOWN COUNTER: module uodown(out,x,clk,data,reset ); input [3:0]data; input x,clk,reset; output[3:0]out; reg[3:0]out; always@(posedge clk) if(reset==1) out=3'b000; else if(x==1) out=out+1; else out=out-1; endmodule library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity Counter_VHDL is port( Number: in std_logic_vector(0 to 3); Clock: in std_logic; Load: in std_logic; Reset: in std_logic; Direction: in std_logic; Output: out std_logic_vector(0 to 3) ); end Counter_VHDL; architecture Behavioral of Counter_VHDL is signal temp: std_logic_vector(0 to 3); begin process(Clock,Reset) begin if Reset='1' then temp <= "0000"; elsif ( Clock'event and Clock='1') then](https://image.slidesharecdn.com/hdlprogramming-3-230106043925-3f047779/75/HDL-PROGRAMMING-3-pdf-6-2048.jpg)

![UPCOUNTER module counter (C, ALOAD, D, Q); input C, ALOAD; input [3:0] D; output [3:0] Q; reg [3:0] tmp; always @(posedge C or posedge ALOAD) begin if (ALOAD) tmp = D; else tmp = tmp + 1'b1; end assign Q = tmp; endmodule if Load='1' then temp <= Number; elsif (Load='0' and Direction='0') then temp <= temp + 1; elsif (Load='0' and Direction='1') then temp <= temp - 1; end if; end if; end process; Output <= temp; end Behavioral; library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity vhdl_binary_counter is port(C, CLR : in std_logic; Q : out std_logic_vector(3 downto 0)); end vhdl_binary_counter; architecture bhv of vhdl_binary_counter is signal tmp: std_logic_vector(3 downto 0); begin process (C, CLR) begin if (CLR=’1′) then tmp <= "0000"; elsif (C’event and C=’1′) then tmp <= tmp + 1; end if; end process; Q <= tmp; end bhv;](https://image.slidesharecdn.com/hdlprogramming-3-230106043925-3f047779/75/HDL-PROGRAMMING-3-pdf-7-2048.jpg)

![DOWN COUNTER module counter (C, S, Q); input C, S; output [3:0] Q; reg [3:0] tmp; always @(posedge C) begin if (S) tmp = 4'b1111; else tmp = tmp - 1'b1; end assign Q = tmp; endmodule library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity counter is port(C, S : in std_logic; Q : out std_logic_vector(3 downto 0)); end counter; architecture archi of counter is signal tmp: std_logic_vector(3 downto 0); begin process (C) begin if (C'event and C='1') then if (S='1') then tmp <= "1111"; else tmp <= tmp - 1; end if; end if; end process; Q <= tmp; end archi;](https://image.slidesharecdn.com/hdlprogramming-3-230106043925-3f047779/75/HDL-PROGRAMMING-3-pdf-8-2048.jpg)