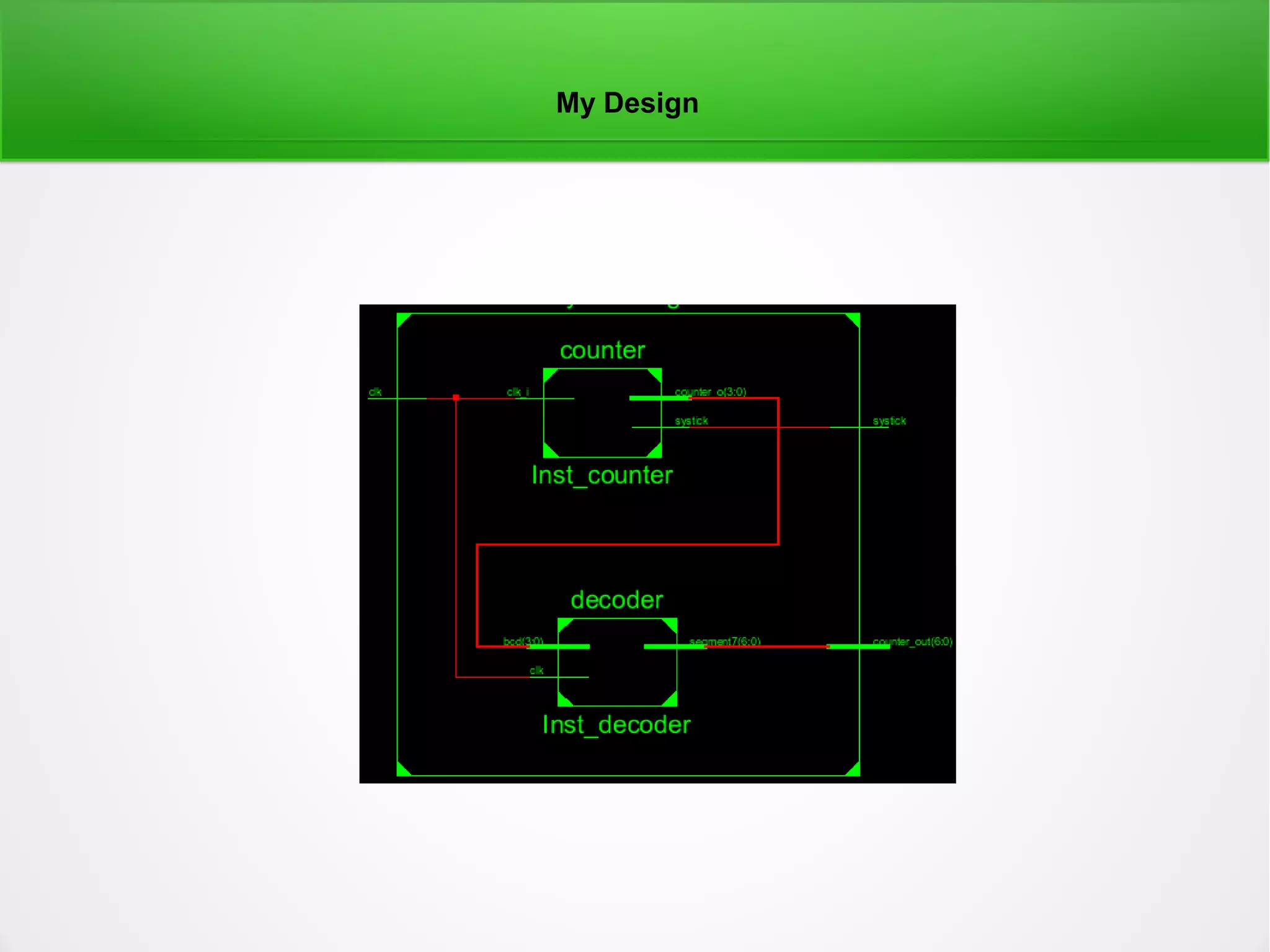

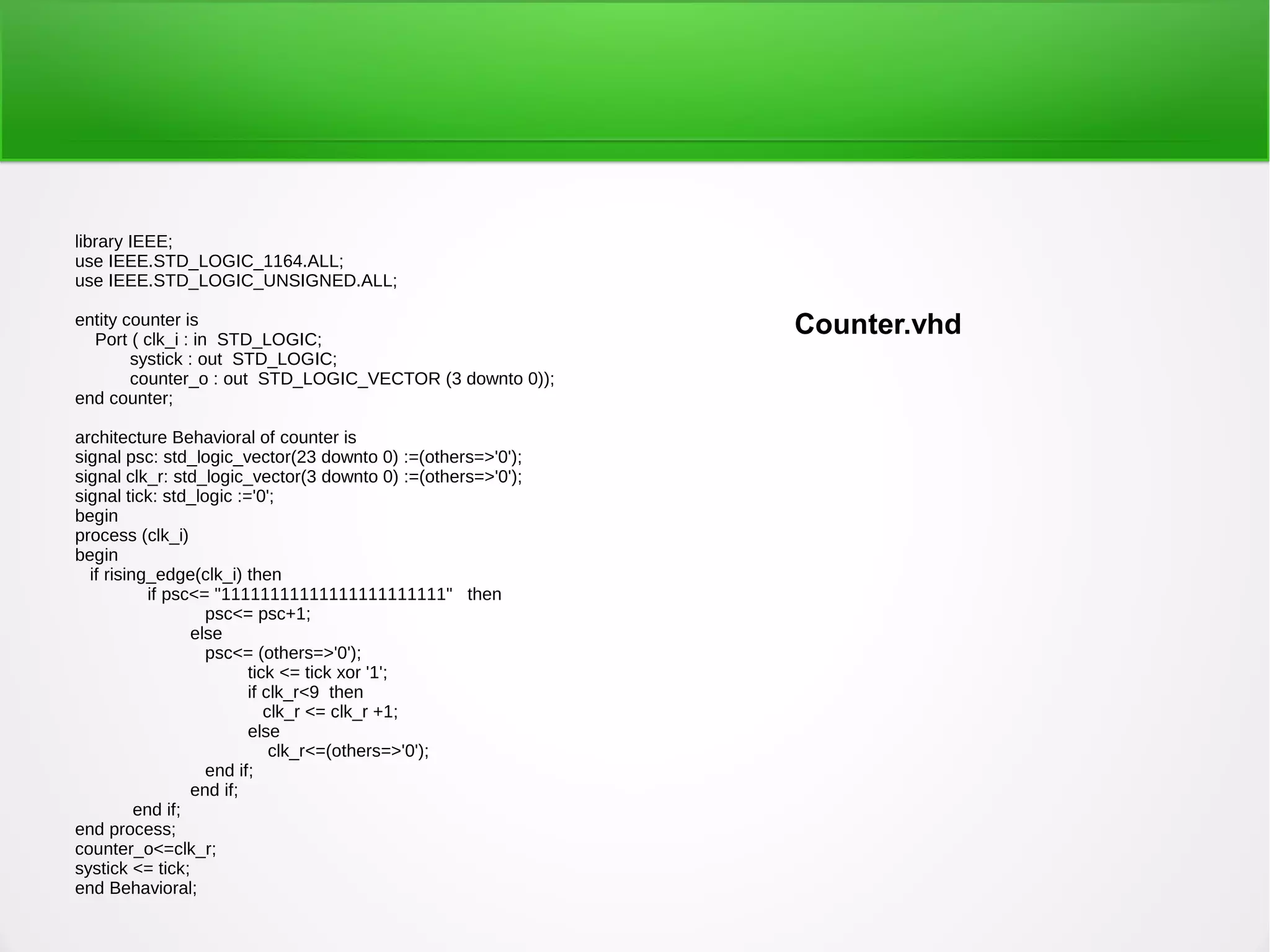

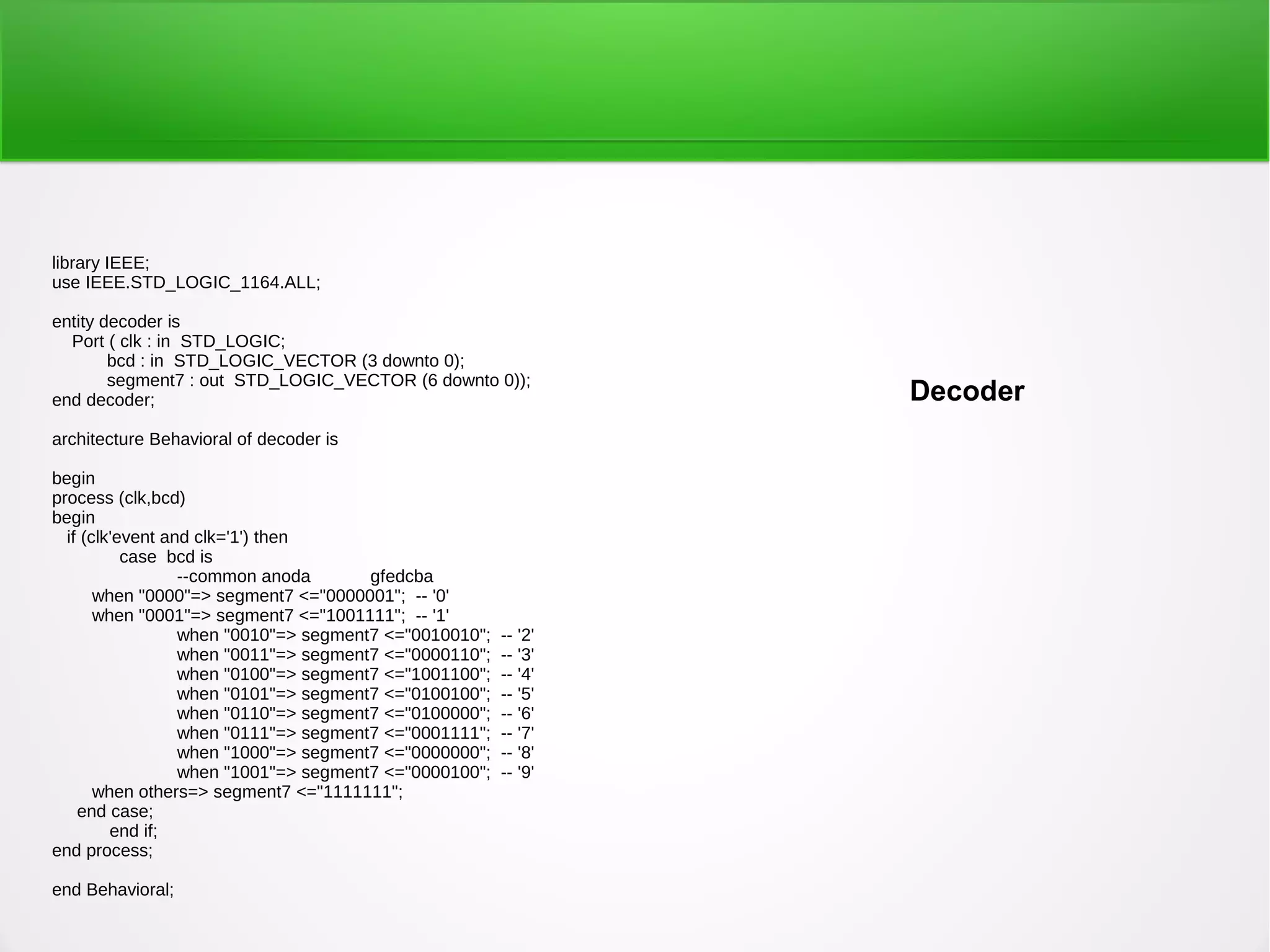

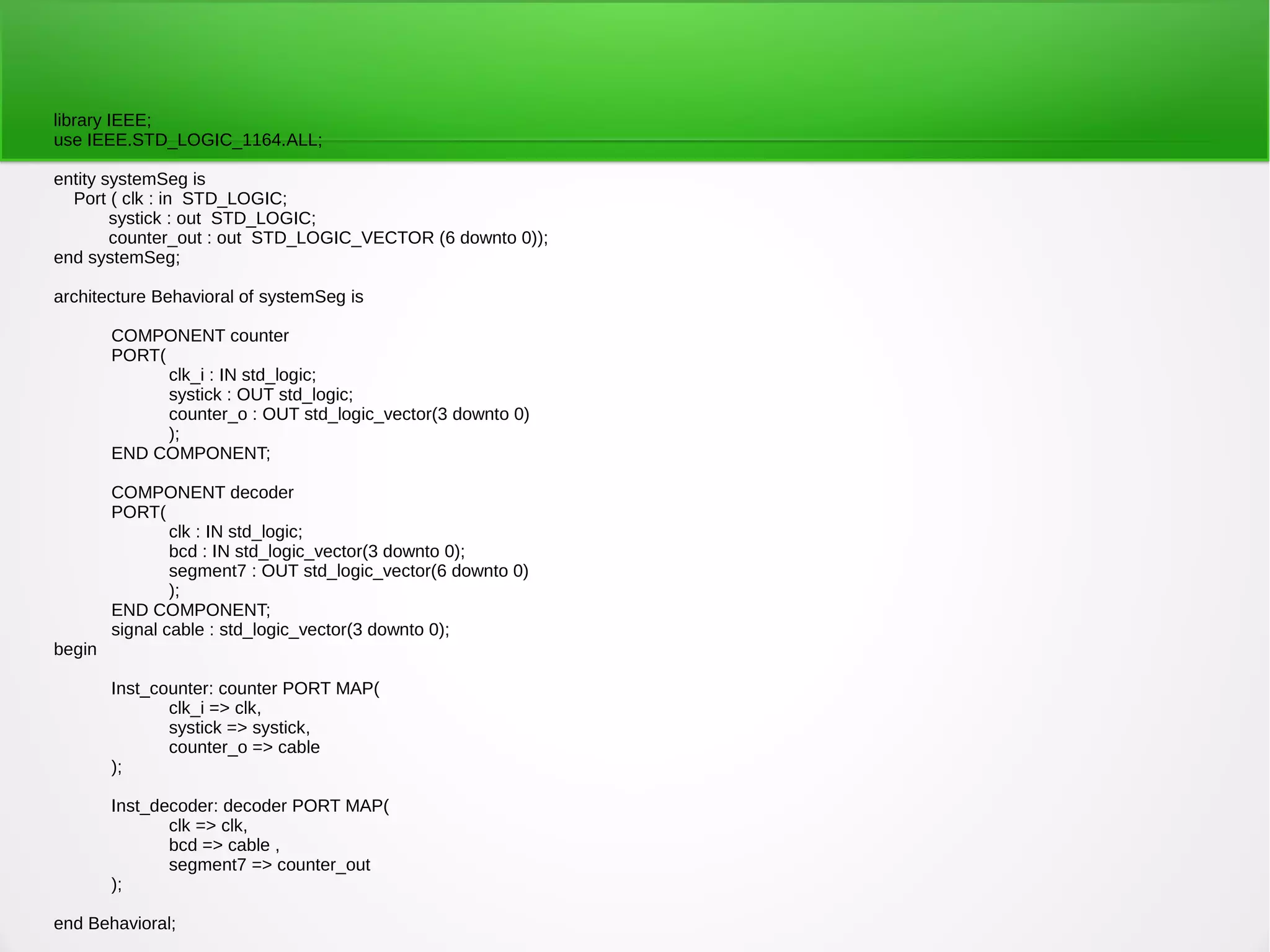

This document describes a design for a counter seven segment display using an FPGA. The author implemented a counter component and a decoder component, then wired them together in a top-level systemSeg entity using port mapping. The counter counts from 0 to 9 and outputs a 4-bit binary coded decimal value. The decoder converts the 4-bit input to a 7-segment display output based on a case statement. The author notes that port mapping is useful for wiring components together in HDL and that designs need to be synchronous with a clock.