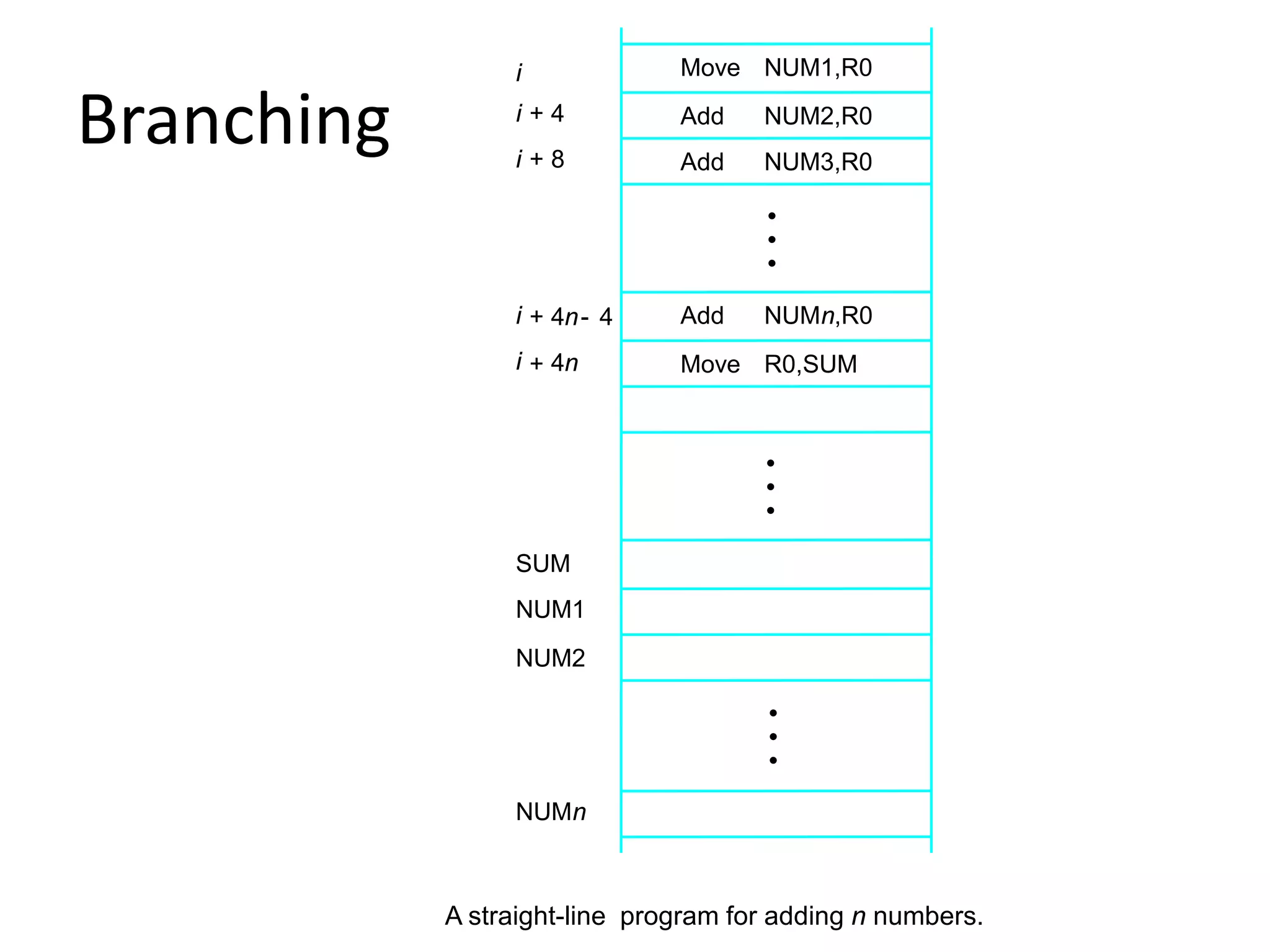

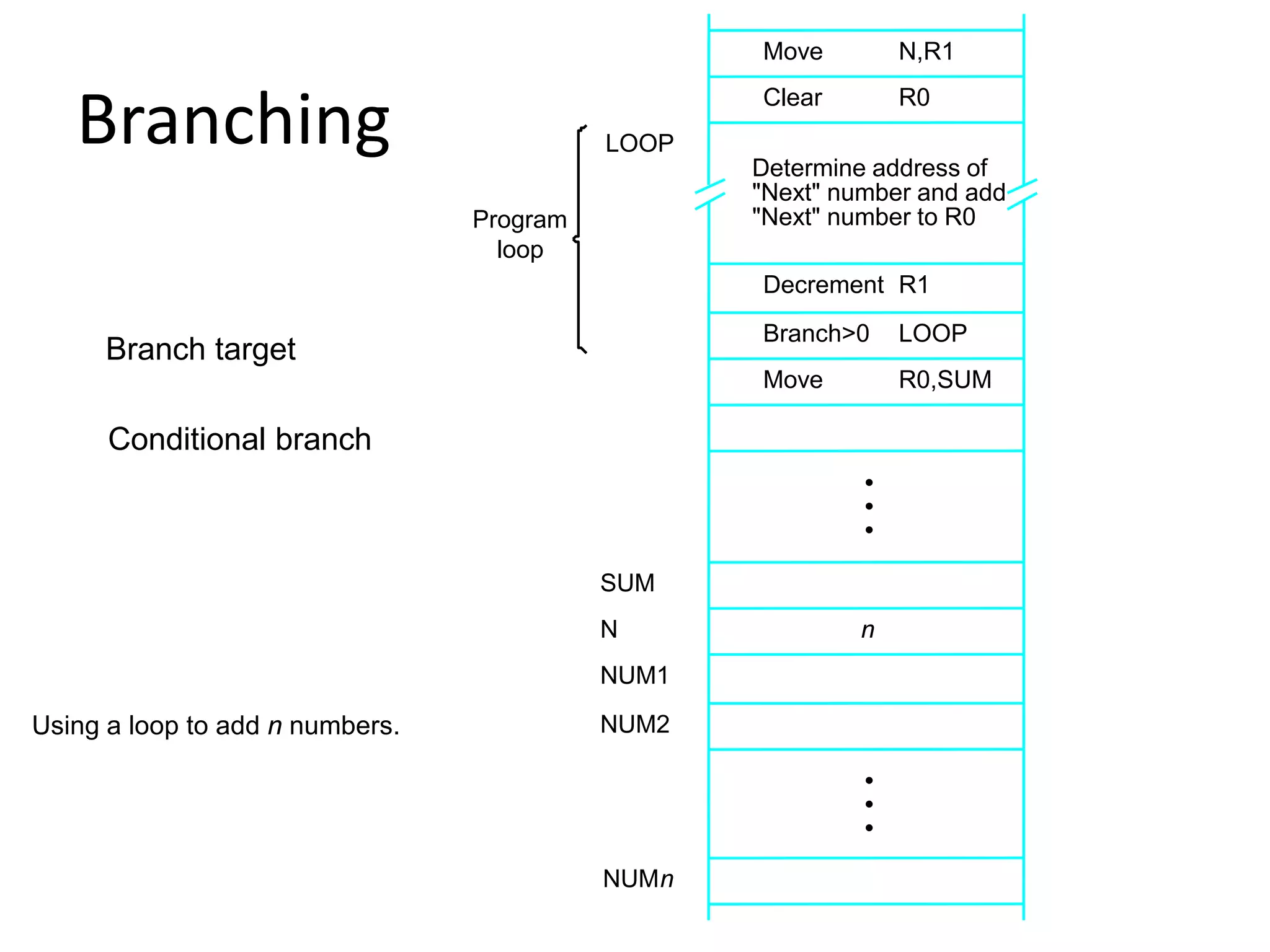

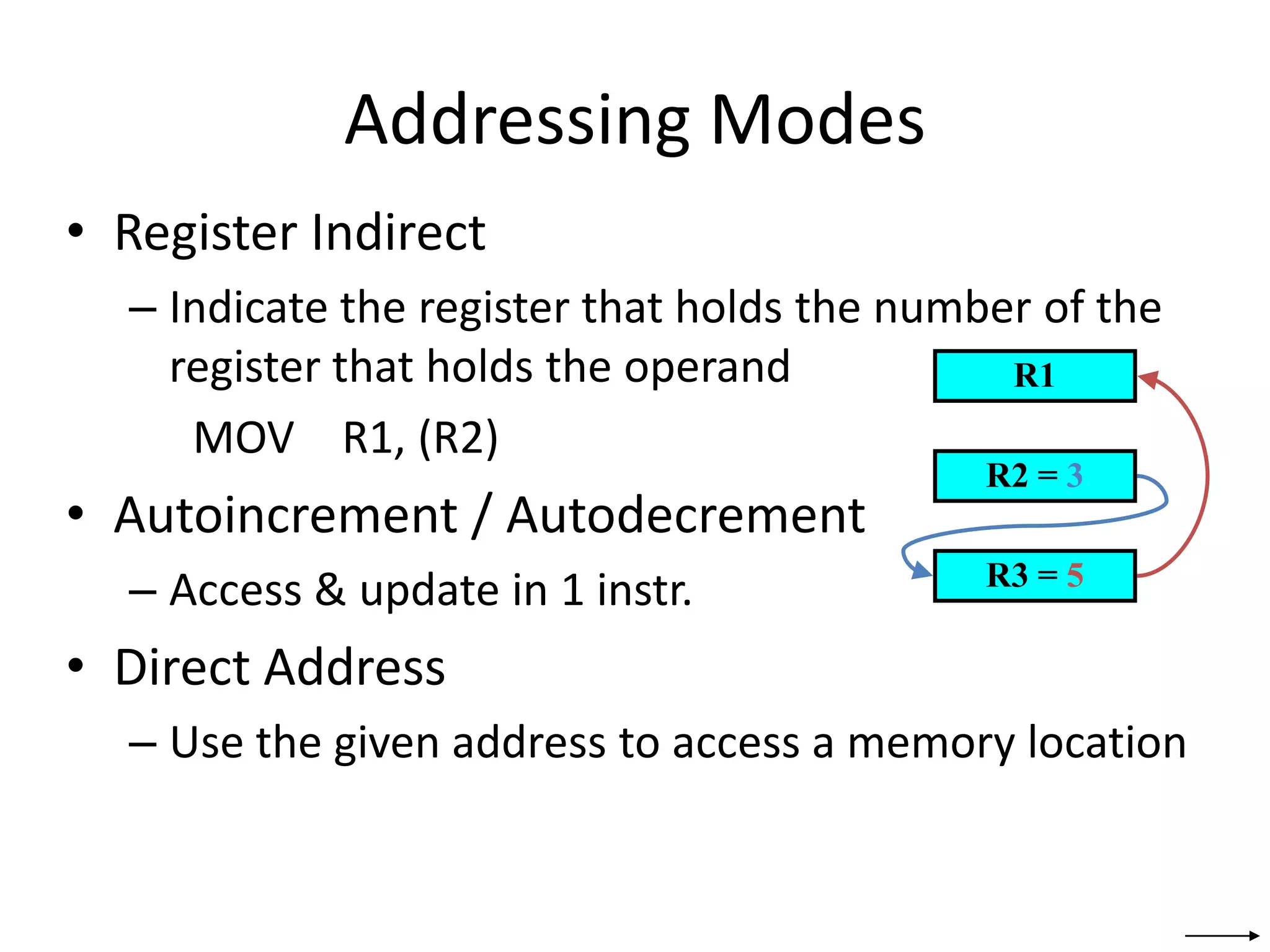

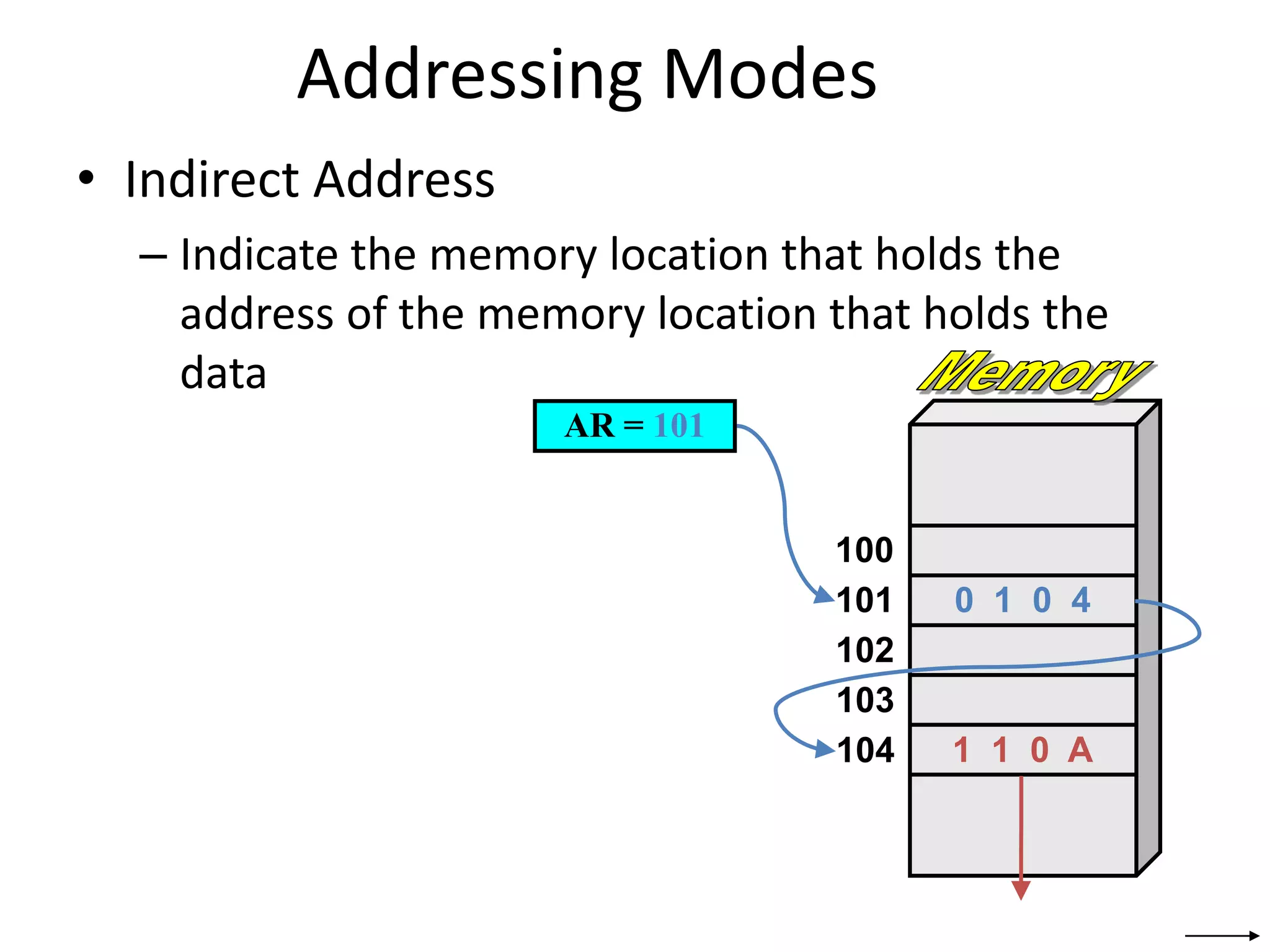

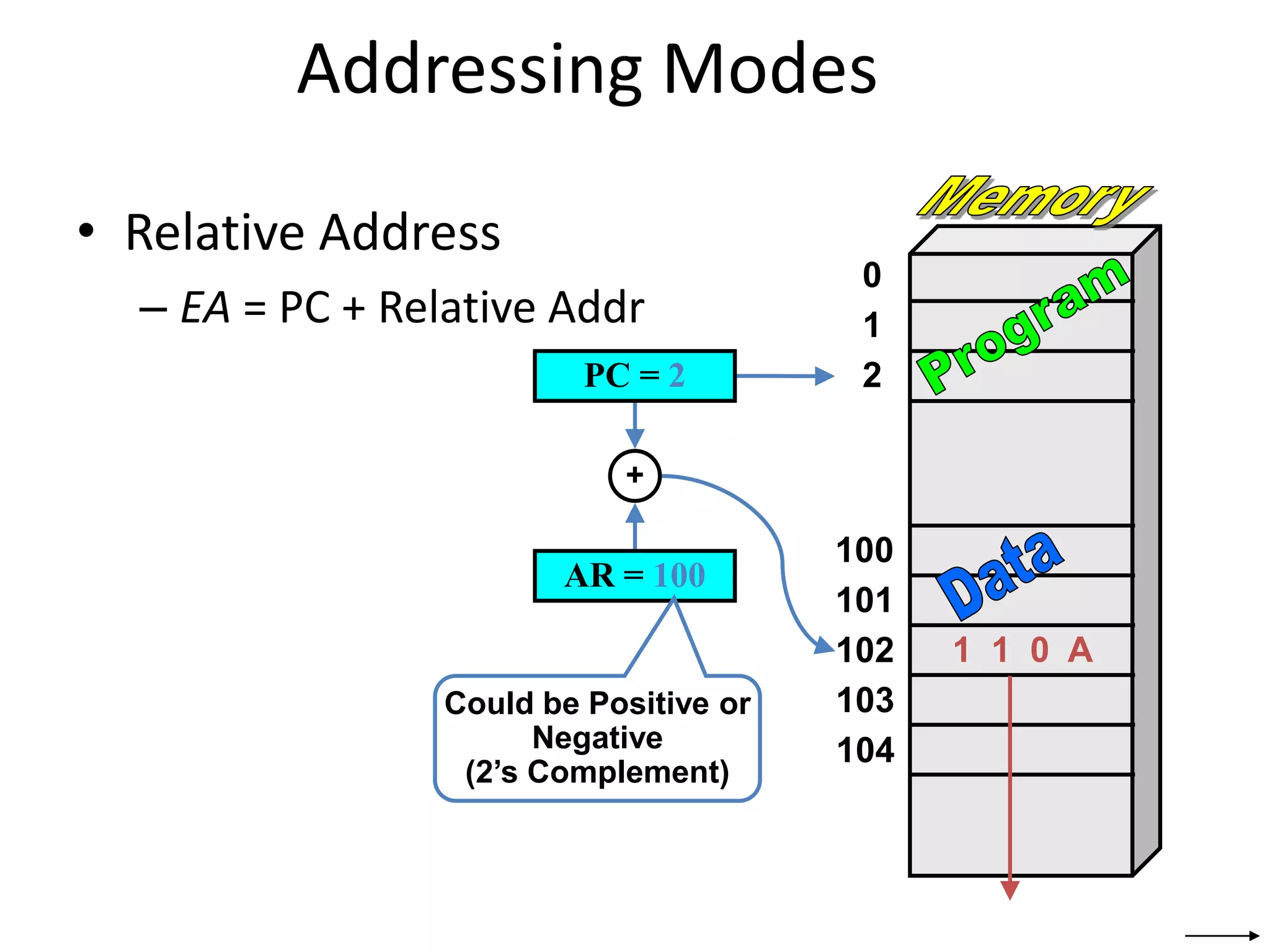

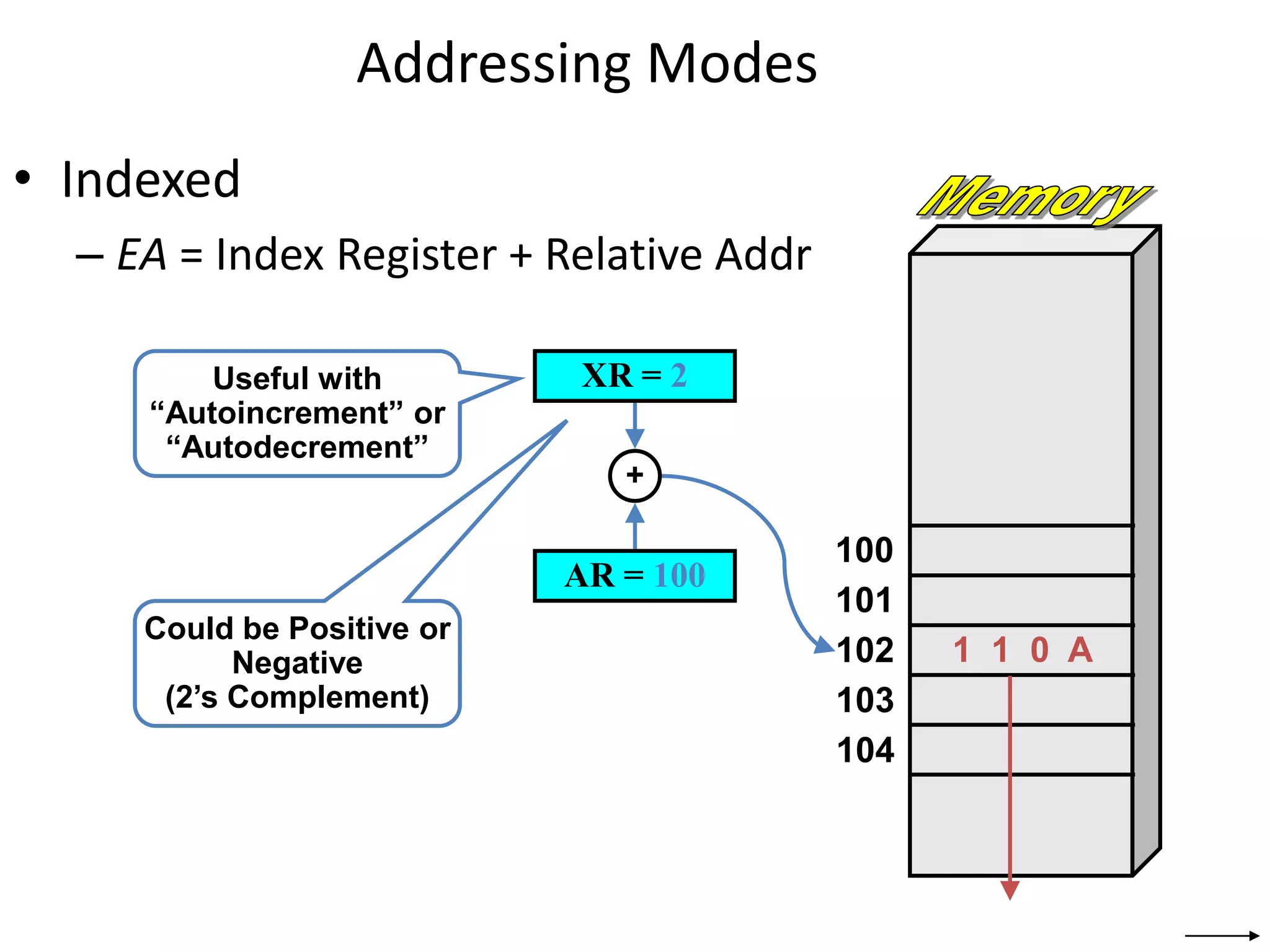

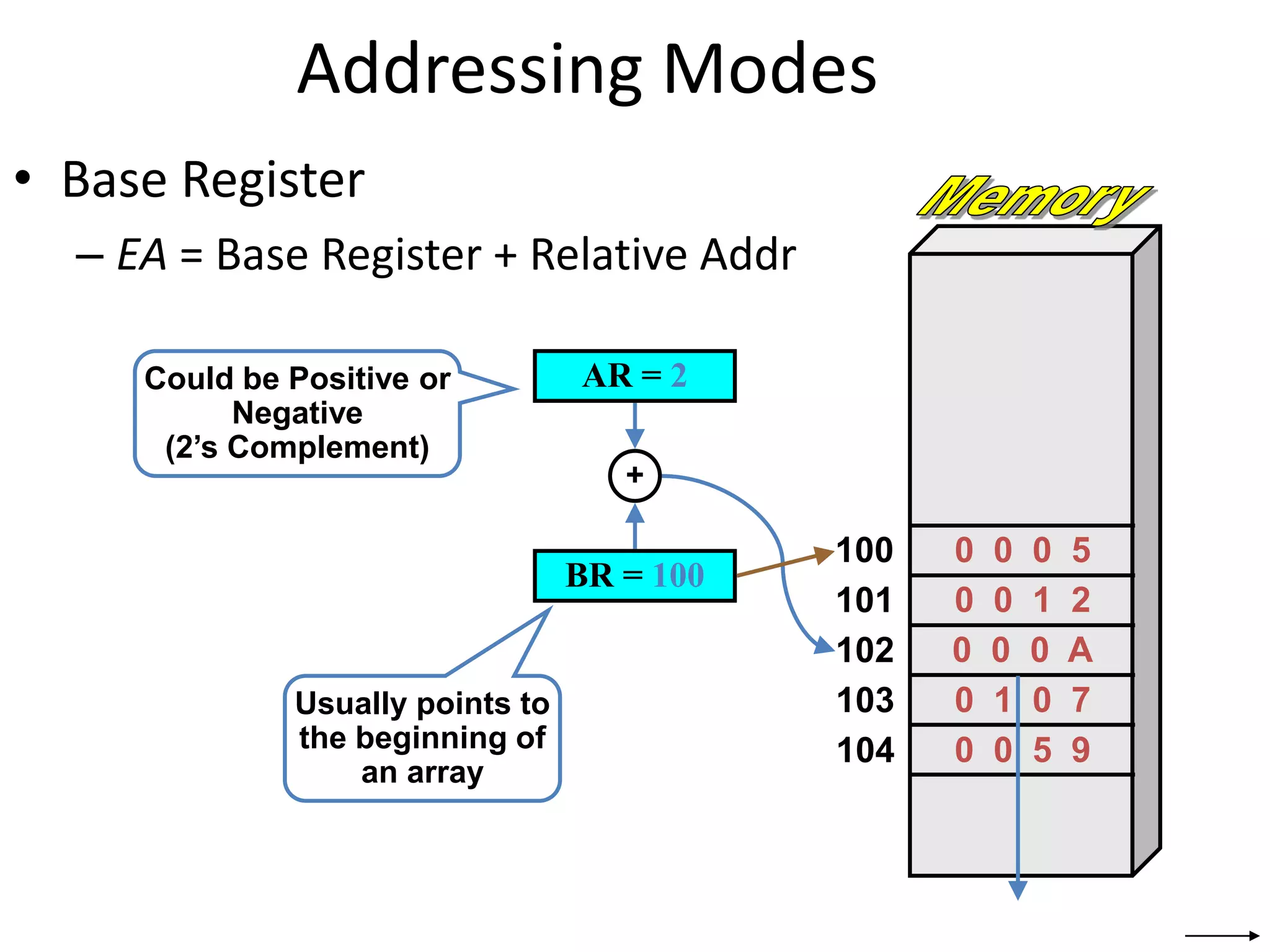

The document discusses different instruction execution methods like straight-line sequencing and branching. It also covers addressing modes which specify how the location of an operand is represented in an instruction, including immediate, register, absolute/direct, indirect, indexed, relative, and auto-increment/decrement modes. Indexing allows accessing data in arrays by adding an index register or offset to a base register pointing to the array start. Relative addressing computes addresses as offsets from the program counter for branches.

![Instruction Execution and Straight-Line Sequencing R0,C B,R0 A,R0 Move i + 8 Begin execution here Move i Contents Address C B A the program Data for segment program 3-instruction Add i + 4 A program for C ← [Α] + [Β]. Assumptions: - One memory operand per instruction - 32-bit word length - Memory is byte addressable - Full memory address can be directly specified in a single-word instruction Two-phase procedure -Instruction fetch -Instruction execute](https://image.slidesharecdn.com/programexecutionstraightlinesequenceandbranching-210316075934/75/Program-execution-straight-line-sequence-and-branching-2-2048.jpg)

![Addressing Modes • Implied – AC is implied in “ADD M[AR]” in “One-Address” instr. – TOS is implied in “ADD” in “Zero-Address” instr. • Immediate – The use of a constant in “MOV R1, 5”, i.e. R1 ← 5 • Register – Indicate which register holds the operand Opcode Mode ...](https://image.slidesharecdn.com/programexecutionstraightlinesequenceandbranching-210316075934/75/Program-execution-straight-line-sequence-and-branching-10-2048.jpg)

![Addressing Modes • The different ways in which the location of an operand is specified in an instruction are referred to as addressing modes. Name Assembler syntax Addressingfunction Immediate #Value Operand = Value Register Ri EA = Ri Absolute(Direct) LOC EA = LOC Indirect (Ri ) EA = [Ri ] (LOC) EA = [LOC] Index X(Ri) EA = [Ri ] + X Basewith index (Ri ,Rj ) EA = [Ri ] + [Rj ] Basewith index X(Ri,Rj ) EA = [Ri ] + [Rj ] + X and offset Relative X(PC) EA = [PC] + X Autoincrement (Ri )+ EA = [Ri ] ; Increment Ri Autodecrement (Ri ) Decrement Ri ; EA = [Ri] −](https://image.slidesharecdn.com/programexecutionstraightlinesequenceandbranching-210316075934/75/Program-execution-straight-line-sequence-and-branching-16-2048.jpg)

![Indexing and Arrays • Index mode – the effective address of the operand is generated by adding a constant value to the contents of a register. • Index register • X(Ri): EA = X + [Ri] • The constant X may be given either as an explicit number or as a symbolic name representing a numerical value. • If X is shorter than a word, sign-extension is needed.](https://image.slidesharecdn.com/programexecutionstraightlinesequenceandbranching-210316075934/75/Program-execution-straight-line-sequence-and-branching-17-2048.jpg)

![Indexing and Arrays • In general, the Index mode facilitates access to an operand whose location is defined relative to a reference point within the data structure in which the operand appears. • Several variations: (Ri, Rj): EA = [Ri] + [Rj] X(Ri, Rj): EA = X + [Ri] + [Rj]](https://image.slidesharecdn.com/programexecutionstraightlinesequenceandbranching-210316075934/75/Program-execution-straight-line-sequence-and-branching-18-2048.jpg)