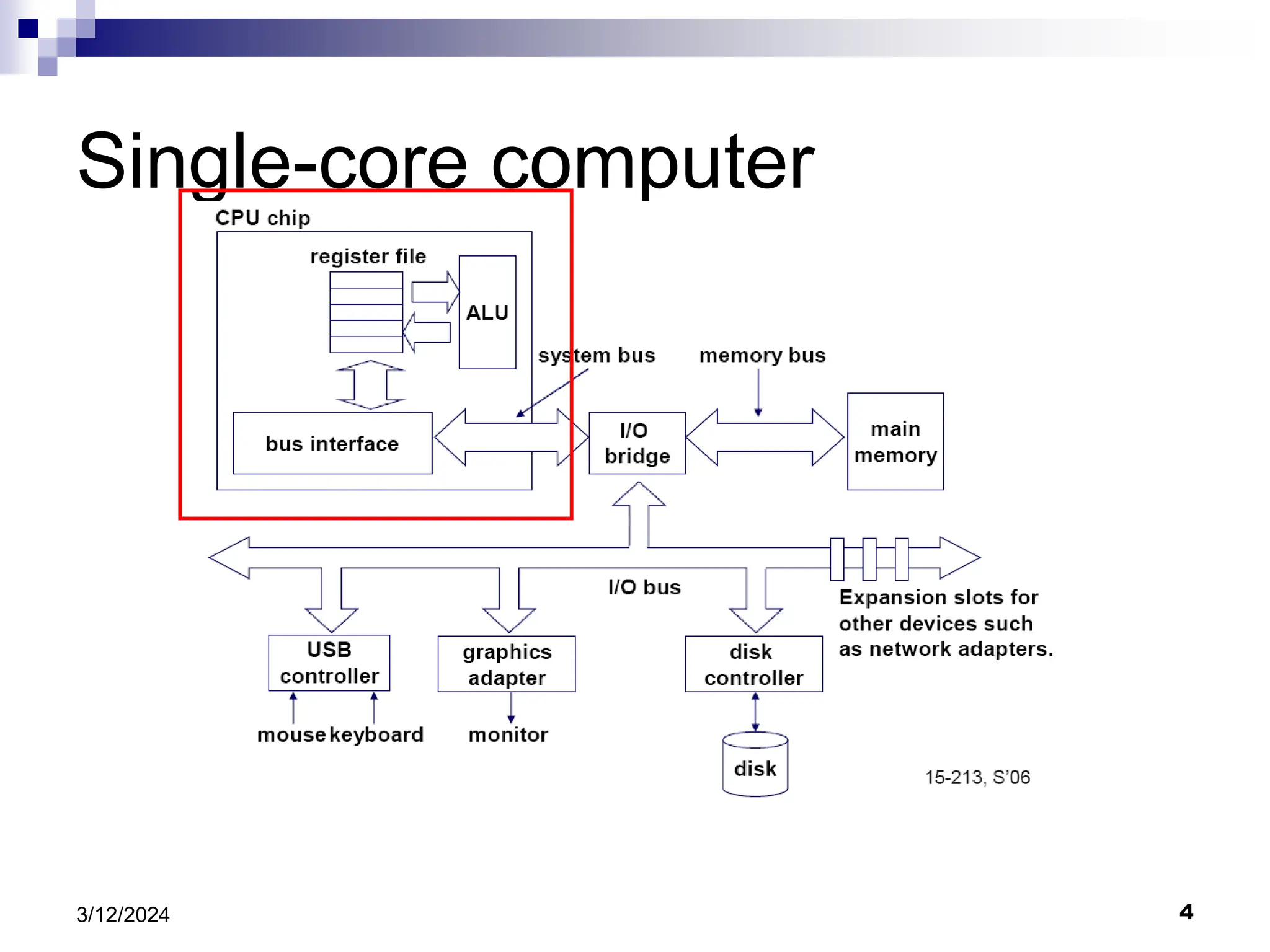

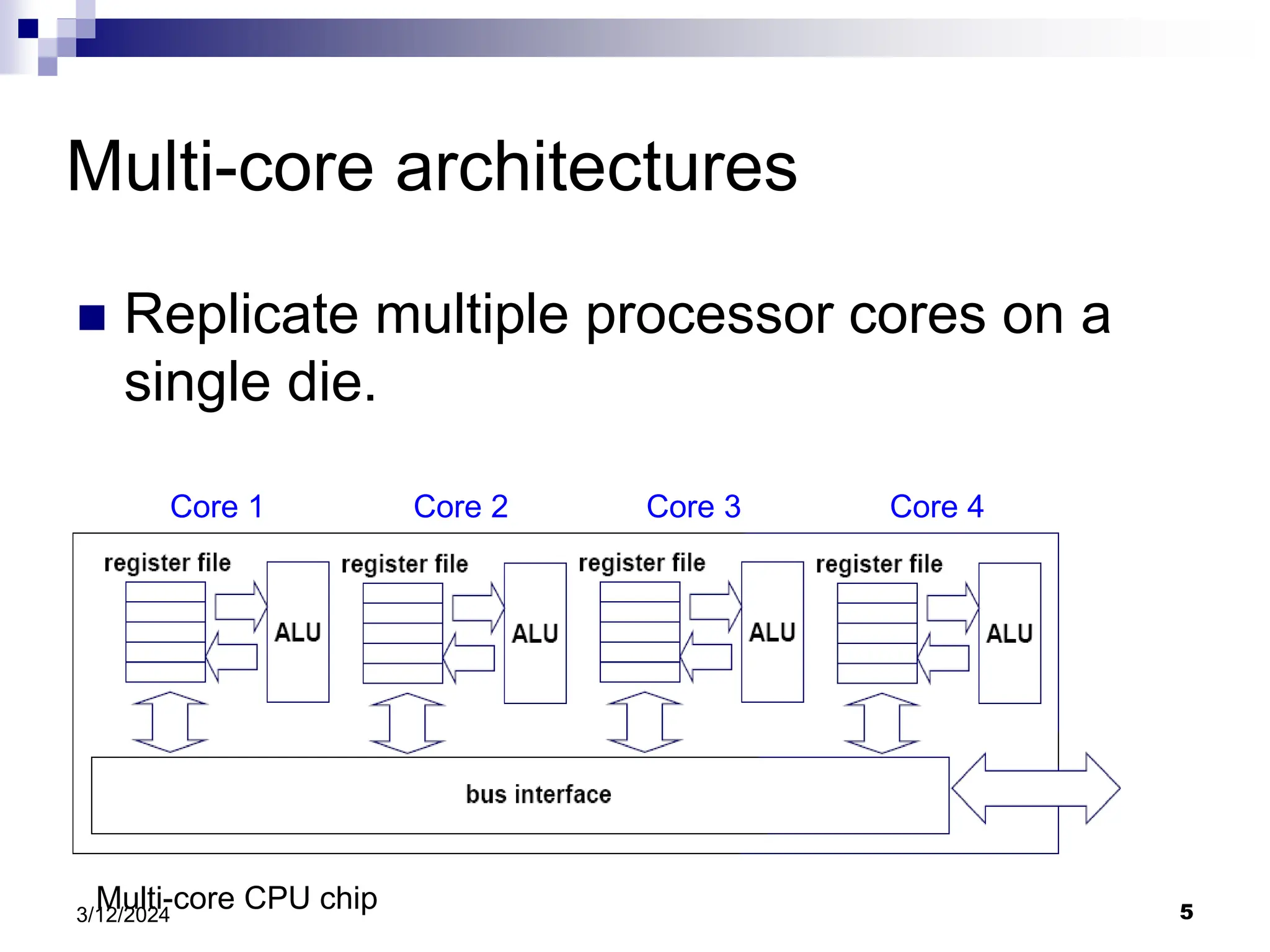

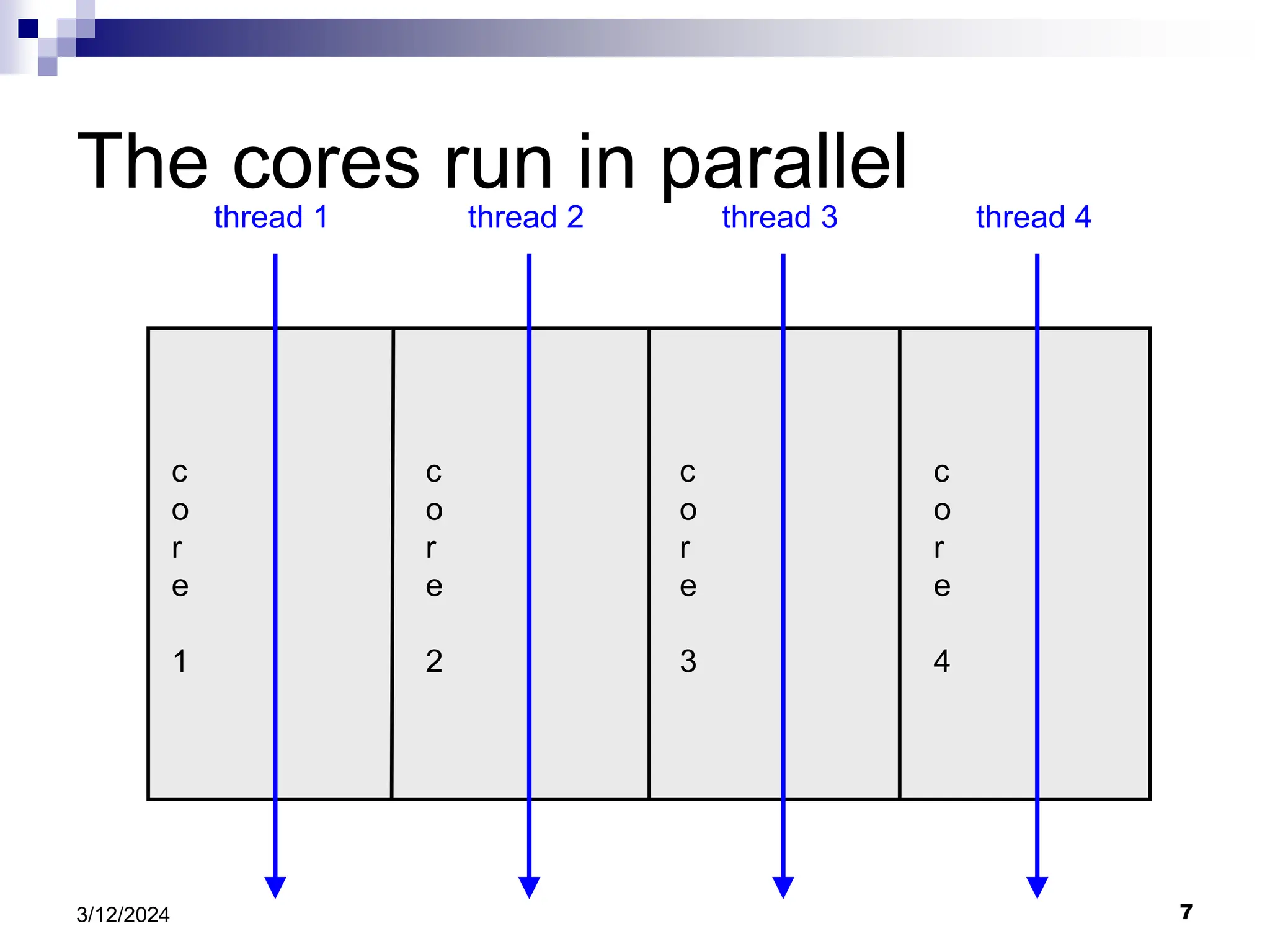

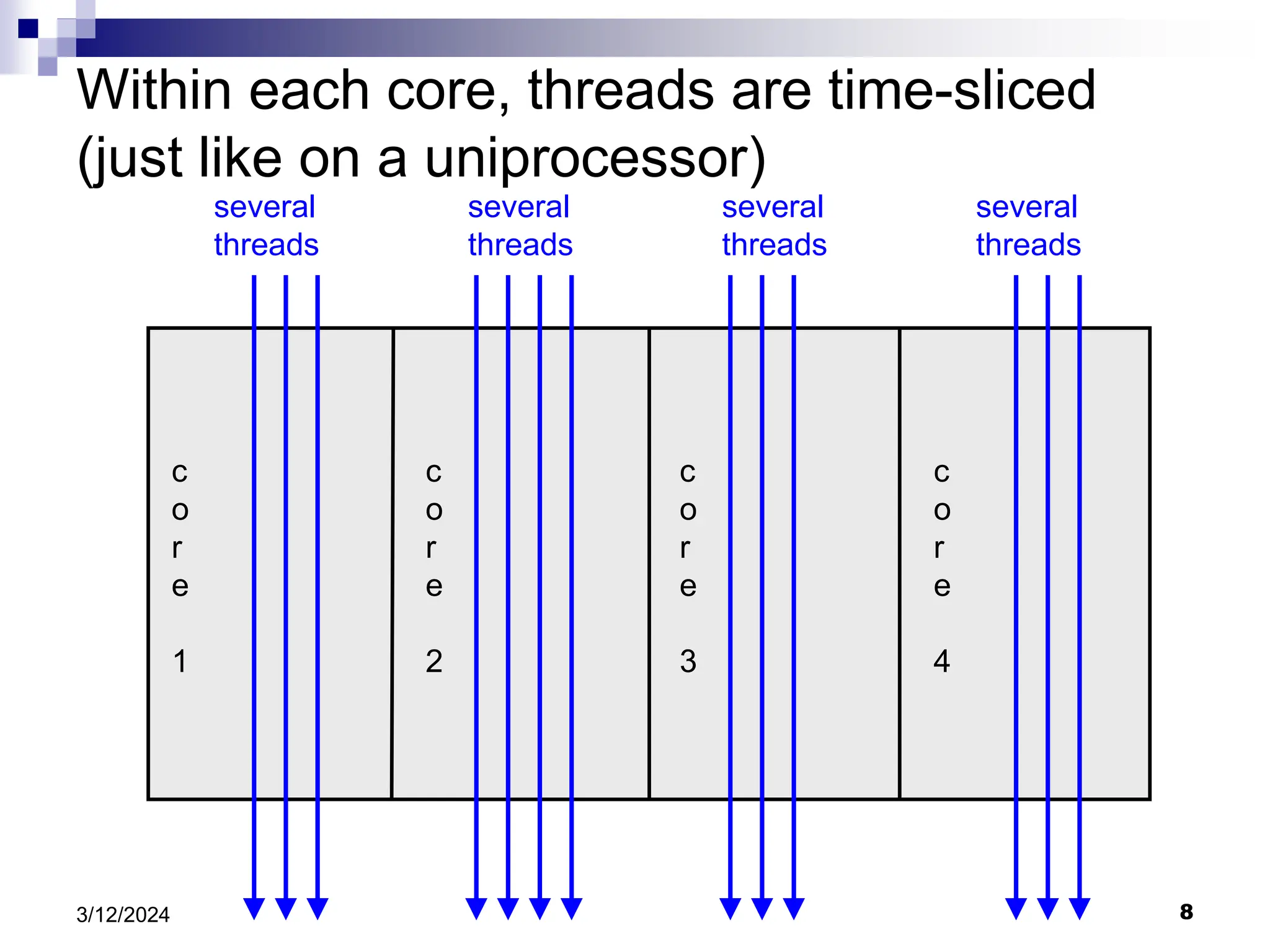

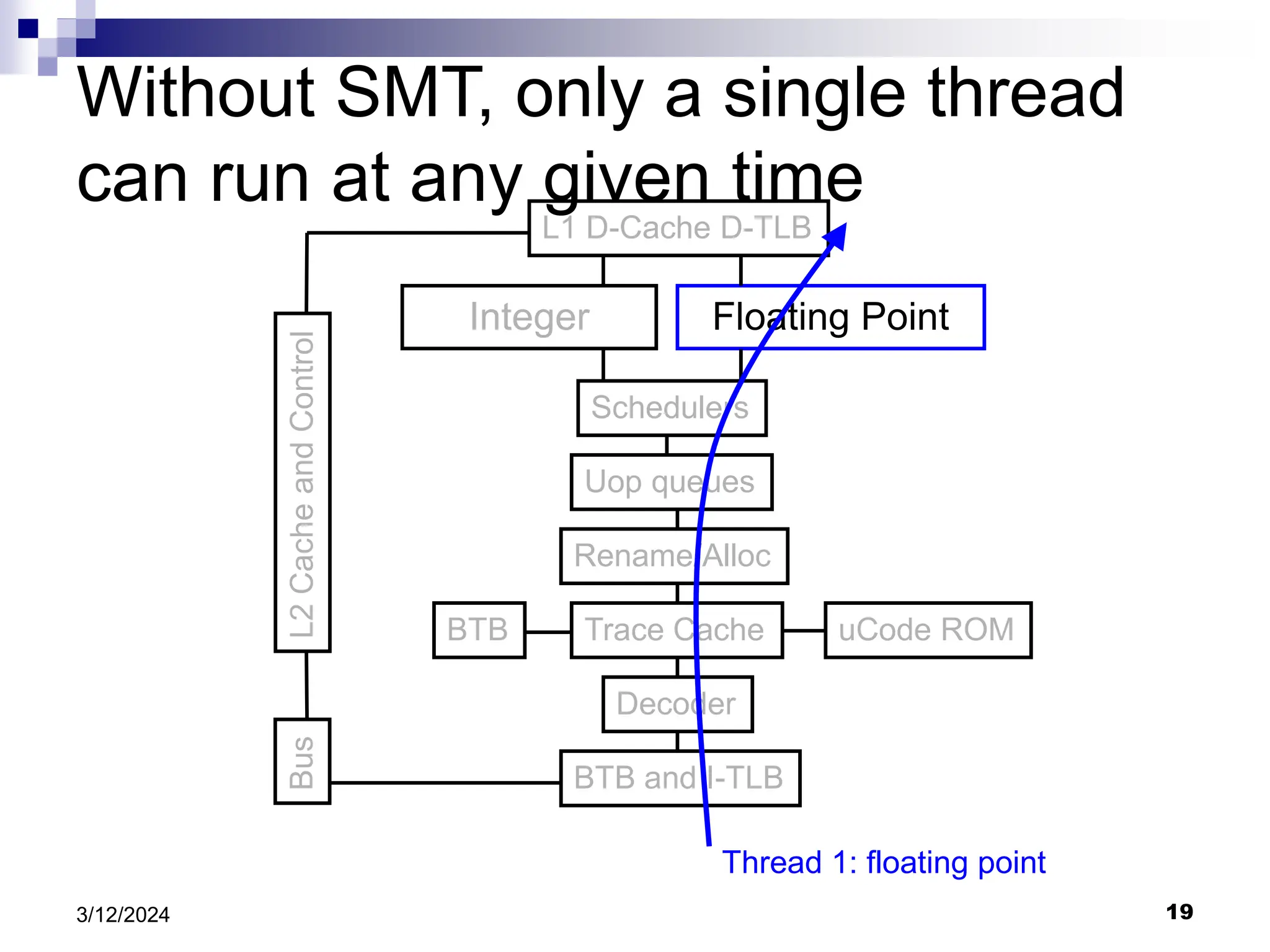

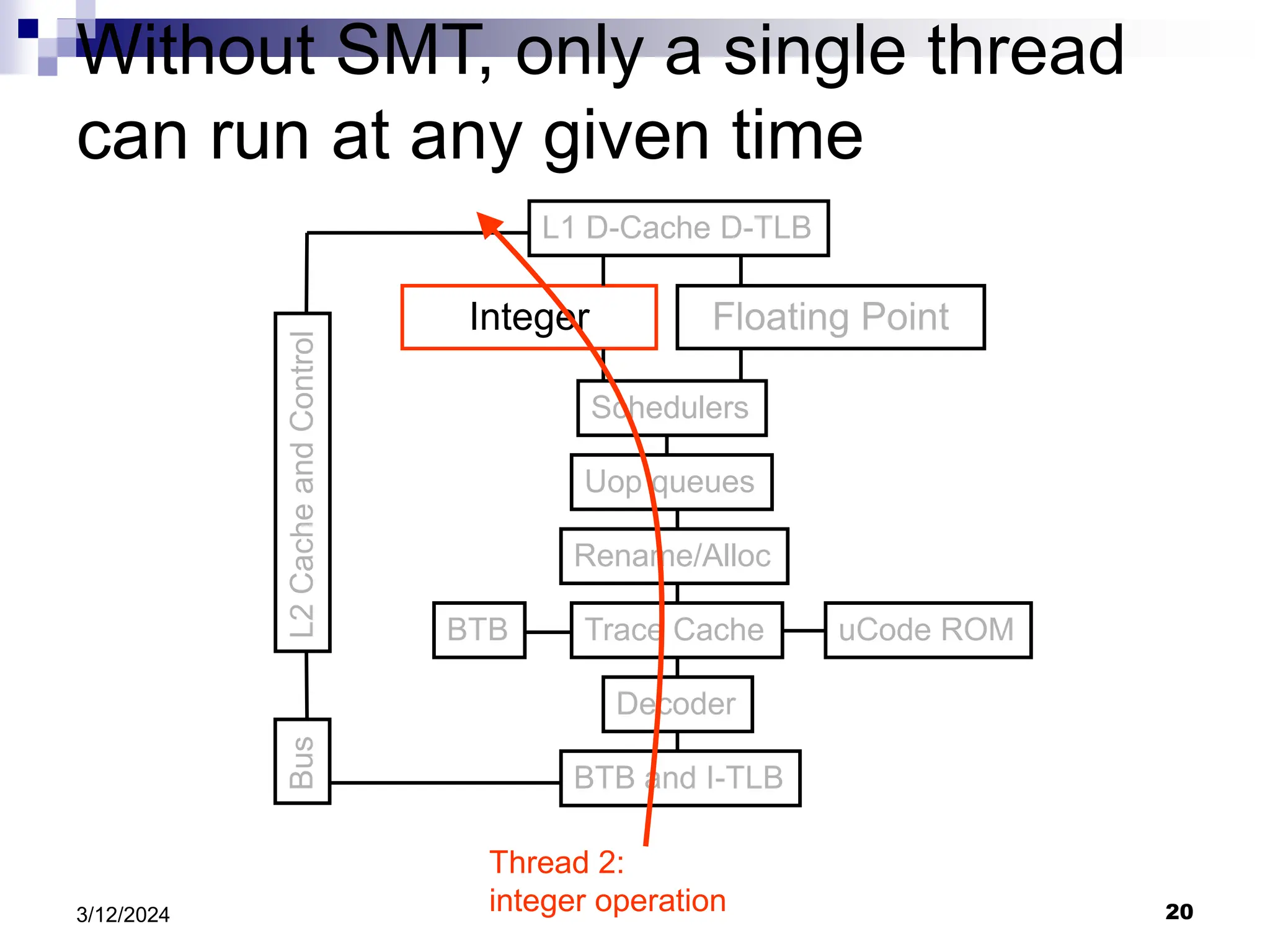

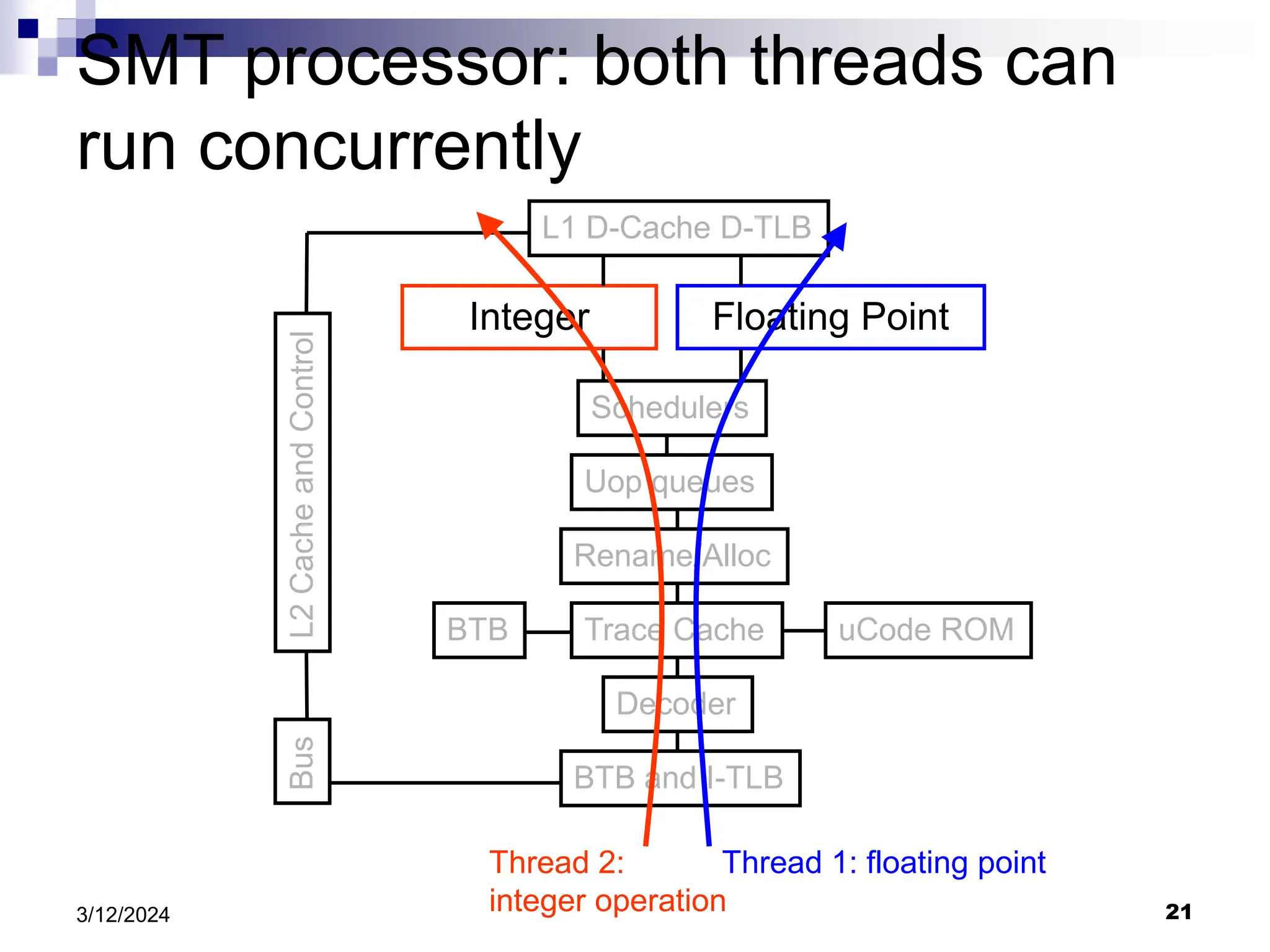

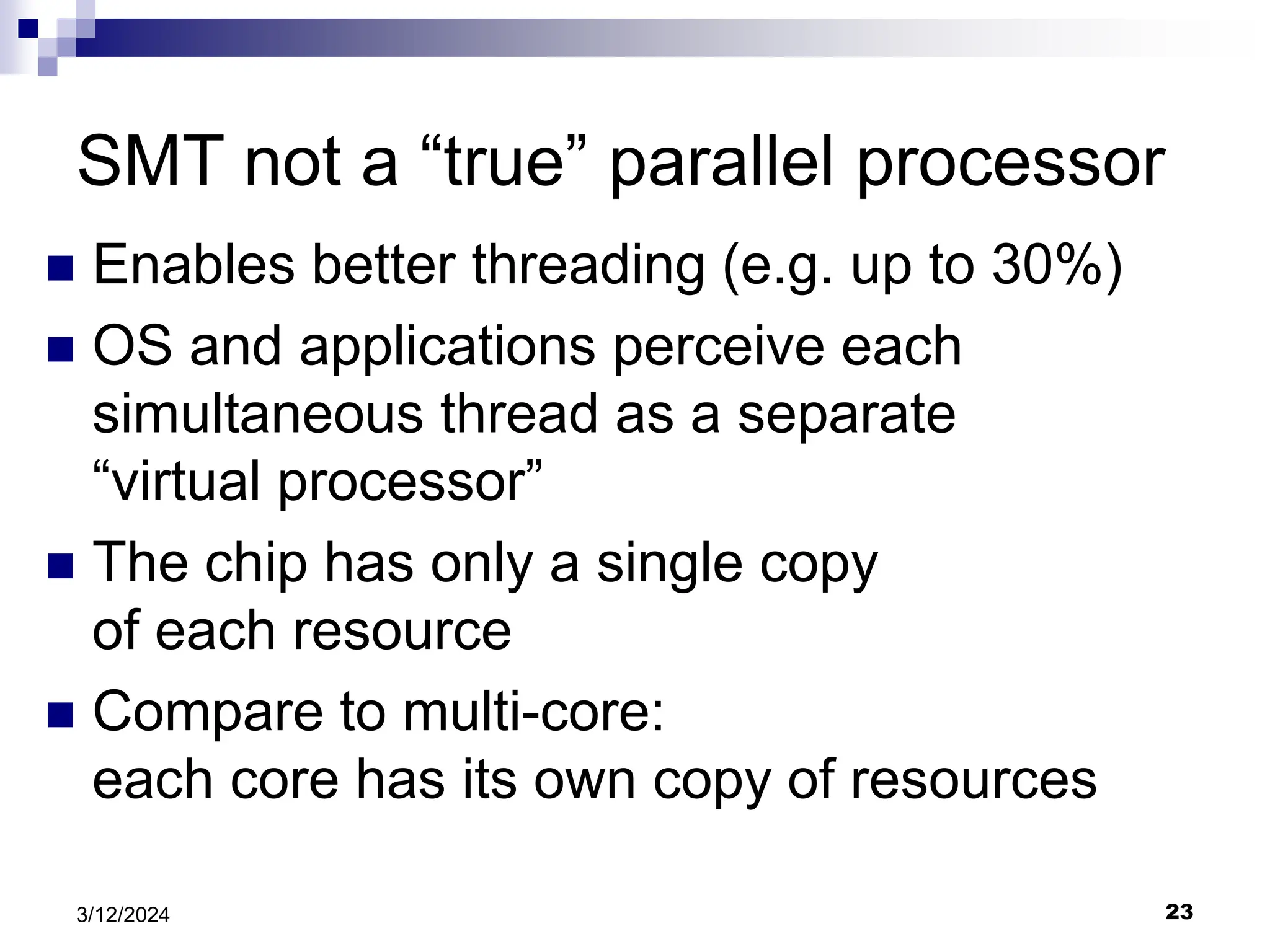

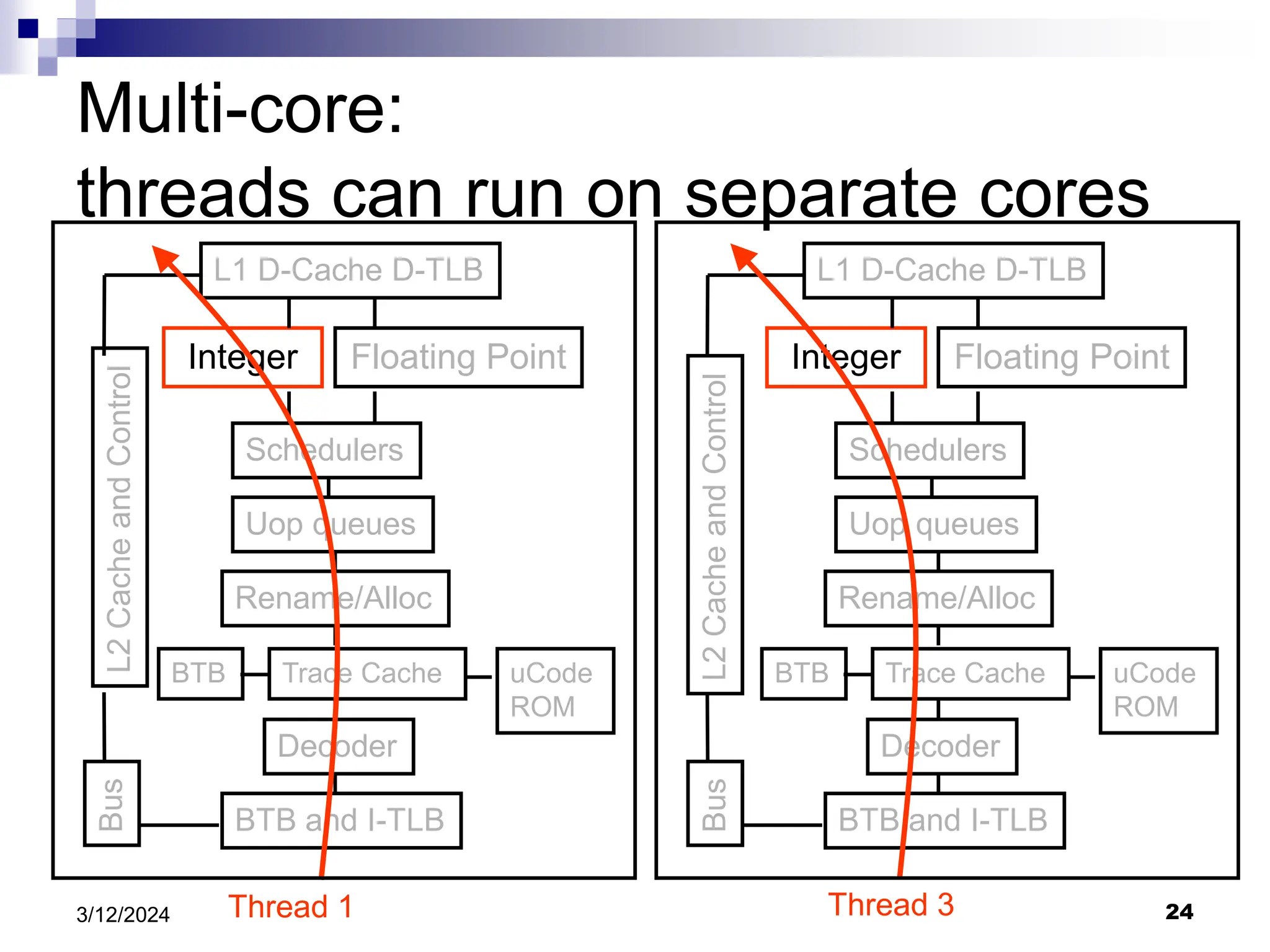

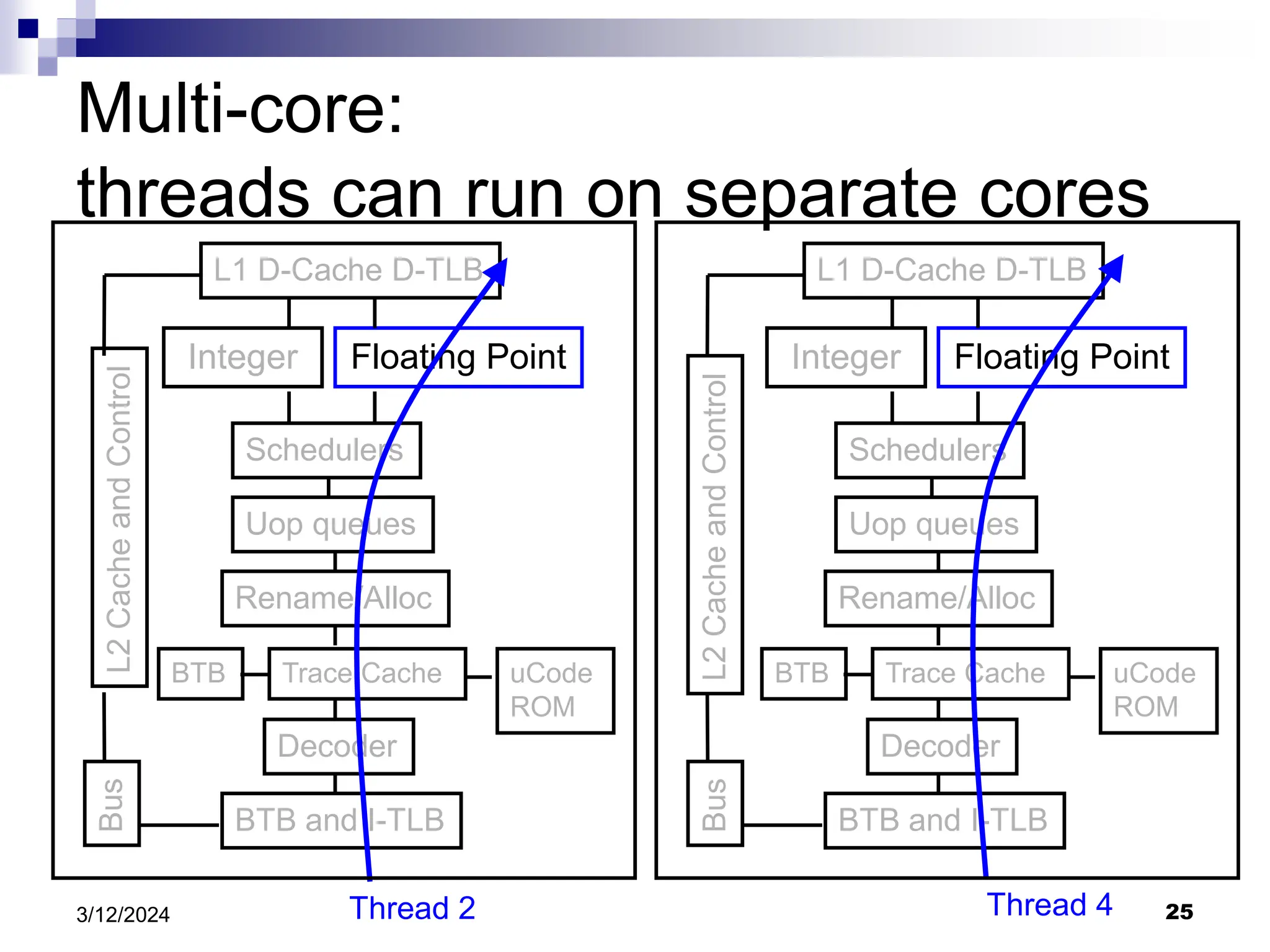

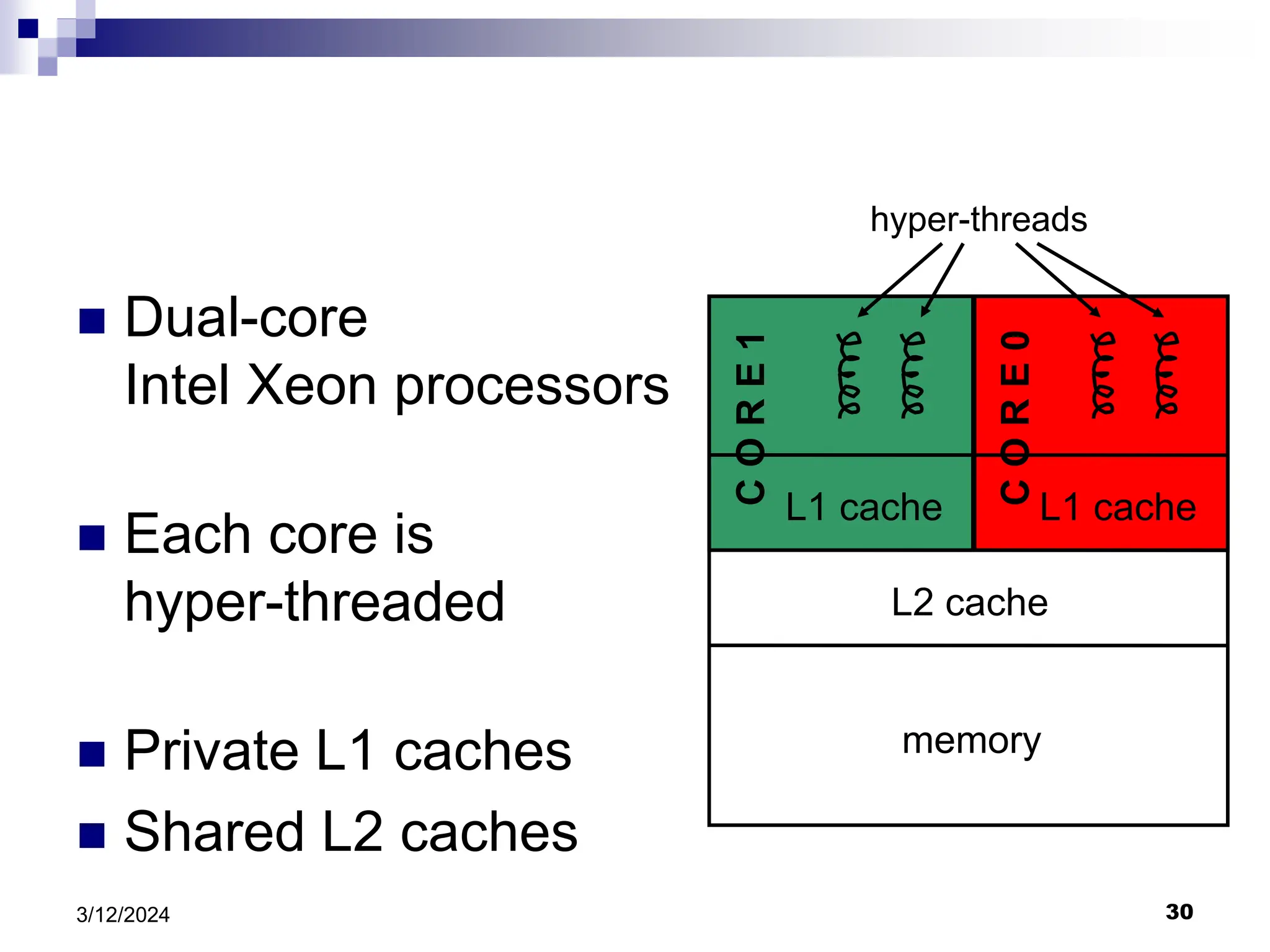

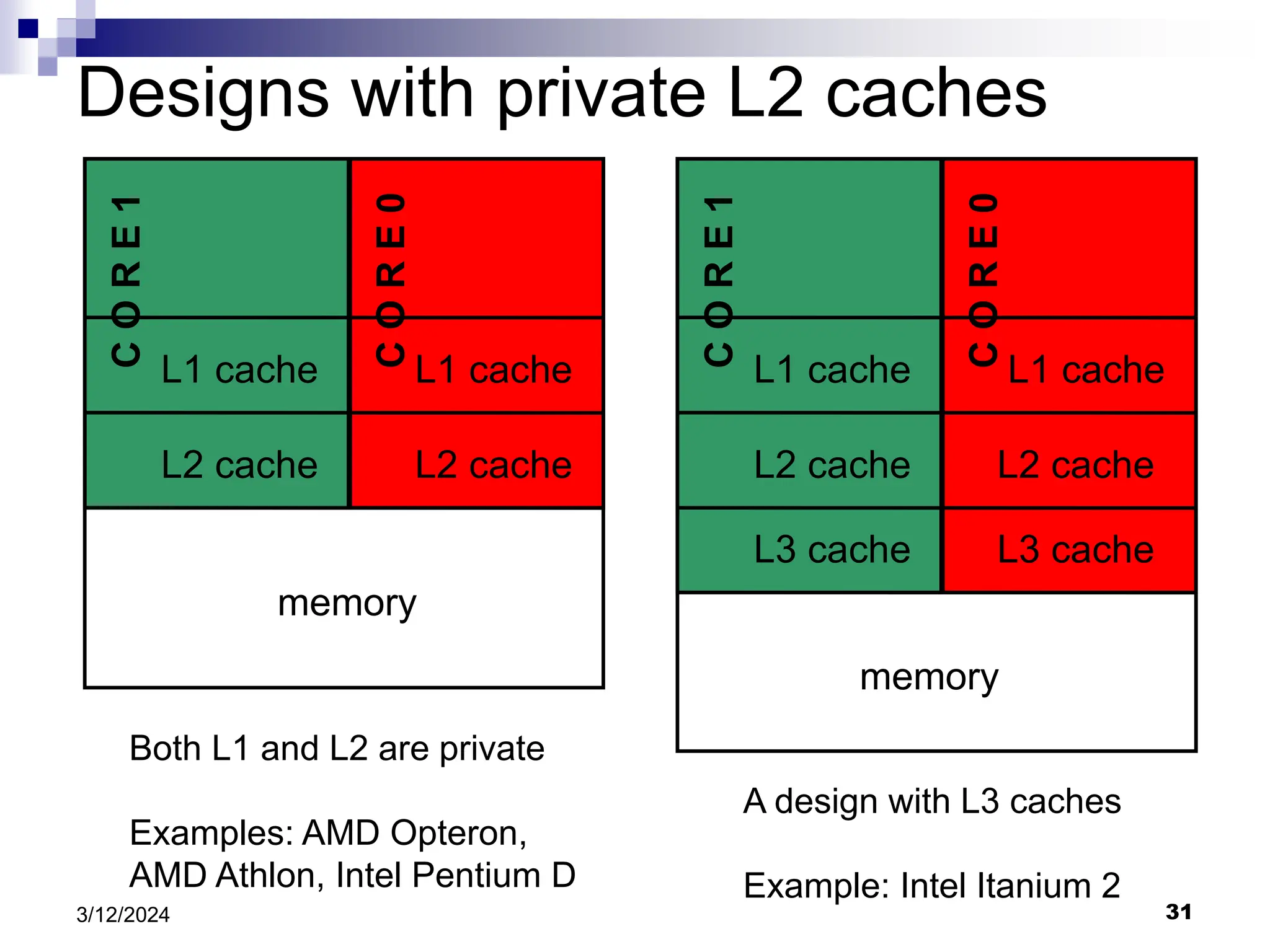

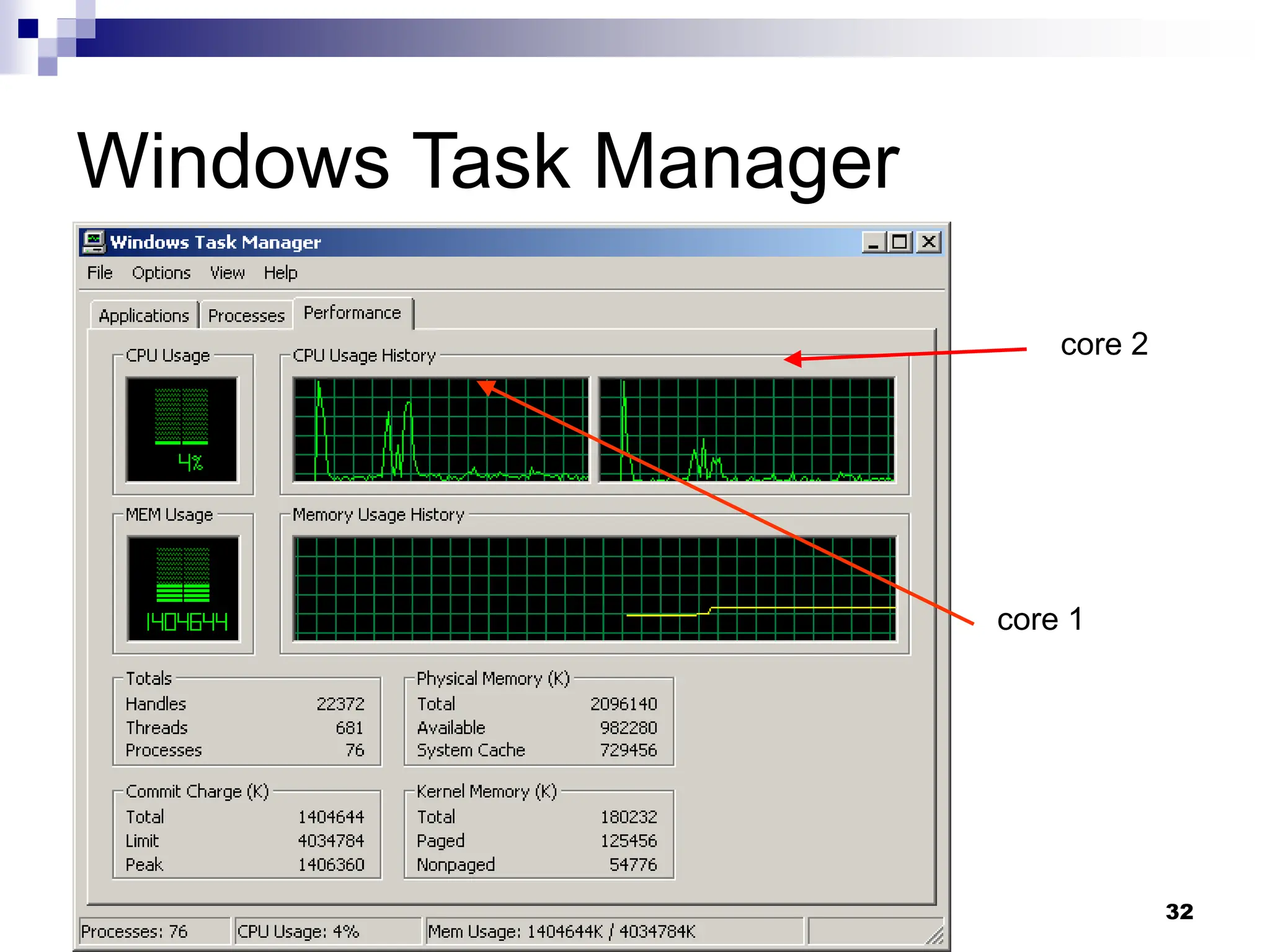

Multi-core computing involves microprocessors with two or more independent processors in a single package, allowing for thread-level parallelism. Major technology providers differ in their definitions of multi-core versus multiple processors, impacting how they design their architectures. Benefits of multi-core include improved performance for multithreaded applications and efficient resource usage, but the effectiveness is contingent on applications being designed to take advantage of multiple threads.