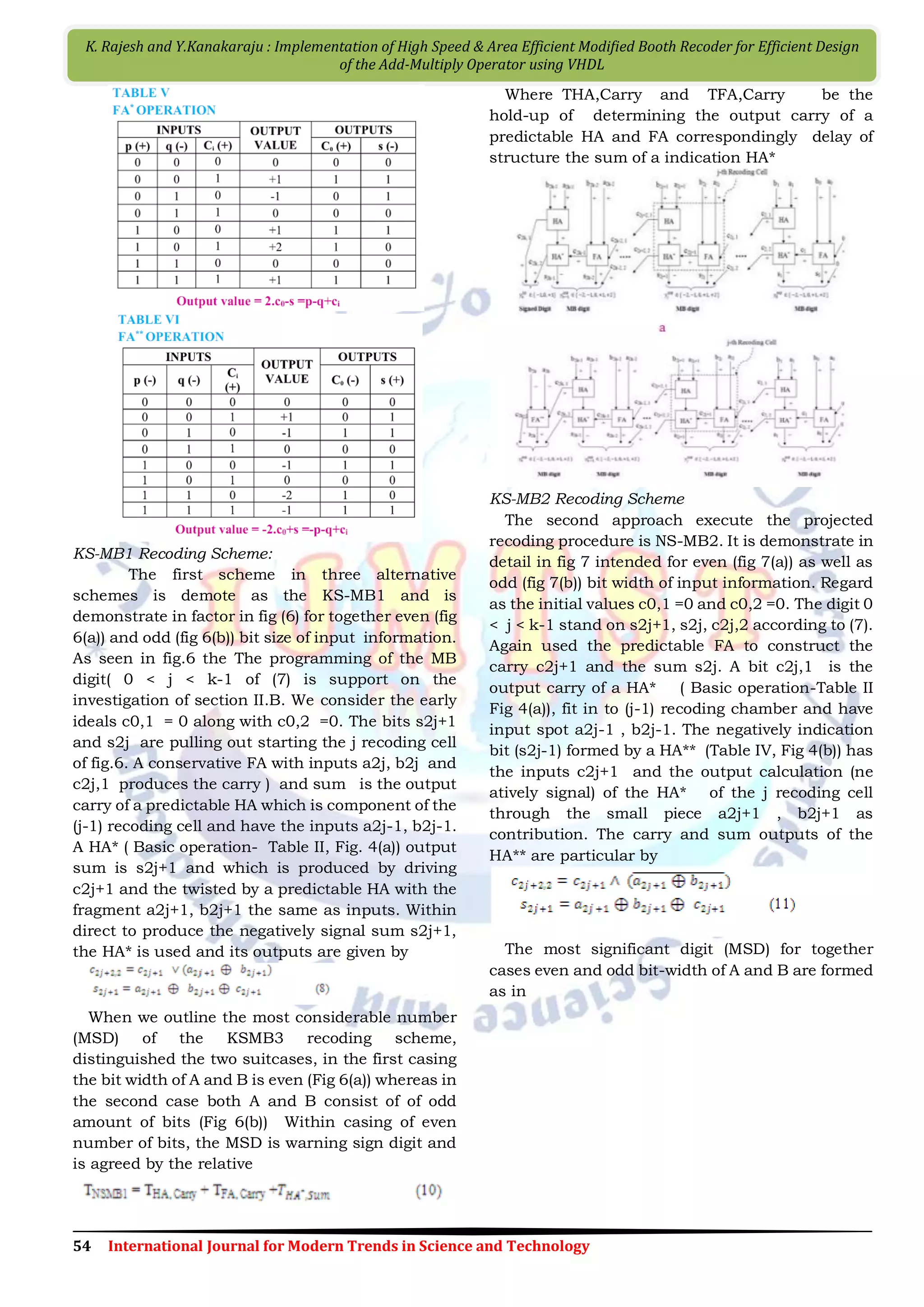

This document discusses the implementation of a high-speed and area-efficient modified Booth recoder for optimizing the add-multiply operator using VHDL, with a focus on reducing power consumption and critical delay in digital signal processing applications. The paper introduces a new recoding technique that allows the direct recoding of sums into modified Booth format, improving performance compared to conventional methods. It presents structural designs and improvements in area utilization and power efficiency through the use of three alternative schemes analyzed with respect to various input sizes.

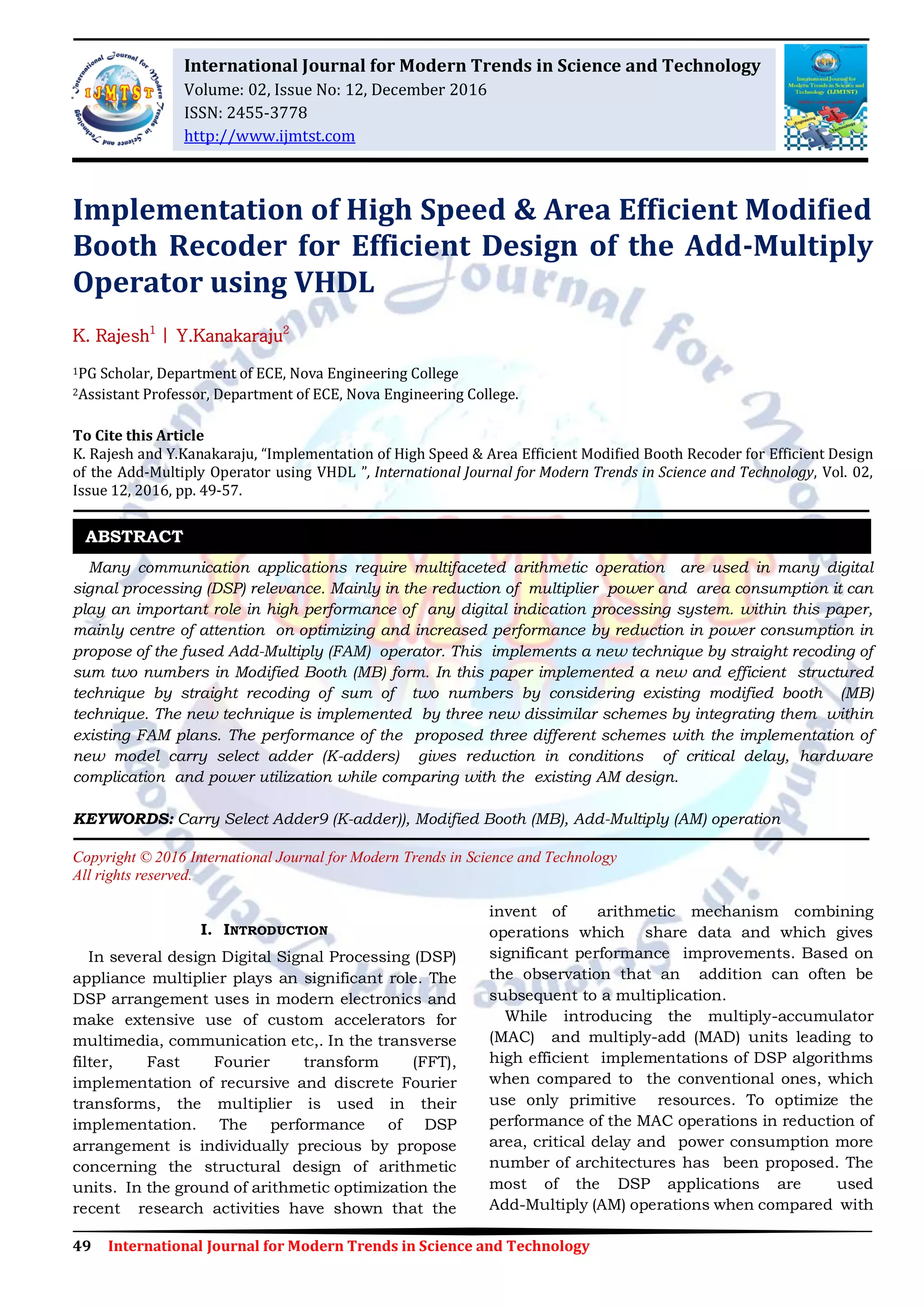

![52 International Journal for Modern Trends in Science and Technology K. Rajesh and Y.Kanakaraju : Implementation of High Speed & Area Efficient Modified Booth Recoder for Efficient Design of the Add-Multiply Operator using VHDL Fig 2(a) shows the Boolean equations on which the implementation of the MB encoding signals is based ( Digits communicate to the three successive bits with one bit extend beyond and allowing for to table I shows how the MB digits are formed by summarizing the MB encoding technique. Each figure is symbolize by three bits given name s, one and two. The sign spot (s) represents the number sign either negative (s=1) or optimistic (s=0). Signal one representing the complete value of a numeral is equal to 1 (one=1) or not (one=0). sign two representing the complete value of a number is equal to 2 (two=1) or not (two=0). By means of these three signals (s, one, two) the MB digit formed and it’s represented by following equation Fig 2(a) shows the Boolean equations on which the implementation of the MB encoding signals is based ( Fig 2(b)). 1. FAM Implementation: The proposed FAM design represented in fig 1 (b) The multiplier is a parallel one based on the MB algorithm. Let us consider X,Y, the term Y= { yn-1 yn-2............y1y0}2’s is prearranged stand on the MB algorithm and multiply with X= { xn-1 xn-2.......x1x0}2’s. Mutually X and Y consists of n=2k bits and in 2’s complement form. Equation (4) explains the production of the k partial commodities.The partial product is generated and is stand on the subsequently logical appearance while fig (3) demonstrate its execution at gate intensity 2. SCG Unit of the BEC-Based CSLA (K-ADER) As shown in Fig. 2, the RCA calculates n-bit sum s01 and c0 out corresponding to cin = 0. The BEC unit receives s01 and c0 out from the RCA and generates (n + 1)-bit excess-1 code. The most significant bit (MSB) of BEC represents c1 out, in which n least significant bits (LSBs) represent s11 . The logic expressions We consider x-1 =0 and xn = xn-1 for the working out of the slightest and most considerable bits of partial product respectively. The quantity of ensuing prejudiced products are [n/2] +1=k+1 in case of n=2k+1. Based on sign conservatory of the preliminary 2’s complement digit the most significant MB digit is formed. After generation of partial products they are further properly weighted throughout a carry select adder (CSL) and which is prearranged by following equation The output of the carry select adder (CSL) gives the result Z=X.Y as shown in fig 1(b). III. NEW SUM TO MODIFIED BOOTH RECODING TECHNIQUES (KS-MB) Defining signed bit full adders and half adders for structured signed Arithmetic The recoding in this New sum to modified booth Recoder is recorded by considering the two consecutive bits of the input A (a2j , a2j+1) with two consecutive bits of the input B (b2j, b2j+1) into one MB digit. As from eq.(2) , the MB digit is formed by including the three bits. The most considerable of them is negatively slanted whereas two least considerable of them have positive weight. Use signed spot calculation in order to make over the two aforementioned couple of bits in MB appearance. In this paper presented a set of bit stage half adders (HA) and Full adders (FA) considering their](https://image.slidesharecdn.com/228ijmtst021242-170109034217/75/Implementation-of-High-Speed-Area-Efficient-Modified-Booth-Recoder-for-Efficient-Design-of-the-Add-Multiply-Operator-using-VHDL-4-2048.jpg)

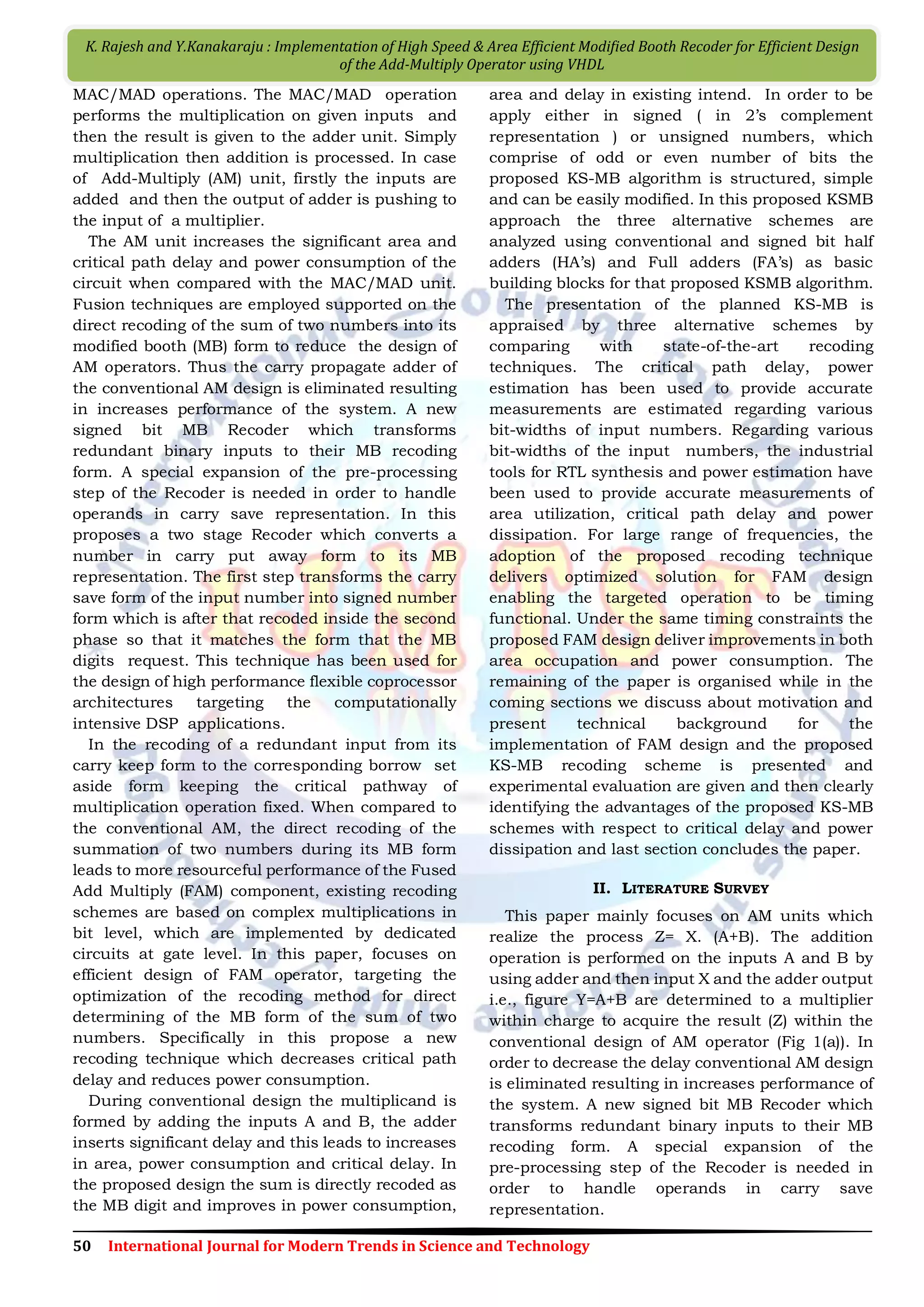

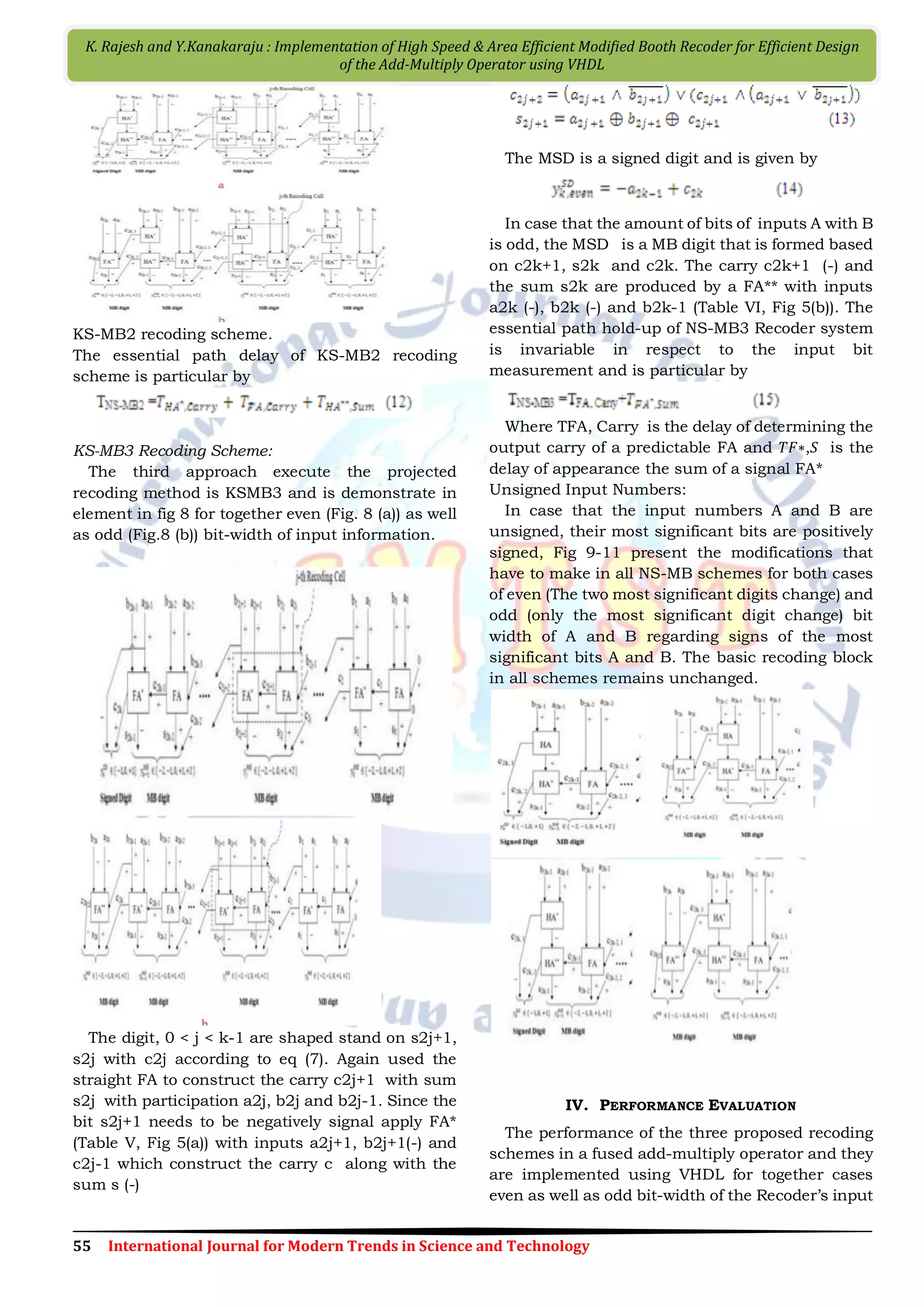

![56 International Journal for Modern Trends in Science and Technology K. Rajesh and Y.Kanakaraju : Implementation of High Speed & Area Efficient Modified Booth Recoder for Efficient Design of the Add-Multiply Operator using VHDL information. To evaluate the presentation of the projected KS-MB schemes by evaluate with the active method in terms of critical delay, power consumption is show in table- VII for Even bit width of the inputs. The inputs with odd bit width and their comparison is shown in table-VIII The comparison of power consumption with different techniques is shown in fig. 12 for even bit width as well as for odd bit size is show in fig.13 Fig:4 Simulation result of Even Bit Width Fig 5: Simulation result of odd Bit Width Comparison of delay, power consumption ( Fig 6: Graphical comparision V. CONCLUSION The design of the fused add-multiply is used to execute the straight recoding of the addition of two information in its modified booth (MB) form. This work focuses on optimizing the invent of the Fused add-multiply (FAM) machinist. In this work explored three new alternative designs of the proposed New sum to modifies booth recoding technique (KS-MB) and compared them with the existing method. The proposed recoding schemes incorporated in FAM designs and they give the performance improvements in conditions of critical delay, power expenditure comparing by way of existing method. REFERENCES [1] Kostas Tsoumanis, Sotiris Xydis and Kaima Pekmestzi “An Optimized Modified Booth Recoder for Efficient Design of the Add-Multiply Operator”, IEEE Trans, Vol. 61, No. 4, April 2014. [2] A. Amaricai, M. Vladutiu, and O. Boncalo, “Design issues and imple-mentations for floating-point divide-add fused,” IEEE Trans. Circuits Syst. II–Exp. Briefs, vol. 57, no. 4, pp. 295–299, Apr. 2010. [3] E. E. Swartzlander and H. H. M. Saleh, “FFT implementation with fused ßoating-point operations,” IEEE Trans. Comput., vol. 61, no. 2, pp. 284–288, Feb. 2012. [4] J. J. F. Cavanagh,DigitalComputer Arithmetic. NewYork: McGraw-Hill, 1984. [5] S. Nikolaidis, E. Karaolis, and E. D. Kyriakis-Bitzaros, “Estimation of signal transition activity inFIR Þlters implemented by a MAC archi-tecture,” IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst., vol. 19, no. 1, pp. 164–169, Jan. 2000. [6] O. Kwon, K. Nowka, and E. E. Swartzlander, “A 16-bit by 16-bit MAC design using fast 5: 3 compressor cells,” J. VLSI Signal Process. Syst., vol. 31, no. 2, pp. 77–89, Jun. 2002. [7] L.-H. Chen, O. T.-C. Chen, T.-Y. Wang, and Y.-C. Ma, “A multiplica-tion-accumulation computation unit with optimized compressors and minimized switching activities,” in Proc. IEEE Int, Symp. Circuits and Syst., Kobe, Japan, 2005, vol. 6, pp. 6118–6121. [8] Y.-H. Seo and D.-W. Kim, “A new VLSI architecture of parallel multiplier–accumulator based on Radix-2 modiÞed Booth algorithm,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 18, no. 2, pp. 201–208, Feb. 2010. [9] A. Peymandoust and G. de Micheli, “Using symbolic algebra in algo-rithmic level DSP synthesis,” in Proc. Design Automation Conf., Las Vegas, NV, 2001, pp. 277–282. [10]W.-C. Yeh and C.-W. Jen, “High-speed and low-power split-radix FFT,” IEEE Trans. Signal Process., vol. 51, no. 3, pp. 864–874, Mar. 2003.](https://image.slidesharecdn.com/228ijmtst021242-170109034217/75/Implementation-of-High-Speed-Area-Efficient-Modified-Booth-Recoder-for-Efficient-Design-of-the-Add-Multiply-Operator-using-VHDL-8-2048.jpg)

![57 International Journal for Modern Trends in Science and Technology K. Rajesh and Y.Kanakaraju : Implementation of High Speed & Area Efficient Modified Booth Recoder for Efficient Design of the Add-Multiply Operator using VHDL [11]C. N. Lyu and D. W. Matula, “Redundant binary Booth recoding,” in Proc. 12th Symp. Comput. Arithmetic, 1995, pp. 50–57. [12]J. D. Bruguera and T. Lang, “Implementation of the FFT butterßy with redundant arithmetic,” IEEE Trans. Circuits Syst. Il, Analog Digit. Signal Process., vol. 43, no. 10, pp. 717–723, Oct. 1996. [13]W.-C. Yeh, “Arithmetic Module Design and its Application to FFT,” Ph.D. dissertation, Dept. Electron. Eng., National Chiao-Tung University, , Chiao-Tung, 2001. [14]R. Zimmermann and D. Q. Tran, “Optimized synthesis of sum-of-prod-ucts,” in Proc. Asilomar Conf. Signals, Syst. Comput., PaciÞc Grove, Washington, DC, 2003, pp. 867–872. [15]B. Parhami, Computer Arithmetic: Algorithms and Hardware De-signs. Oxford: Oxford Univ. Press, 2000. [16]O. L. Macsorley, “High-speed arithmetic in binary computers,” Proc. IRE, vol. 49, no. 1, pp. 67–91, Jan. 1961. [17]N. H. E. Weste and D. M. Harris, “Datapath subsystems,” in CMOS VLSI Design: A Circuits and Systems Perspective, 4th ed. Read-ington: Addison-Wesley, 2010, ch. 11. [18]S. Xydis, I. Triantafyllou, G. Economakos, and K. Pekmestzi, “Flex-ible datapath synthesis through arithmetically optimized operation chaining,” in Proc. NASA/ESA Conf. Adaptive Hardware Syst., 2009, 407–414. [19]http://www.synopsys.com/Tools/Implementaton RTLSynthesis/DCUltra/Pages/default.aspx [20]http://www.synopsys.com/Tools/Implementation/ SignOff/PrimeTime/Pages/default.aspx [21]Z. Huang, “High-Level Optimization Techniques for Low-Power Mul-tiplier Design,” Ph.D., University of California, Department of Com-puter Science, Los Angeles, CA, 2003. [22]C. S. Wallace, “A suggestion for a fast multiplier,” IEEE Trans. Elec-tron. Comput., vol. EC-13, no. 1, pp. 14–17, 1964. [23]M. Daumas and D. W. Matula, “A Booth multiplier accepting both a redundant or a non redundant input with no additional delay,” in Proc. IEEE Int. Conf. on Application-SpeciÞc Syst., Architectures, and Pro-cessors, 2000, pp. 205–214. [24]Z. Huang and M. D. Ercegovac, “High-performance low-power left-to-right array multiplier design,” IEEE Trans. Comput., vol. 54, no. 3, pp. 272–283, Mar. 2005.](https://image.slidesharecdn.com/228ijmtst021242-170109034217/75/Implementation-of-High-Speed-Area-Efficient-Modified-Booth-Recoder-for-Efficient-Design-of-the-Add-Multiply-Operator-using-VHDL-9-2048.jpg)