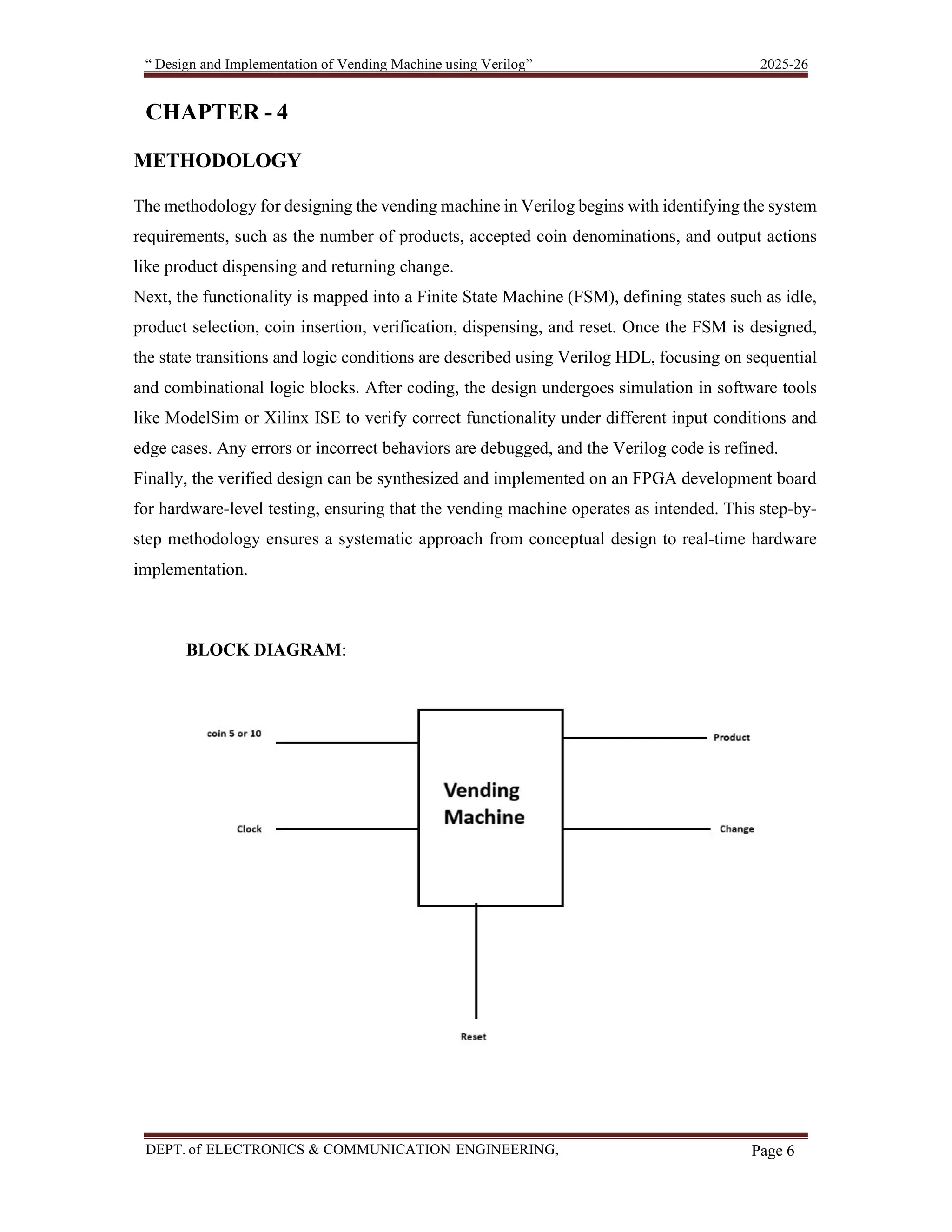

This project focuses on creating a digital vending machine model using Verilog HDL (Hardware Description Language). The vending machine is designed to dispense products (like snacks or drinks) when a customer inserts the correct amount of money and makes a selection. It uses concepts like Finite State Machines (FSM) to handle different states such as waiting for input, checking balance, dispensing product, and returning change. The project shows how digital logic design and Verilog programming can be used to implement a real-world system that is simple, user-friendly, and reliable. It demonstrates your understanding of HDL coding, simulation, hardware design, and problem-solving in electronics.