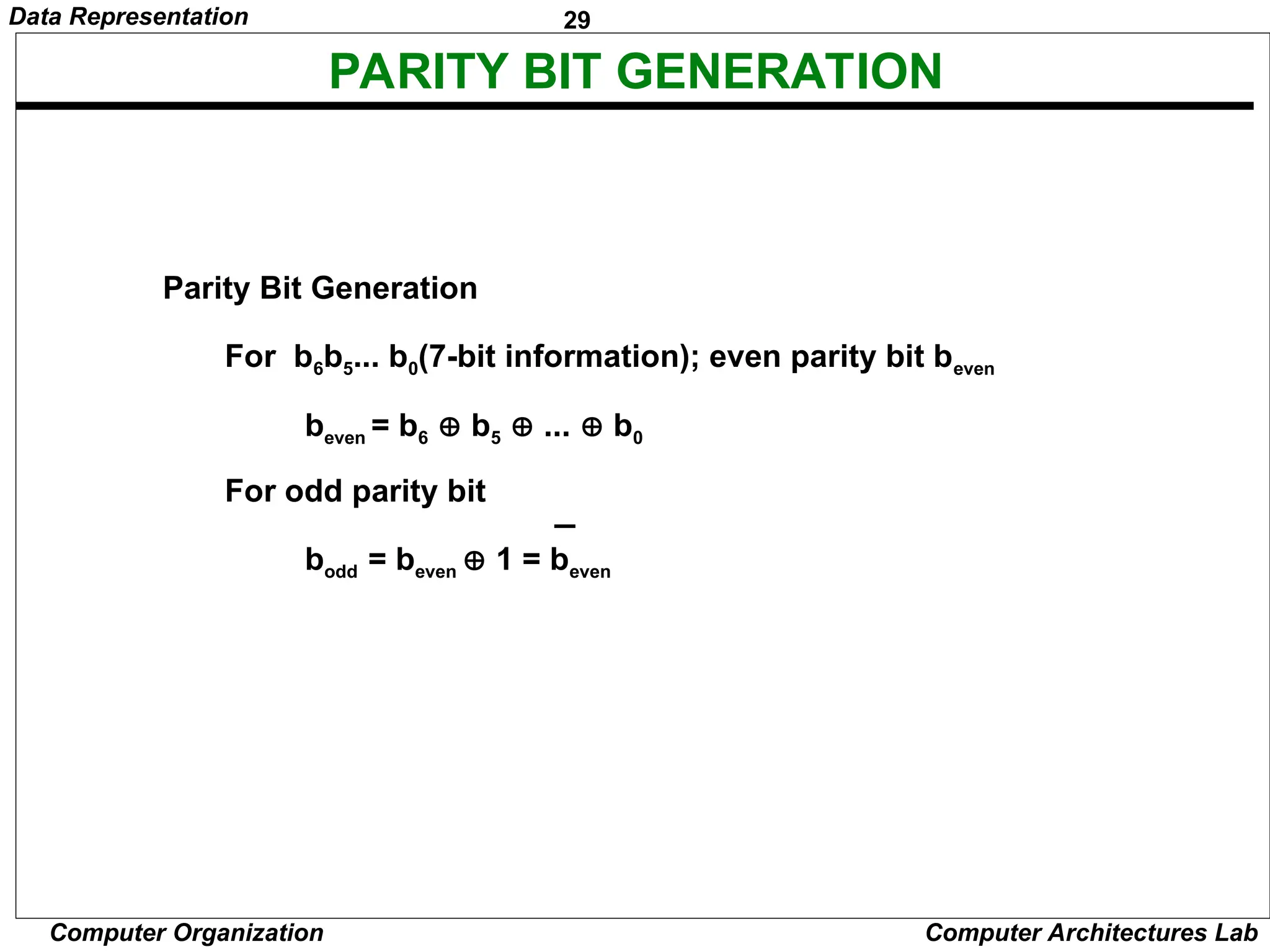

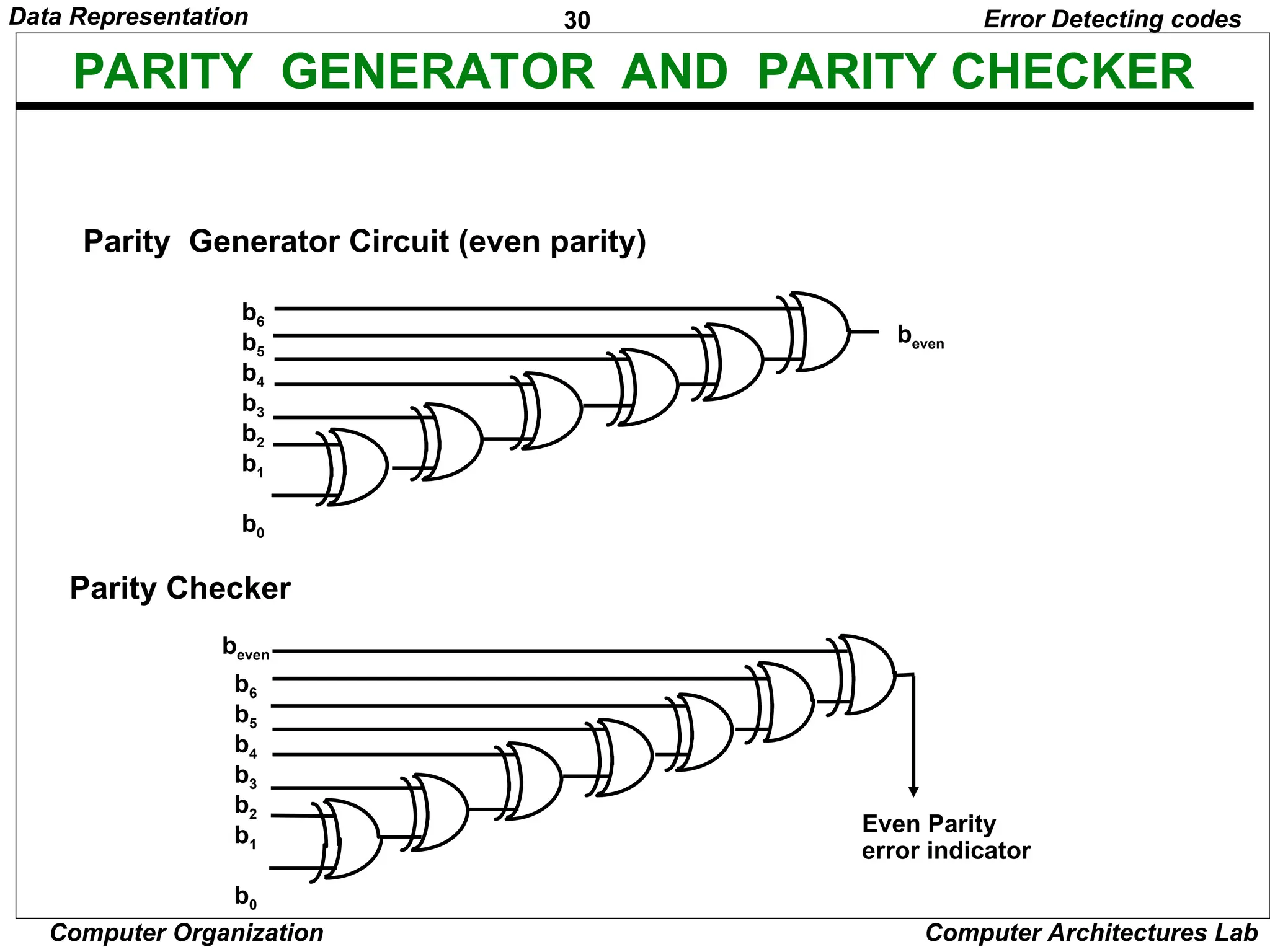

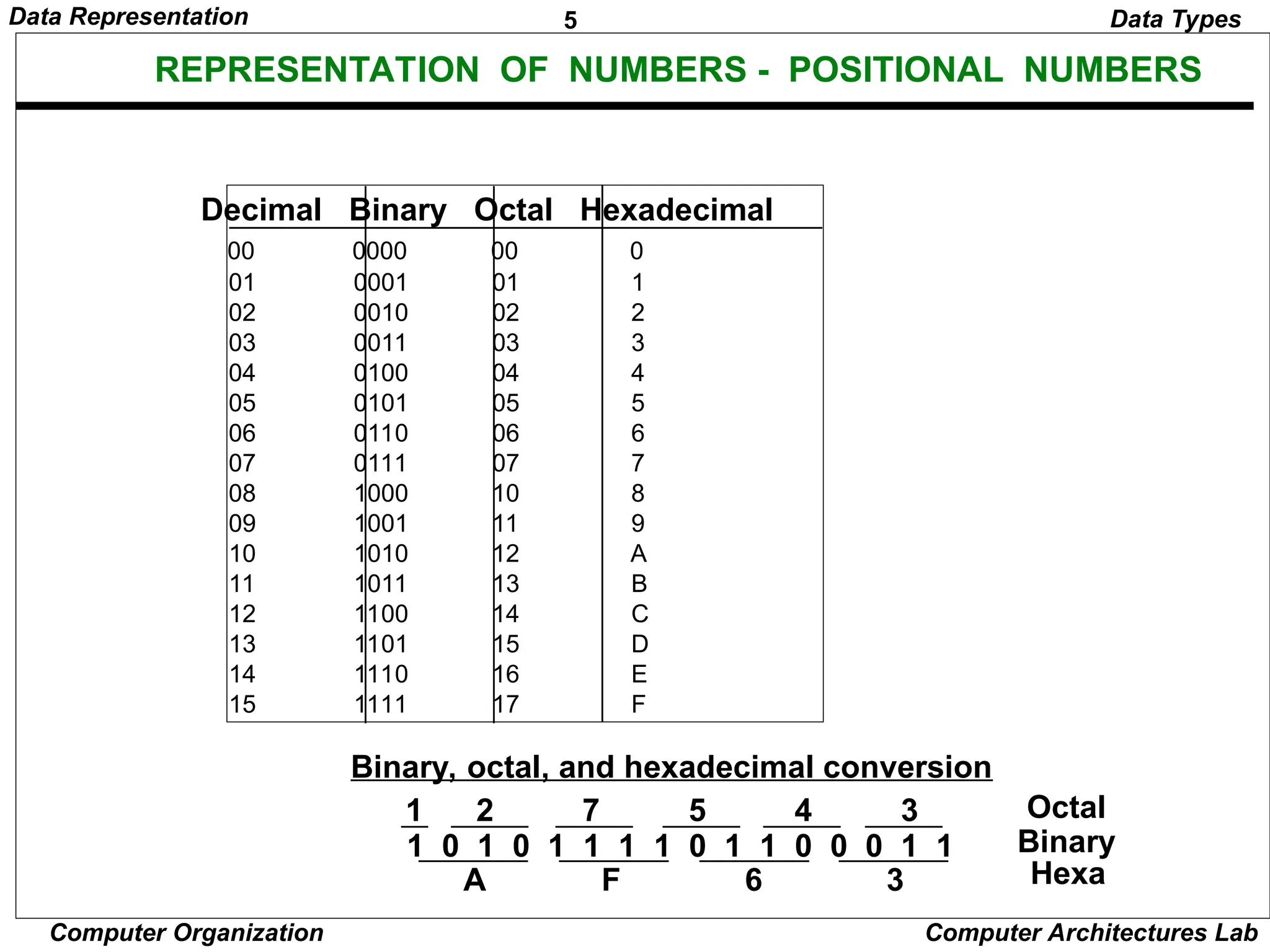

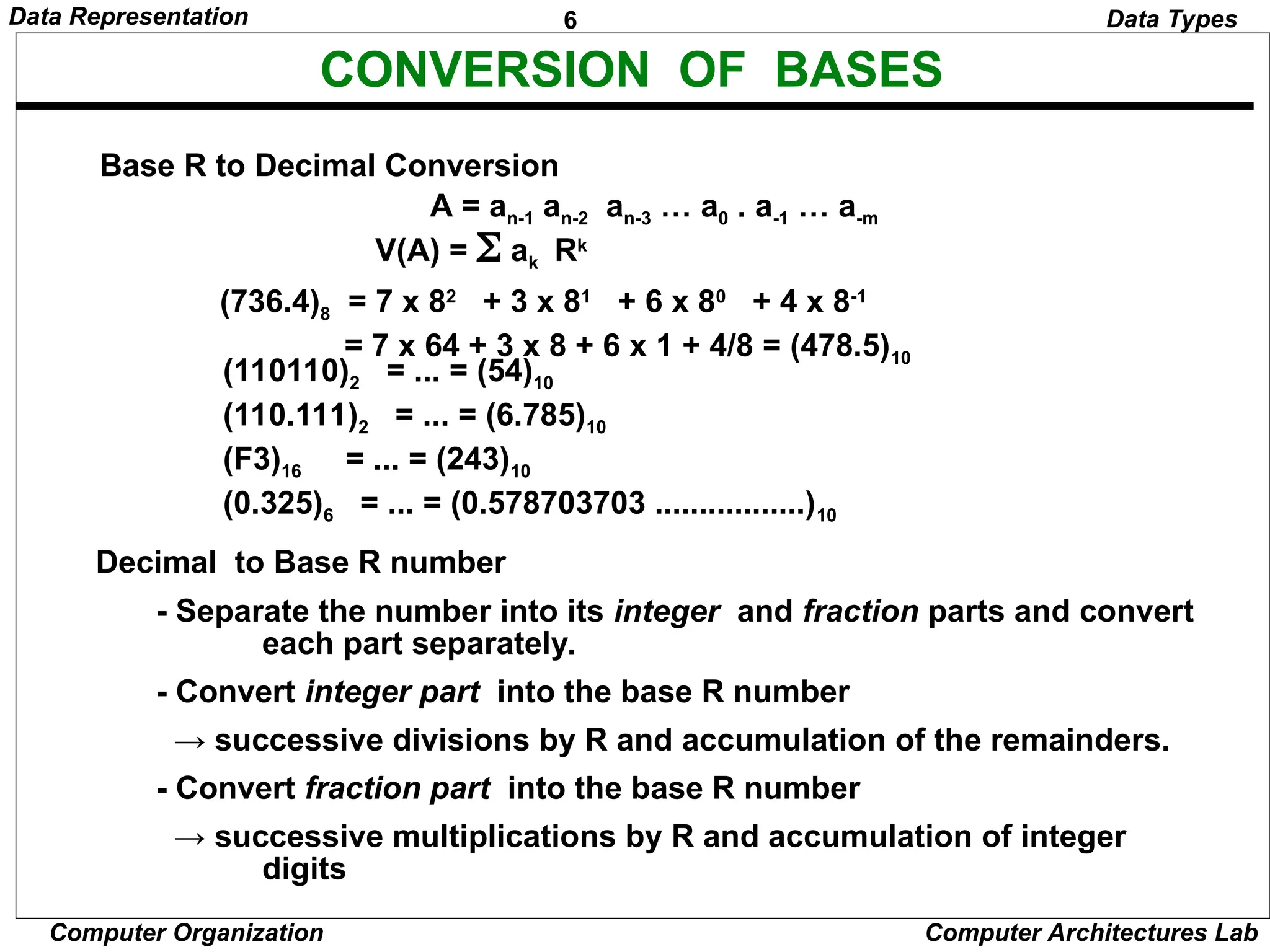

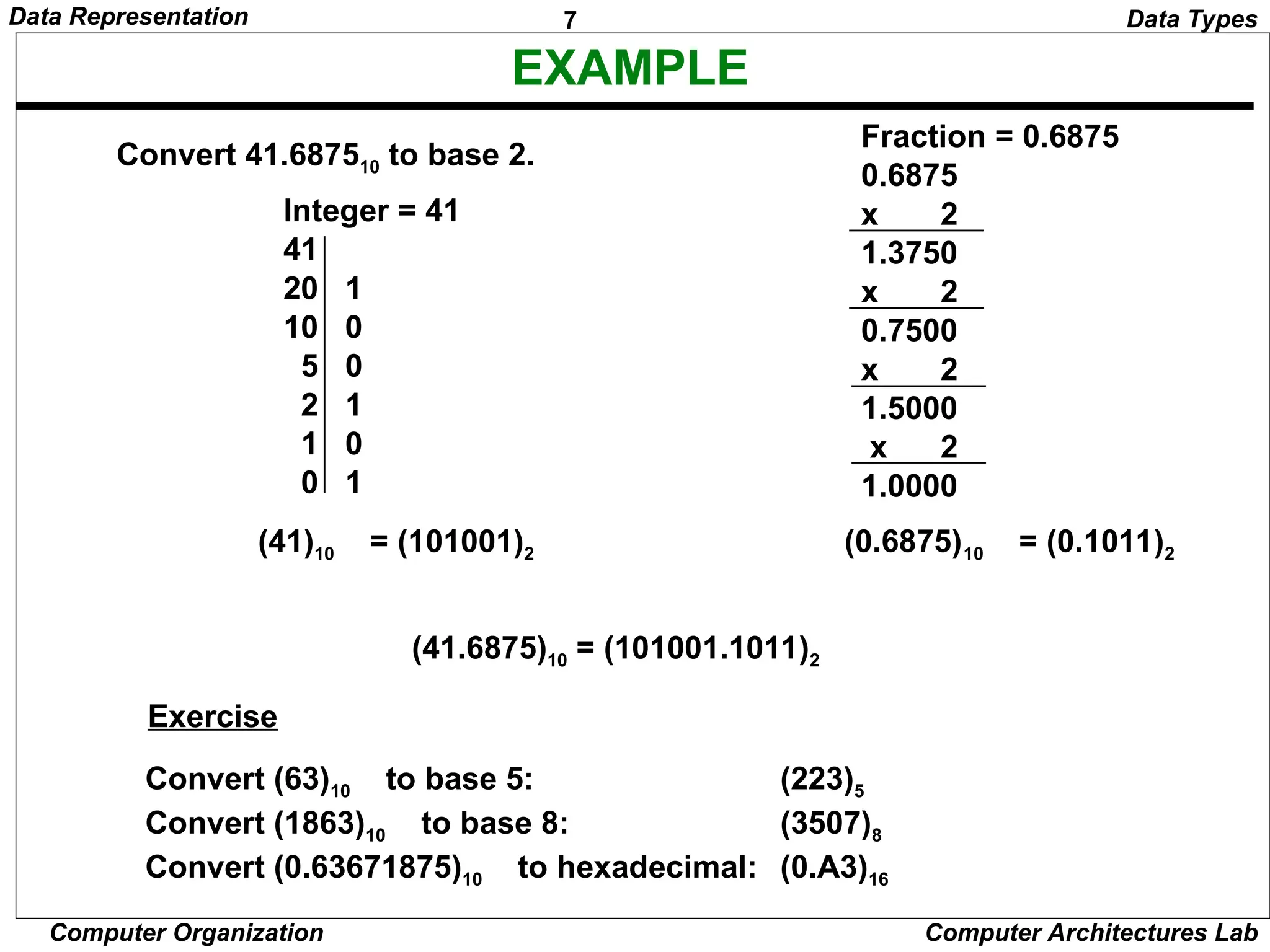

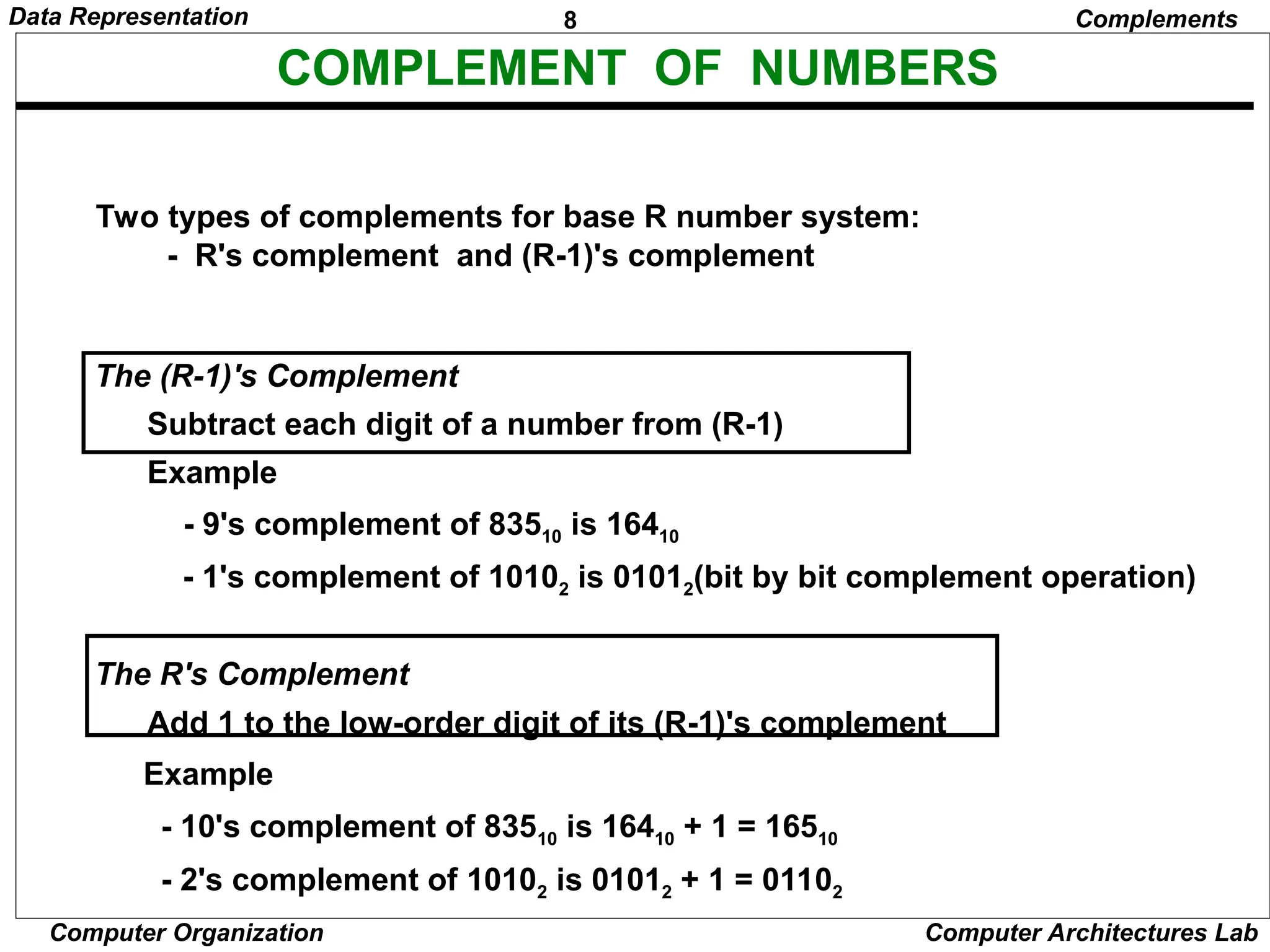

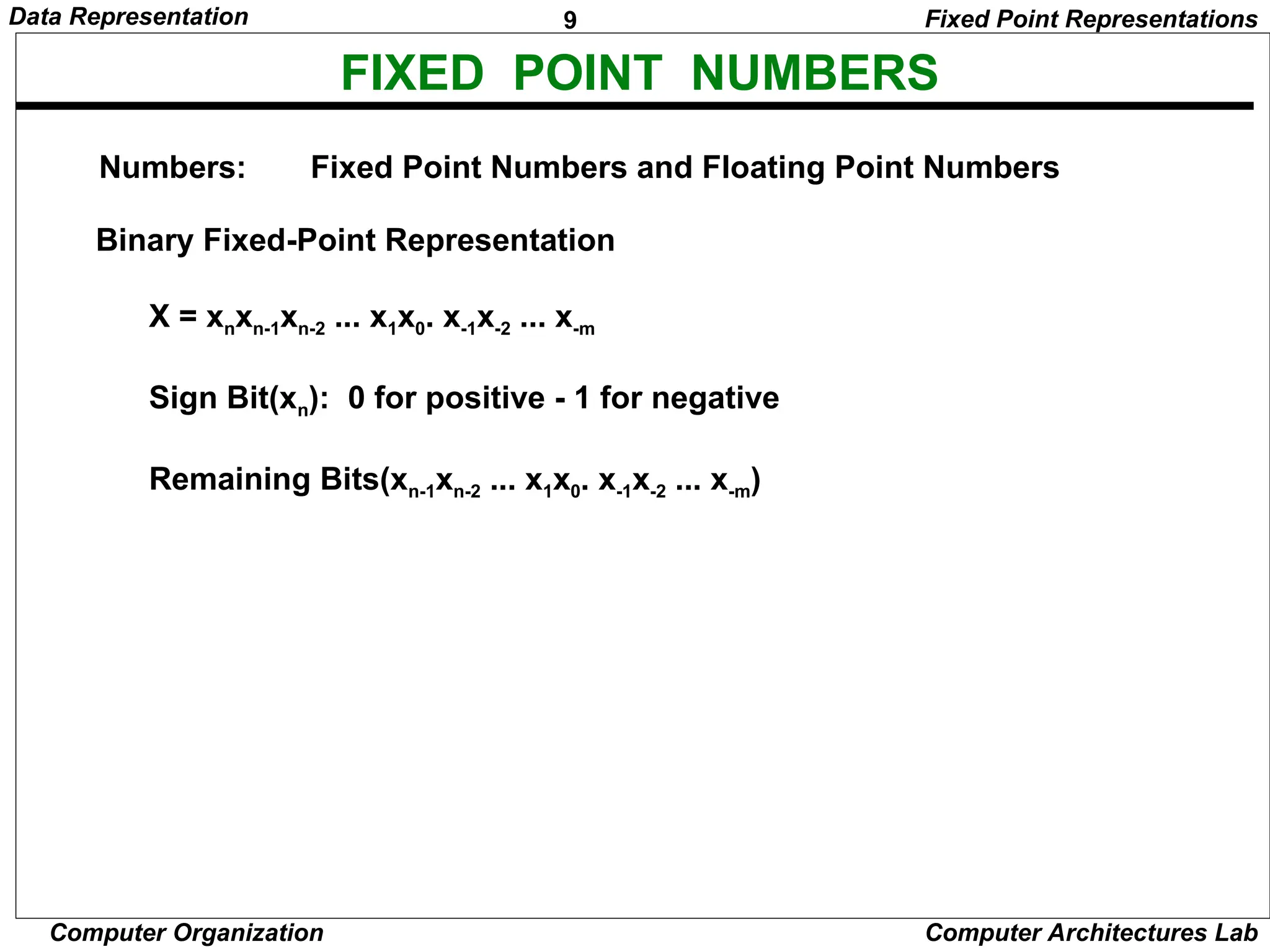

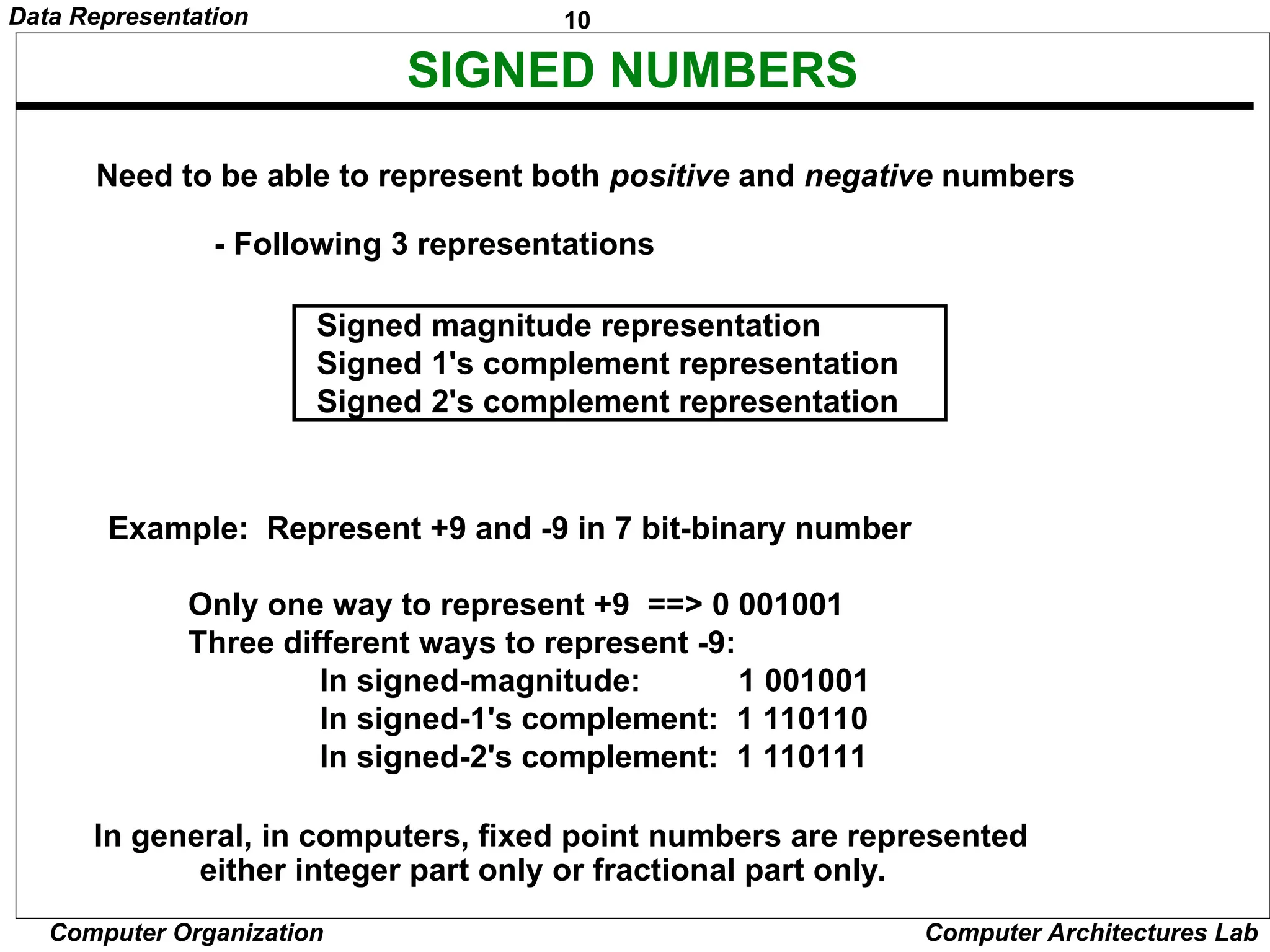

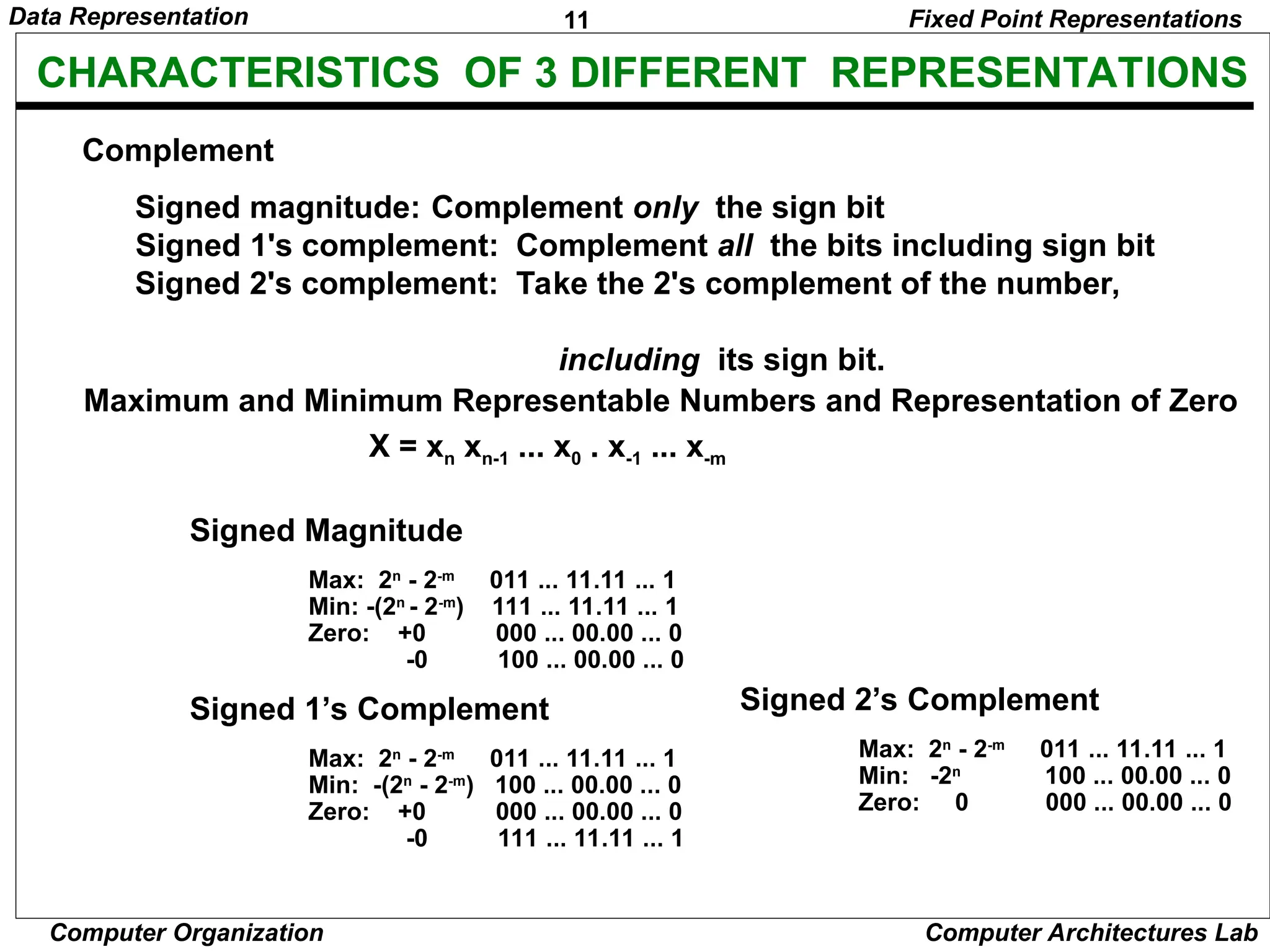

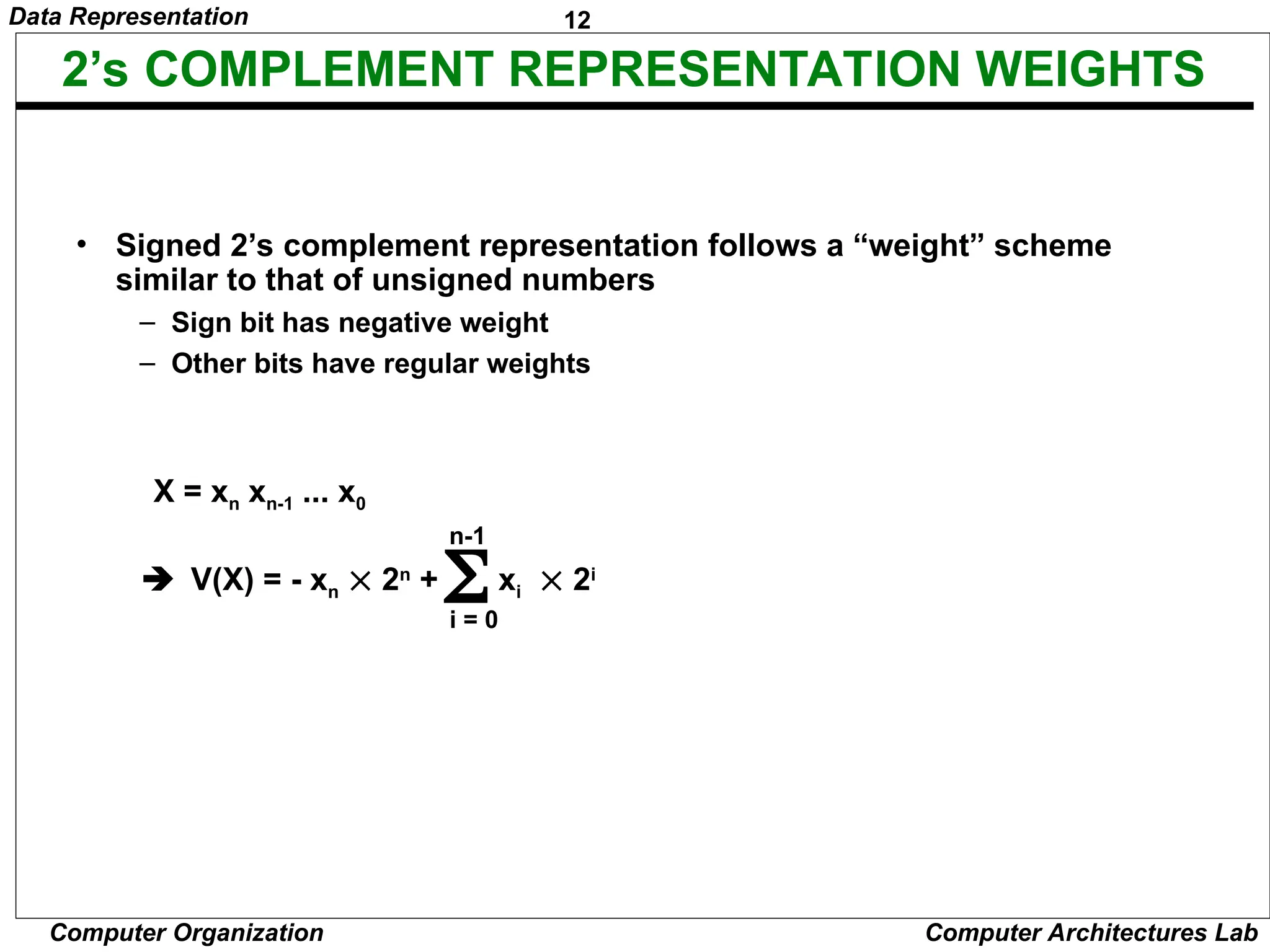

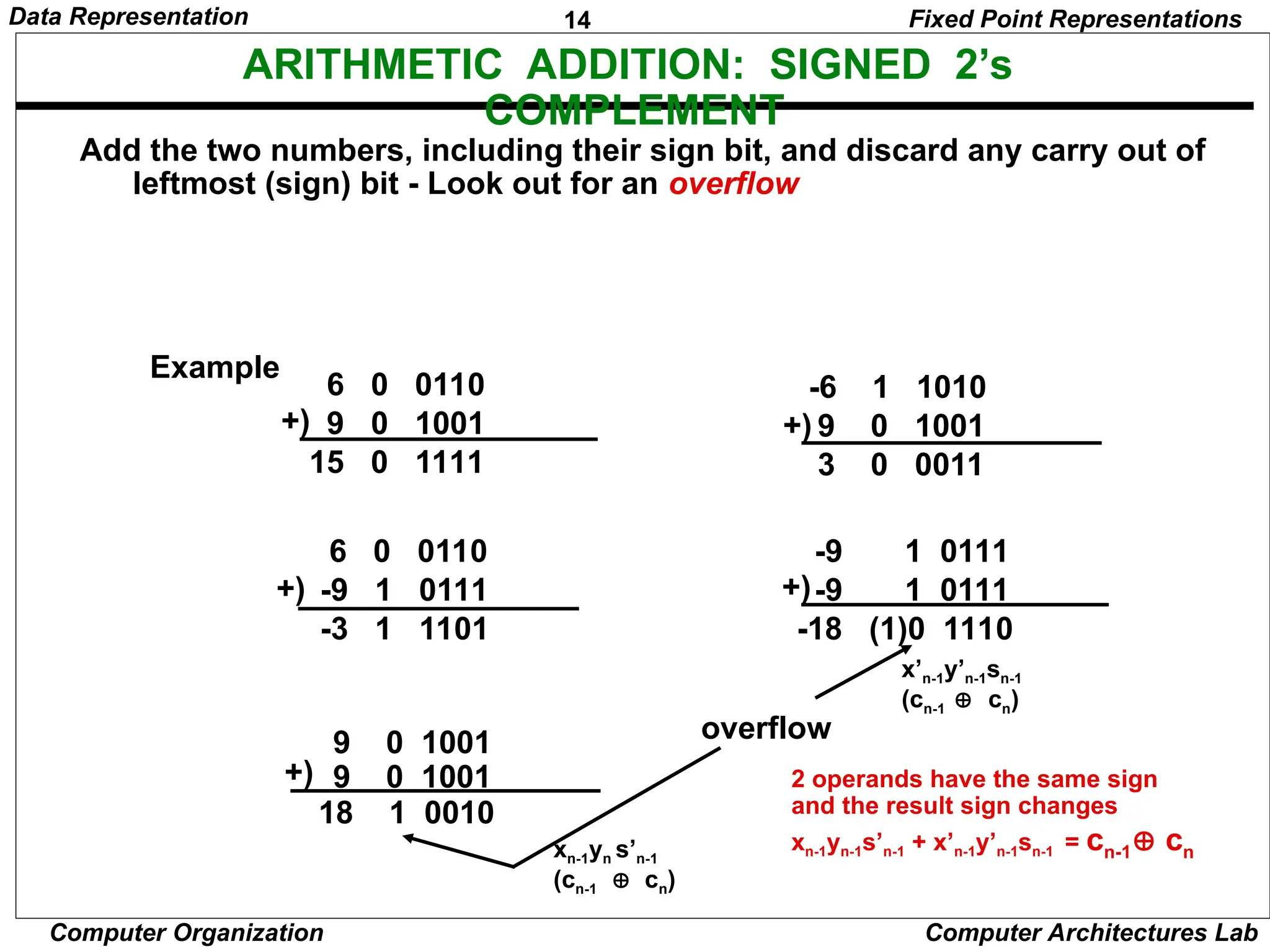

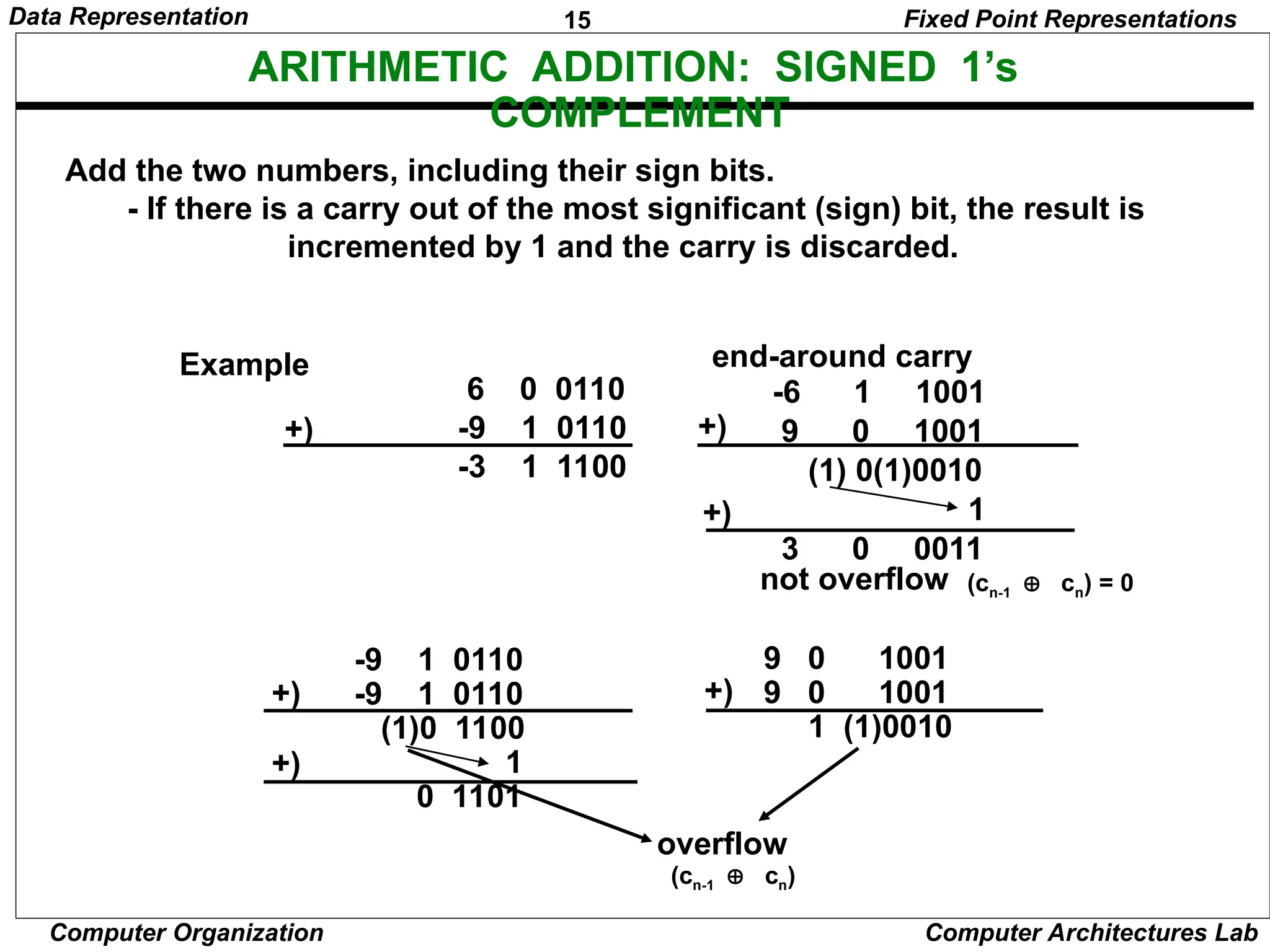

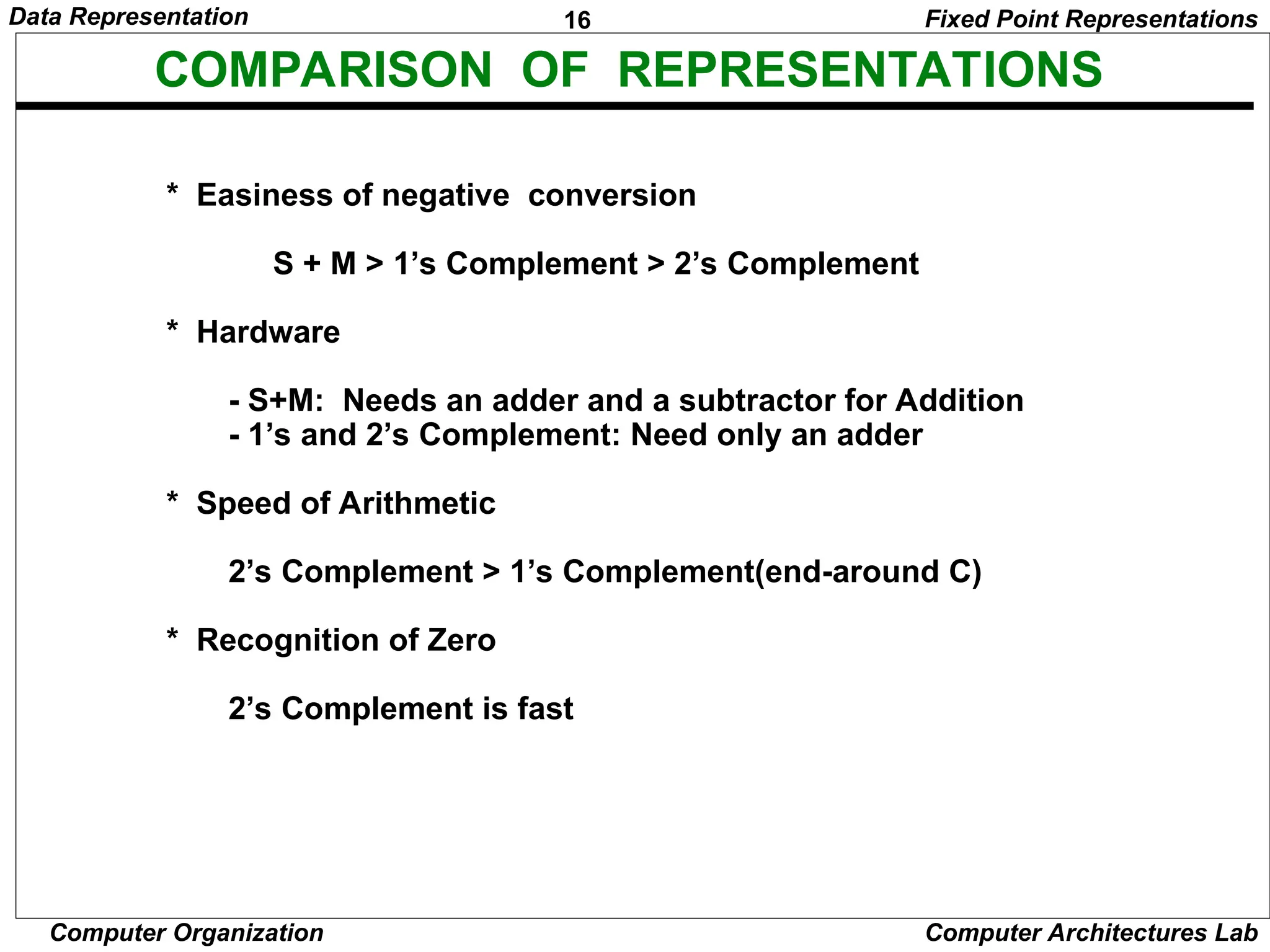

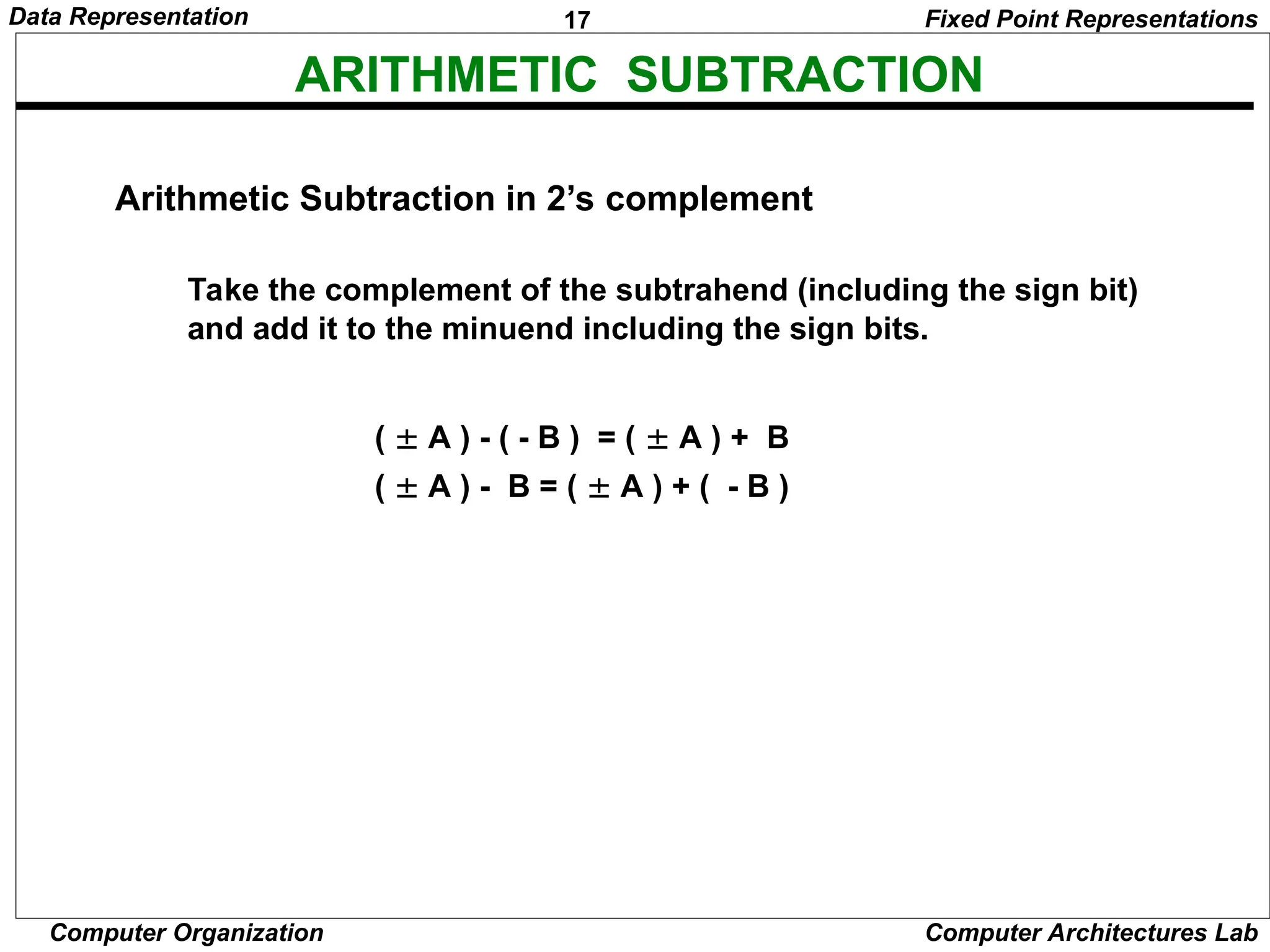

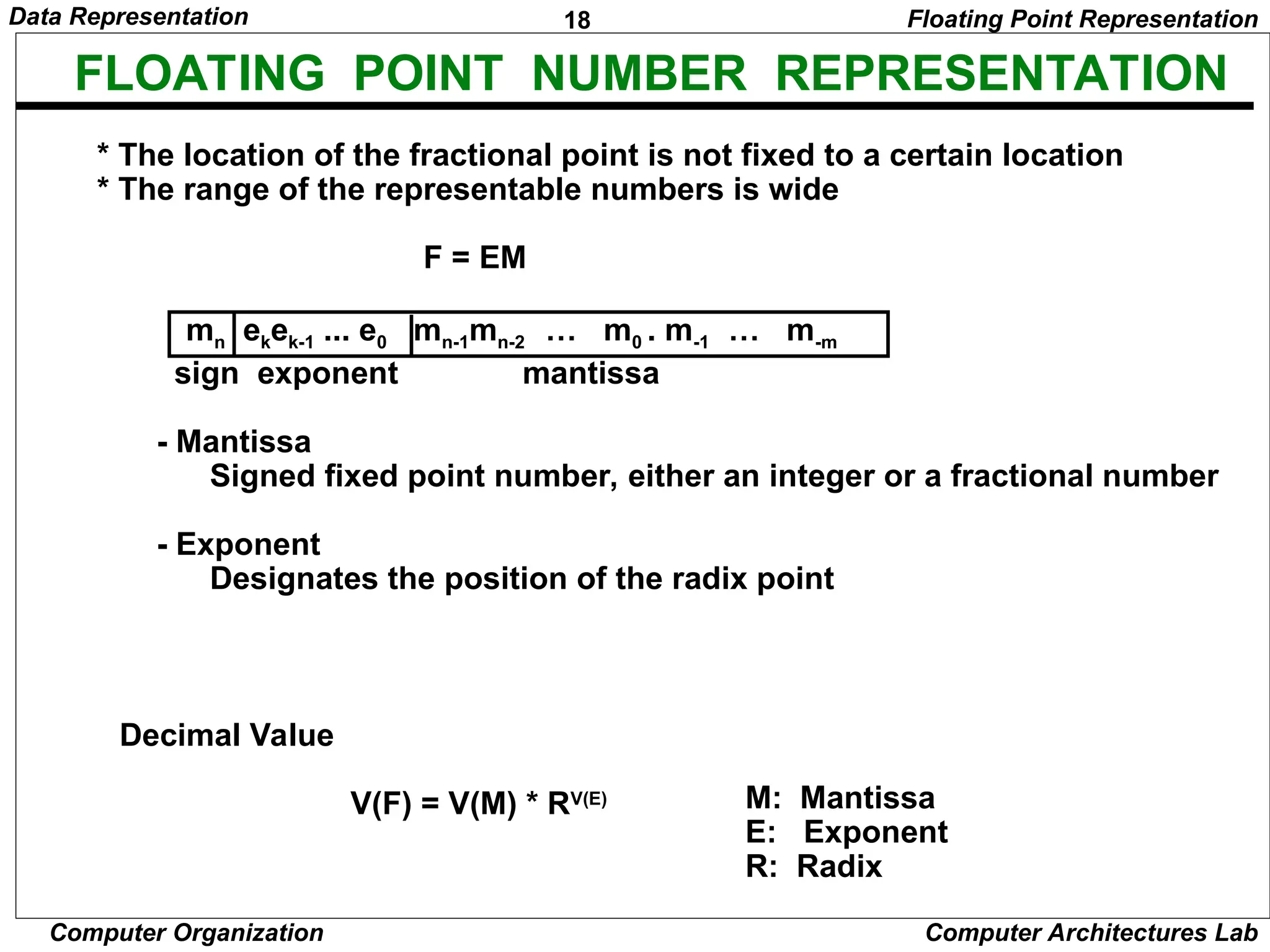

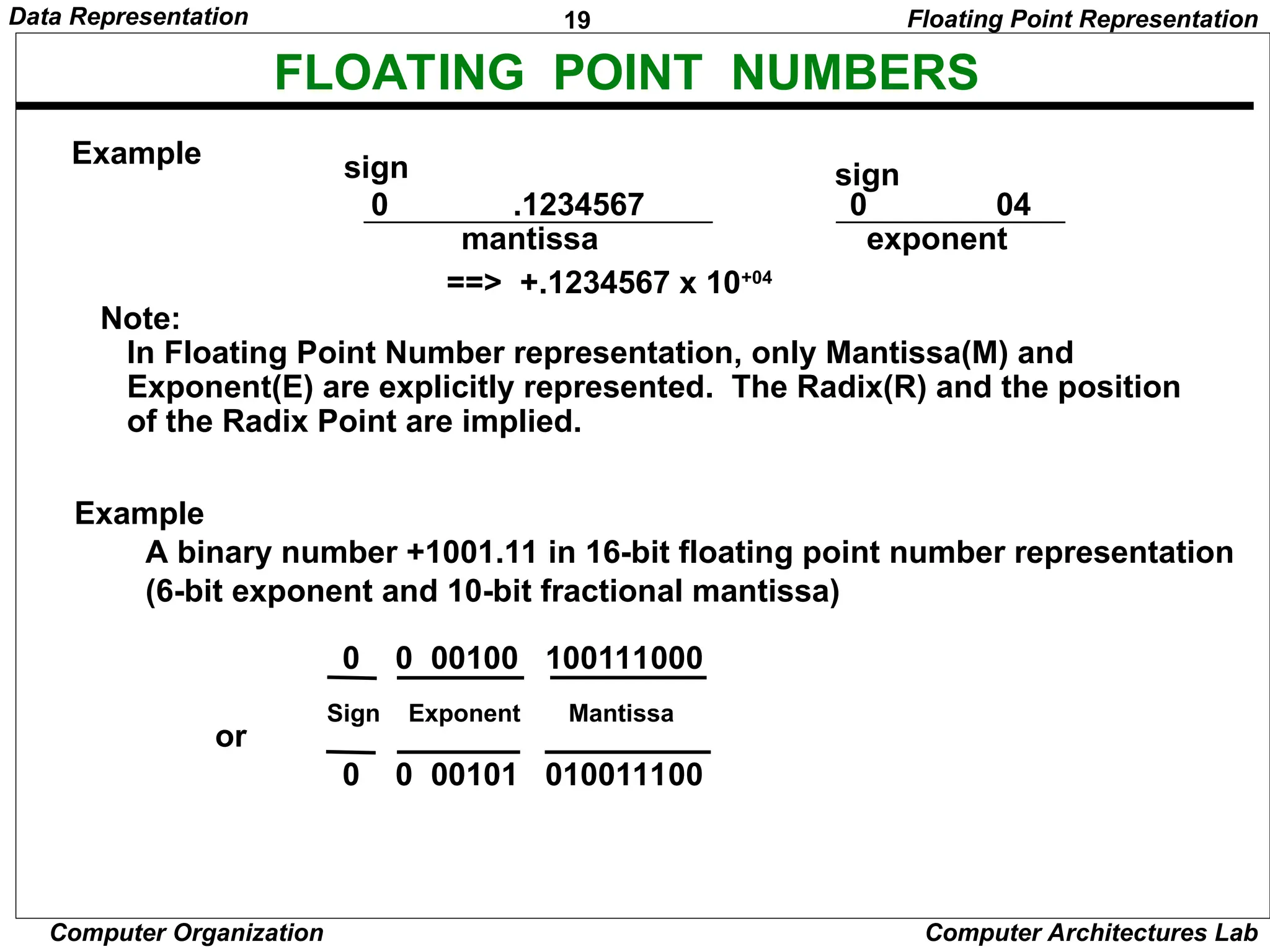

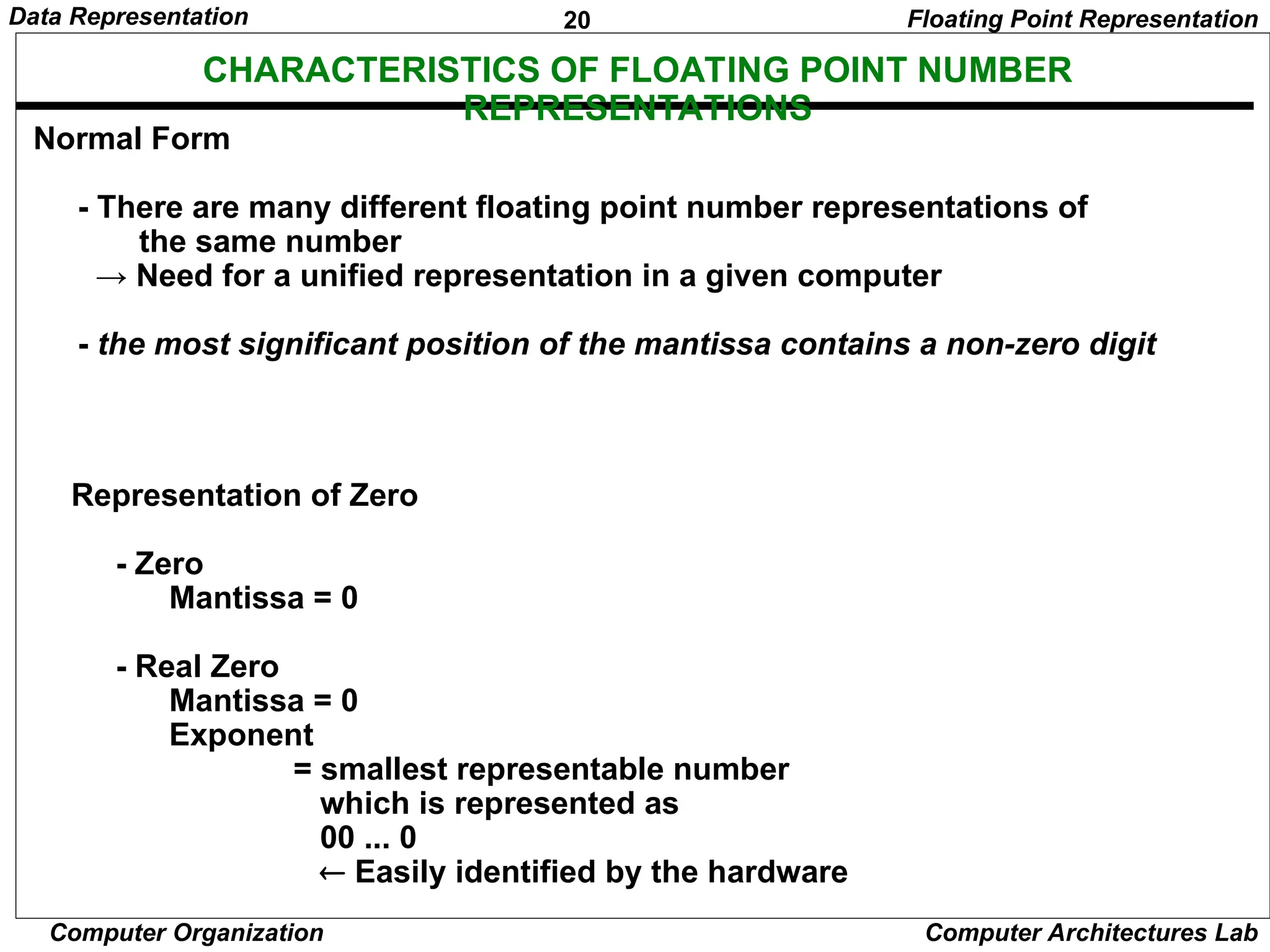

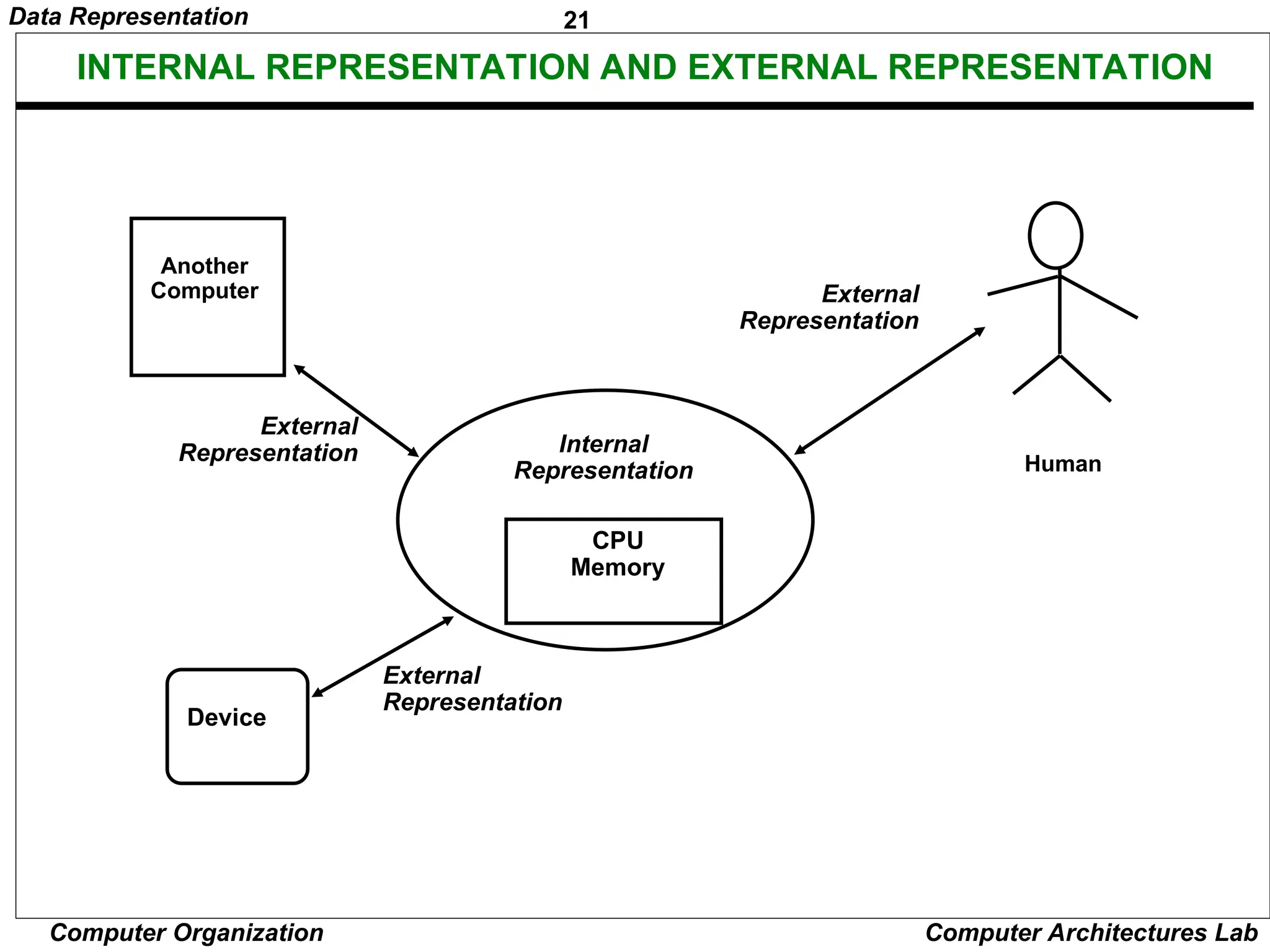

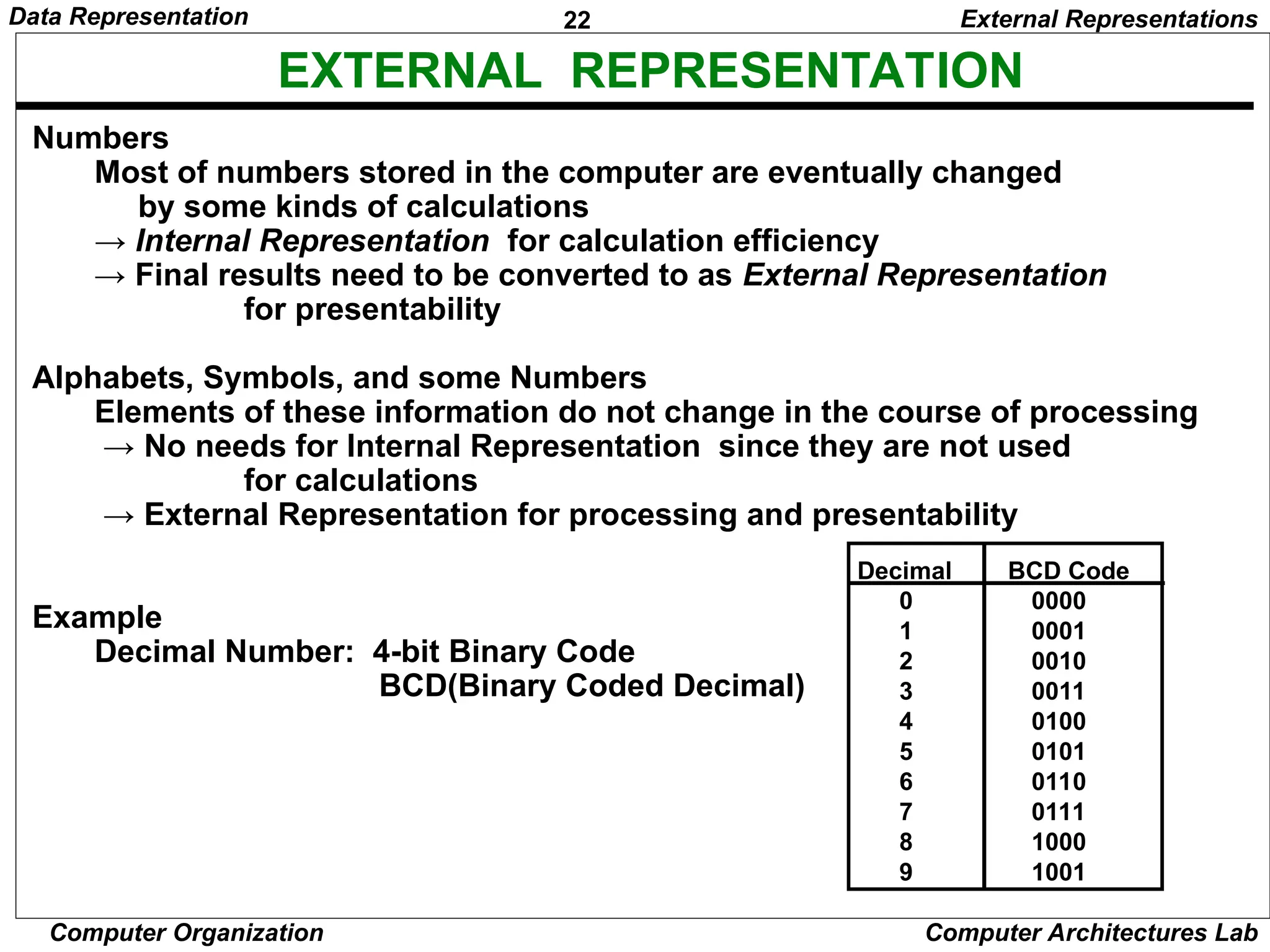

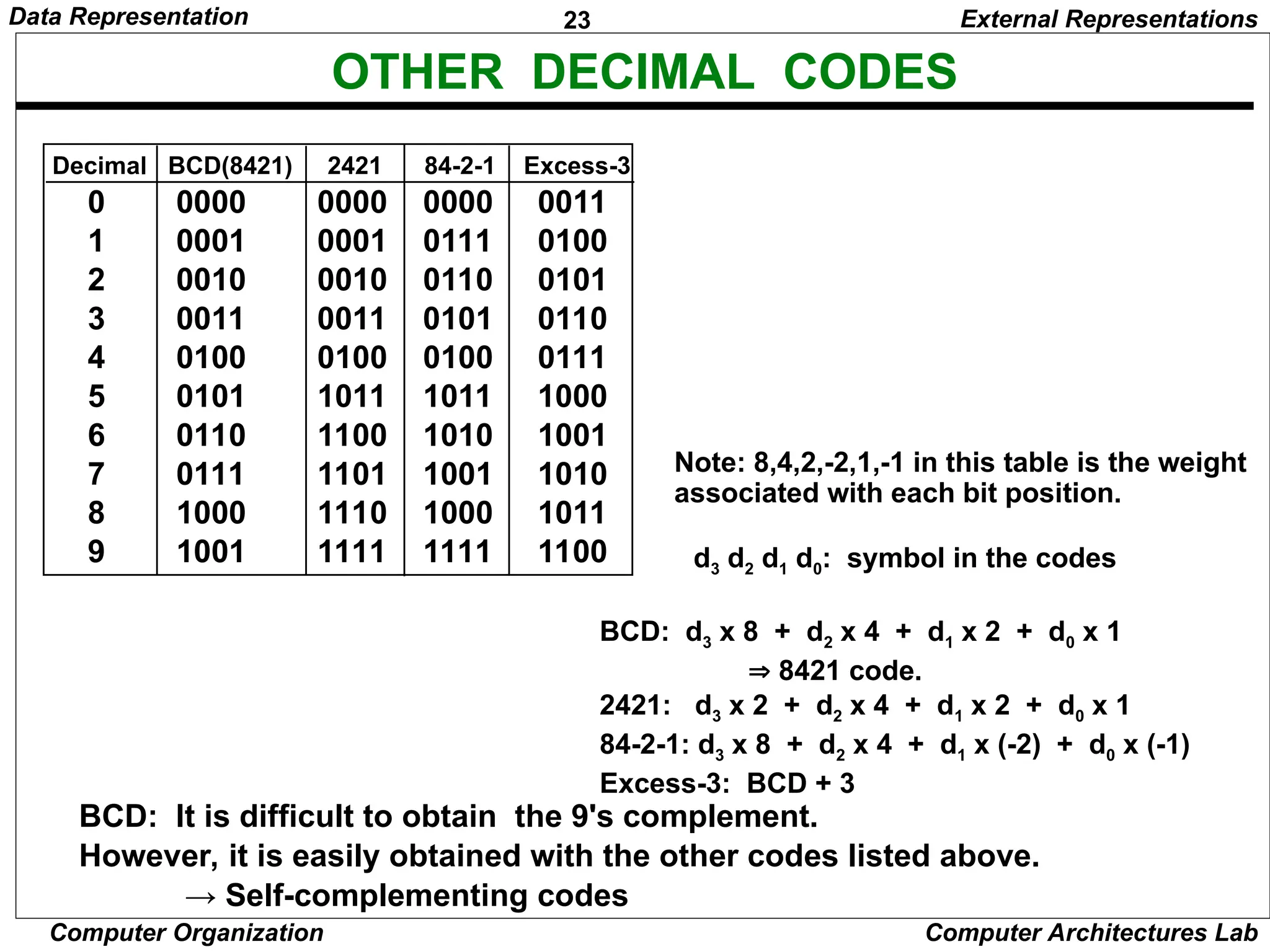

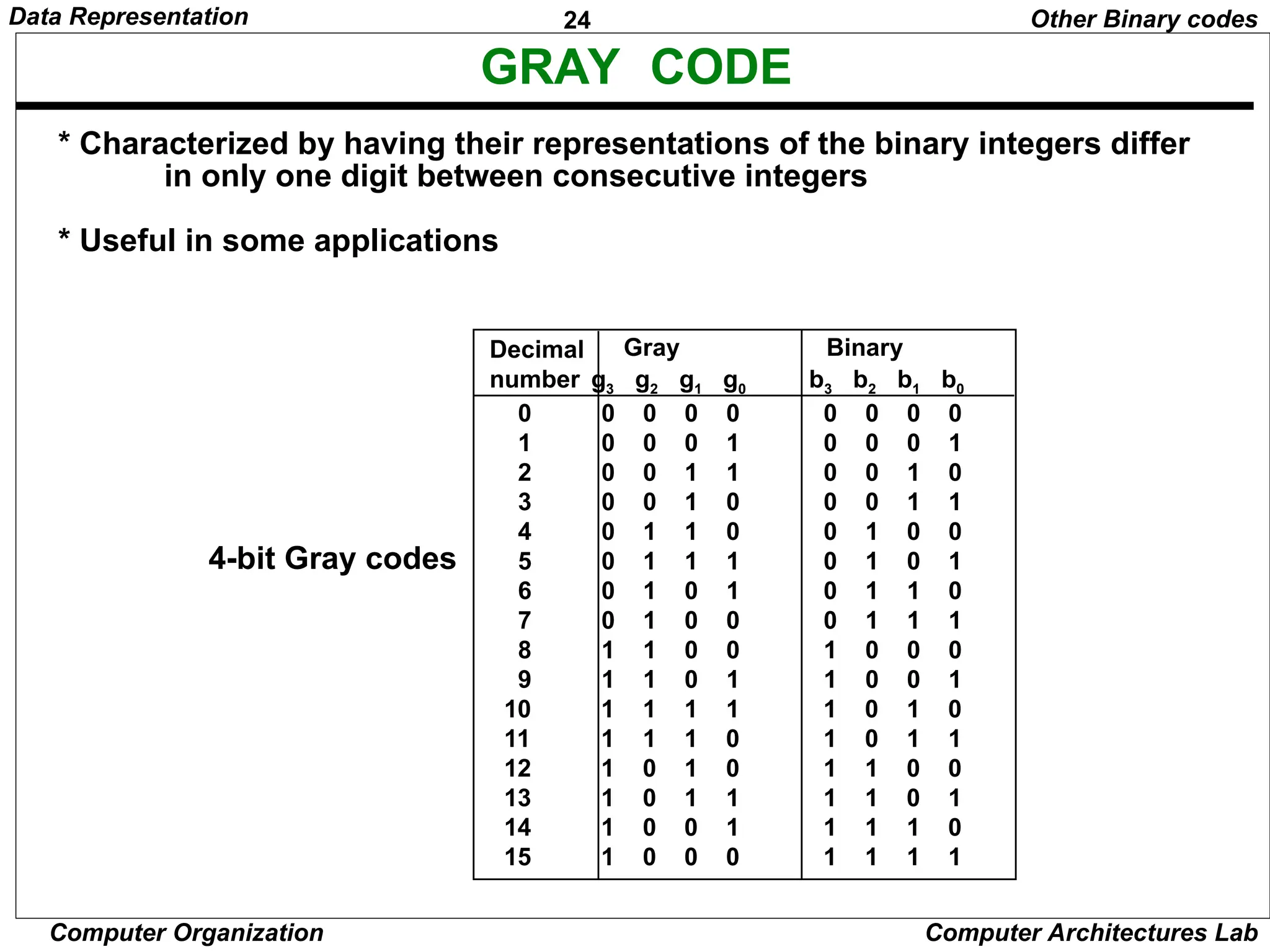

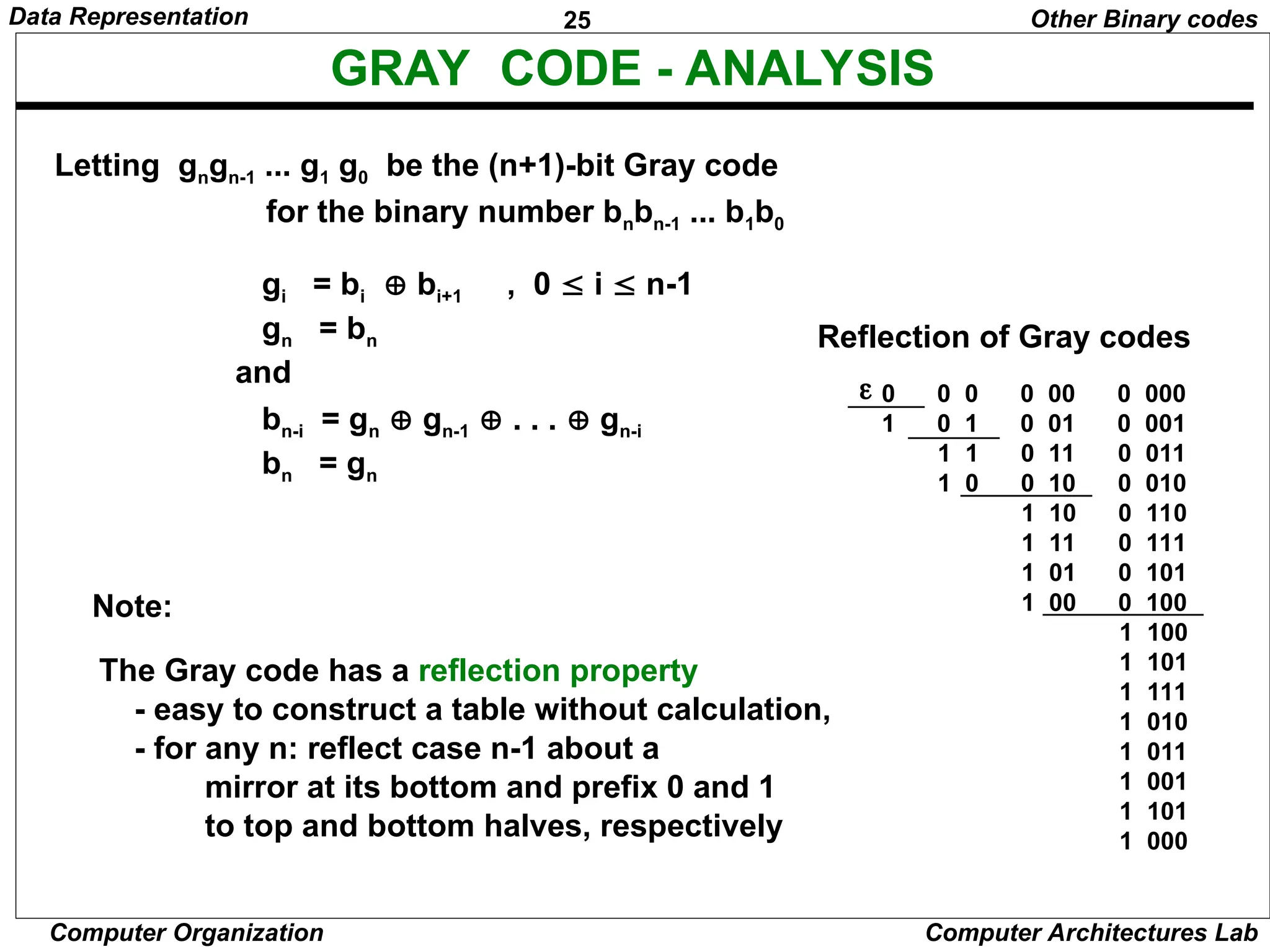

The document discusses data representation in computer organization and architectures, covering various number systems like binary, decimal, octal, and hexadecimal, as well as fixed and floating-point representations. It explains how data types interact within data structures, conversion between bases, complements, and methods for representing signed numbers. The document further elaborates on arithmetic operations and their implications in hardware design, alongside external representations for communication with devices and humans.

![13 Data Representation Computer Organization Computer Architectures Lab ARITHMETIC ADDITION: SIGNED MAGNITUDE [1] Compare their signs [2] If two signs are the same , ADD the two magnitudes - Look out for an overflow [3] If not the same , compare the relative magnitudes of the numbers and then SUBTRACT the smaller from the larger --> need a subtractor to add [4] Determine the sign of the result 6 0110 +) 9 1001 15 1111 -> 01111 9 1001 - ) 6 0110 3 0011 -> 00011 9 1001 -) 6 0110 - 3 0011 -> 10011 6 0110 +) 9 1001 -15 1111 -> 11111 6 + 9 -6 + 9 6 + (- 9) -6 + (-9) Overflow 9 + 9 or (-9) + (-9) 9 1001 +) 9 1001 (1)0010 overflow Fixed Point Representations](https://image.slidesharecdn.com/ch3-241208050620-b8e4909c/75/DATA-REPRESENTATIONS-and-Data-codes-and-formats-ppt-13-2048.jpg)

![26 Data Representation Computer Organization Computer Architectures Lab CHARACTER REPRESENTATION ASCII ASCII (American Standard Code for Information Interchange) Code Other Binary codes 0 1 2 3 4 5 6 7 8 9 A B C D E F NUL SOH STX ETX EOT ENQ ACK BEL BS HT LF VT FF CR SO SI SP ! “ # $ % & ‘ ( ) * + , - . / 0 1 2 3 4 5 6 7 8 9 : ; < = > ? @ A B C D E F G H I J K L M N O P Q R S T U V W X Y Z [ ] m n ‘ a b c d e f g h I j k l m n o P q r s t u v w x y z { | } ~ DEL 0 1 2 3 4 5 6 7 DLE DC1 DC2 DC3 DC4 NAK SYN ETB CAN EM SUB ESC FS GS RS US LSB (4 bits) MSB (3 bits)](https://image.slidesharecdn.com/ch3-241208050620-b8e4909c/75/DATA-REPRESENTATIONS-and-Data-codes-and-formats-ppt-26-2048.jpg)