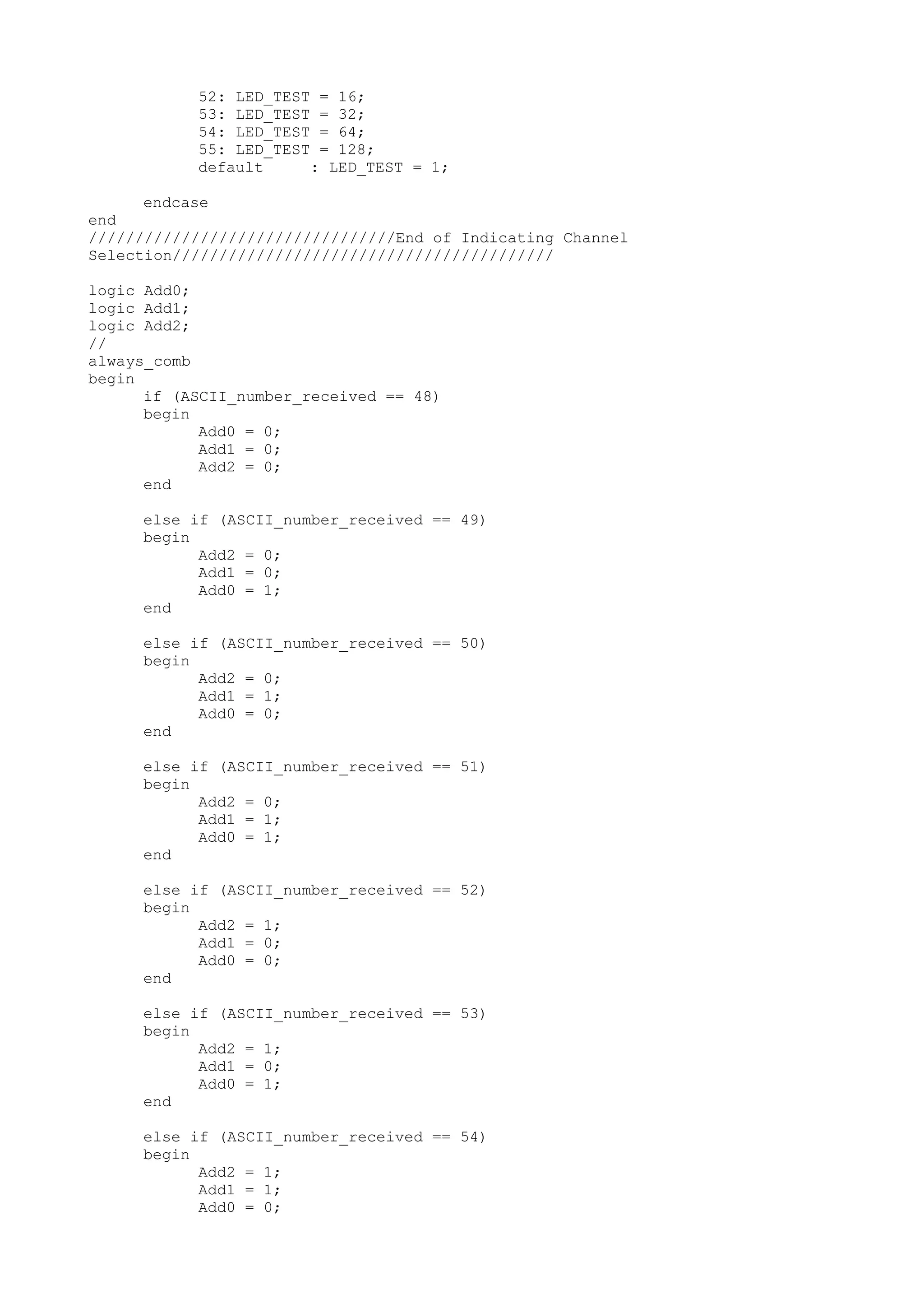

El módulo lab7 implementa una máquina de estados para controlar un sistema basado en temporización, que incluye la generación de señales de reloj y la lectura de datos de un ADC. Se organiza en varias máquinas de estado para gestionar la secuenciación de las señales de reloj, la cuenta de bits y la configuración de la salida en un display de siete segmentos. Además, el módulo convierte números binarios a ASCII y gestiona la salida de caracteres a través de un multiplexor.

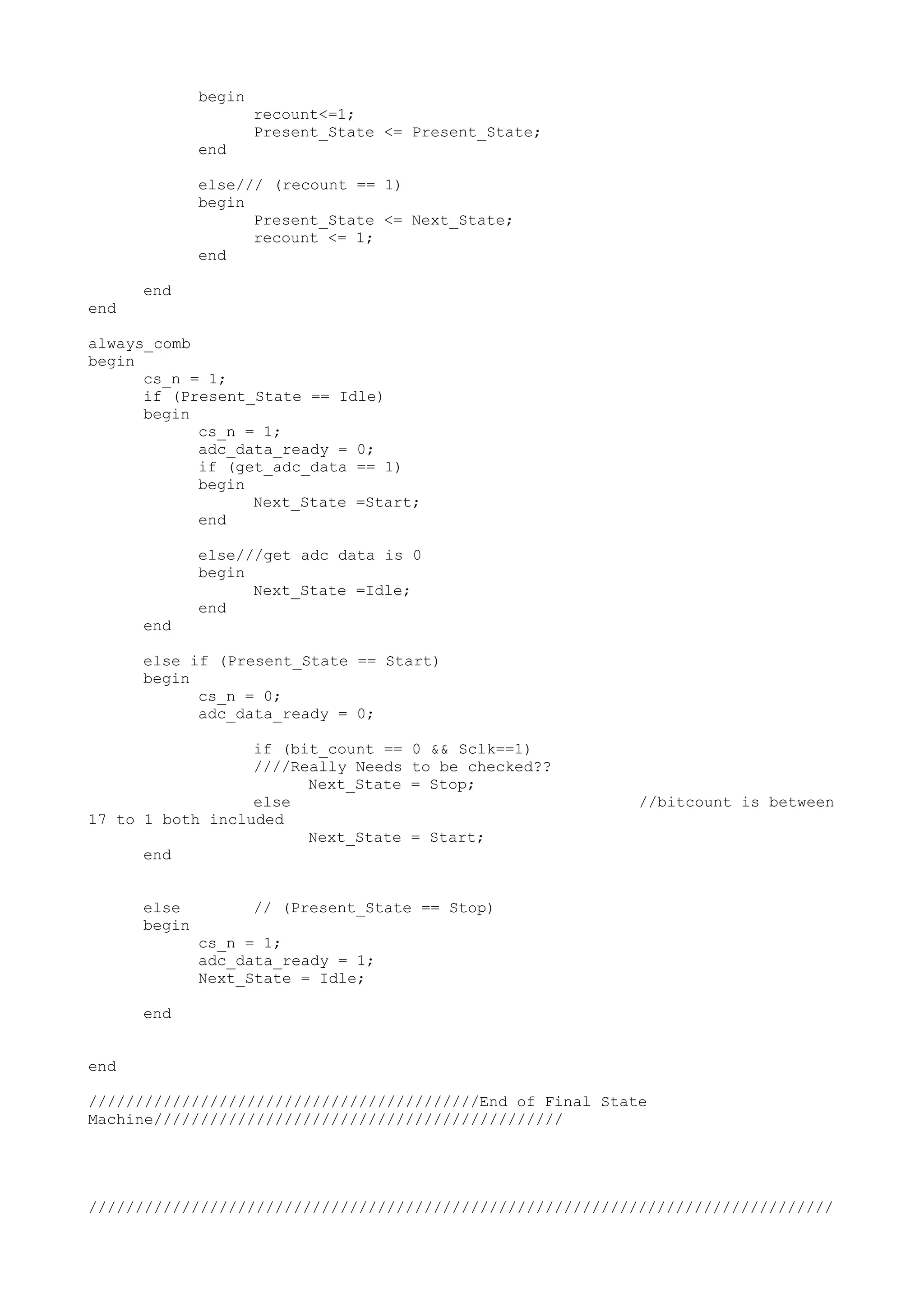

![module lab7( input logic inclk0_sig, input logic reset, output logic Sclk, output logic Din, output logic cs_n, output logic PC_Serial_data_output, output logic [6:0] seven_segment, output logic [2:0] sel, output reg en2, output reg en3, output logic pwm_out, output logic D_P, input logic TXD, output logic [7:0] LED_TEST, input logic Dout ); logic c0_sig; logic c1_sig; logic c2_sig; ////PLL// PLL PLL_inst ( .inclk0 ( inclk0_sig ), //50 MHz Input Clock .c0 ( c0_sig ), // 3 MHz .c1 ( c1_sig ), // 4 KHz Clock .c2 ( c2_sig ) //Baud Clock ); // //////////////////////////////////////////////////////////////////////////////// ////////////////// ///////////Making get adc as pule lasting for 0.5 secs but width of 3MHz clock///////////// //////////////////////////////////////////////////////////////////////////////// ////////////////// logic get_adc_data; // logic [20:0] number1; always_ff@(posedge c0_sig or negedge reset) begin if (!reset) begin get_adc_data <=0; number1<= 0; end else begin](https://image.slidesharecdn.com/voltmentercode-160614052306/75/Digital-Voltmeter-displaying-voltage-level-on-a-seven-segment-display-and-computer-1-2048.jpg)

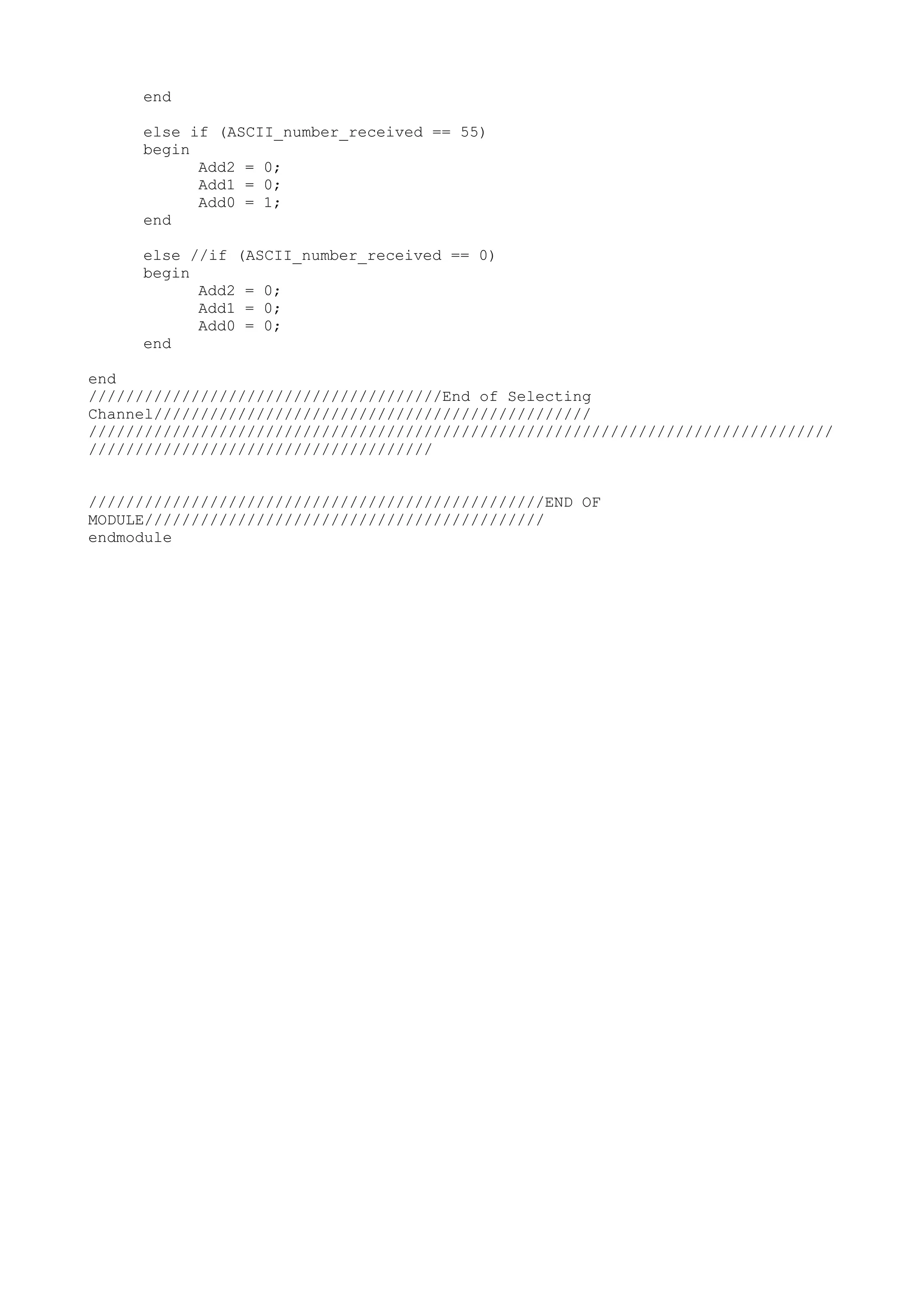

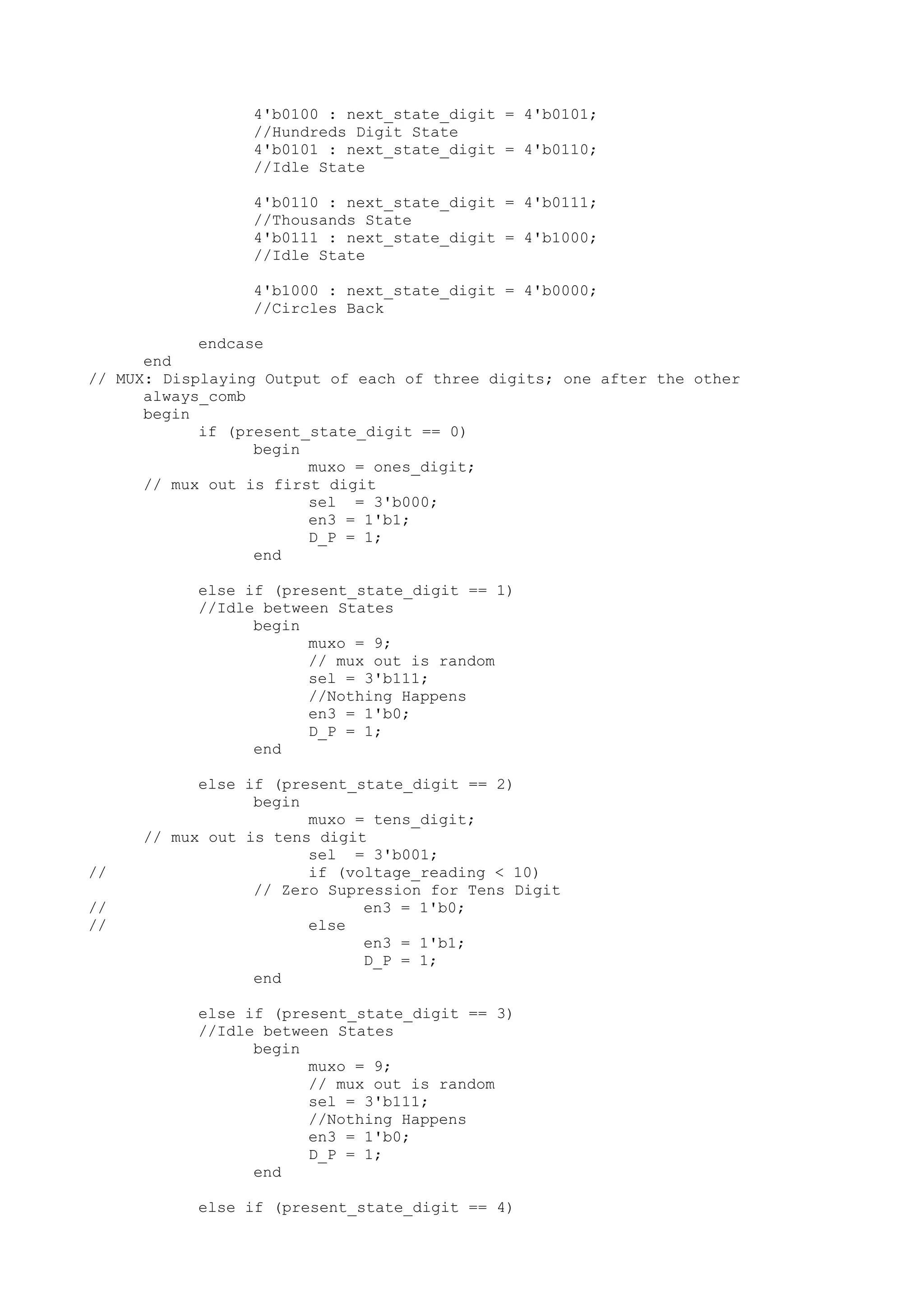

![if (number1 == 0) begin get_adc_data <= 1; end else if (number1 == 1) begin get_adc_data <= 0; end else if (number1 == 1500000)//3 or above begin number1 <= 0; get_adc_data <= 1; end number1 <= number1 +1; end end /////////////////////////////////End of making a getadc pulse////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// /////////////////// ///////////////////////State Machine for Sclk////////////////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////// logic [1:0] tecount; // always_ff@(posedge c0_sig or negedge reset) begin if (!reset) begin Sclk <= 1; tecount <=0; end else begin if (tecount <2) begin tecount <= tecount+1; Sclk <= Sclk; end else ///tecount hits 2 begin tecount <= tecount; ////tecount stays at 2 if (Sclk==1) begin if (Present_State == Start) Sclk <= ~Sclk; else ///Sclk present state is anything else like stop or idle Sclk <= Sclk;](https://image.slidesharecdn.com/voltmentercode-160614052306/75/Digital-Voltmeter-displaying-voltage-level-on-a-seven-segment-display-and-computer-2-2048.jpg)

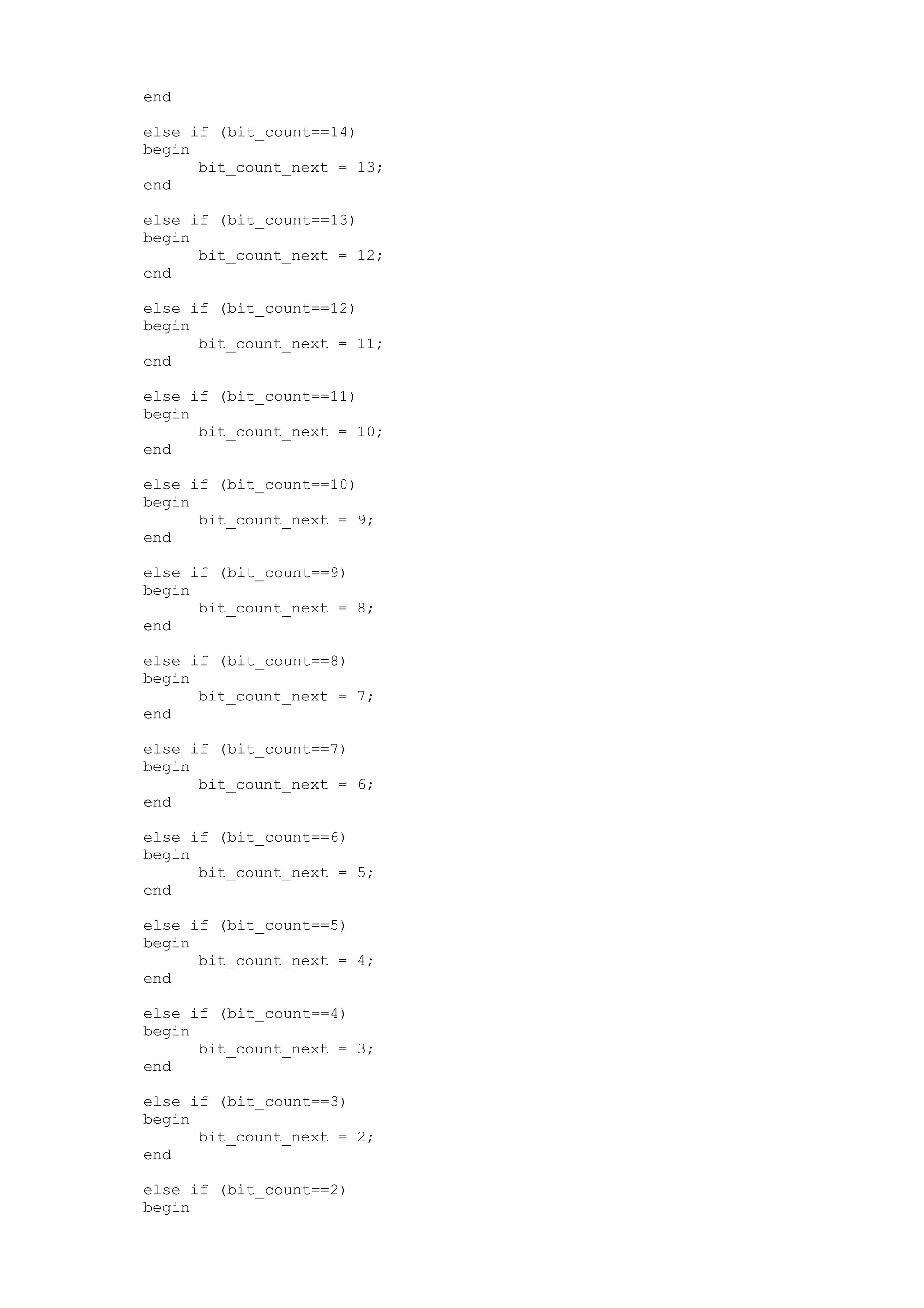

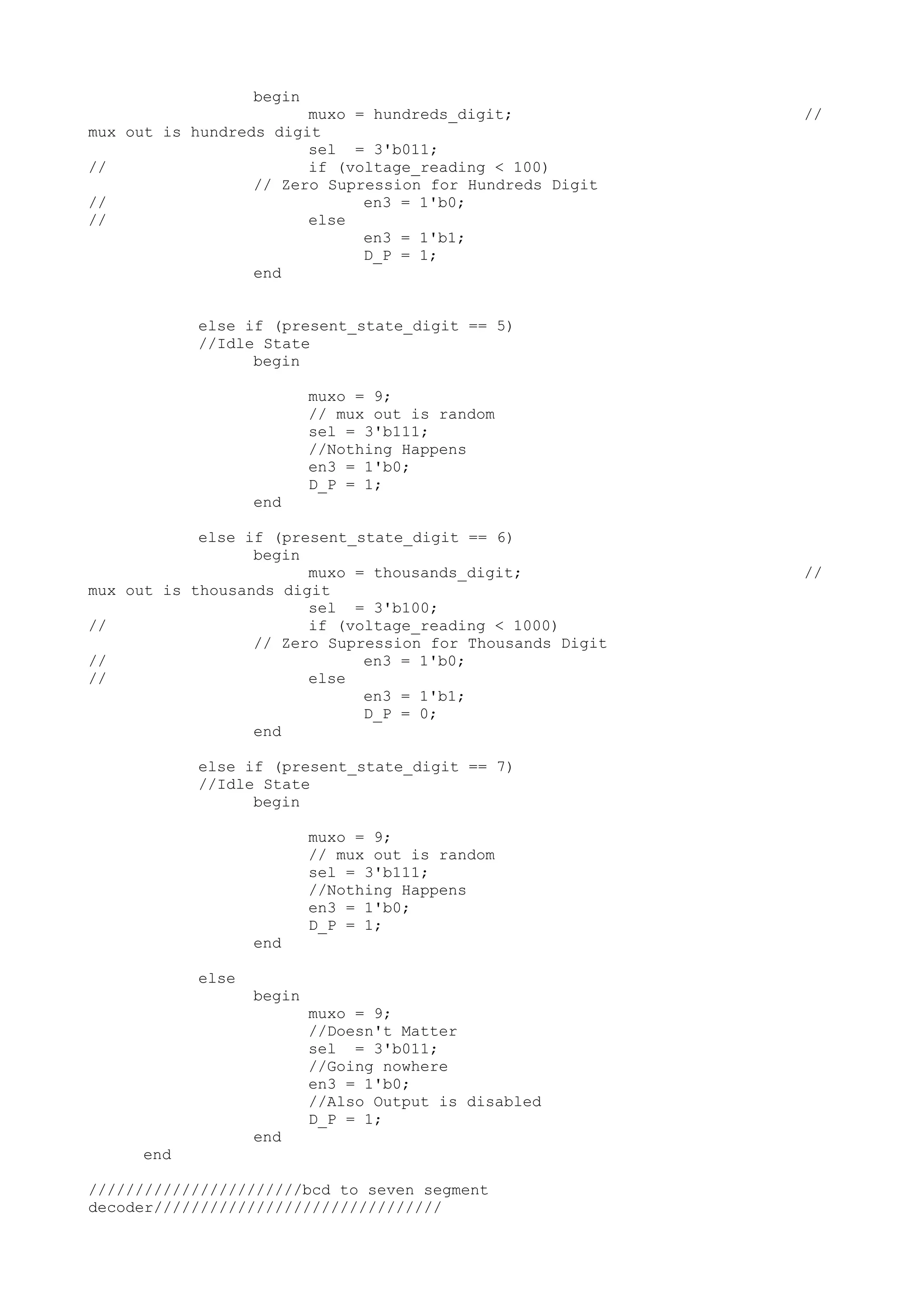

![end else////Sclk is a zero begin Sclk <= ~Sclk; end end end end ////////////////////////End of State Machine 1///////////////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////// ///////////////////////State Machine for Bitcount////////////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////// logic [4:0] bit_count; logic [4:0] bit_count_next; // always_ff@(negedge Sclk or negedge reset) begin if (!reset) begin bit_count <= 17; bit_count_next <= 16; ///Sclk <= 1; end else begin bit_count <= bit_count_next; end bit_count_next <= bit_count_next; end always_comb begin if (bit_count==17) begin ////Do we really need this? if (Sclk==1 && Present_State == Start) bit_count_next = 16; else bit_count_next = 17; end else if (bit_count==16) begin bit_count_next = 15; end else if (bit_count==15) begin bit_count_next = 14;](https://image.slidesharecdn.com/voltmentercode-160614052306/75/Digital-Voltmeter-displaying-voltage-level-on-a-seven-segment-display-and-computer-3-2048.jpg)

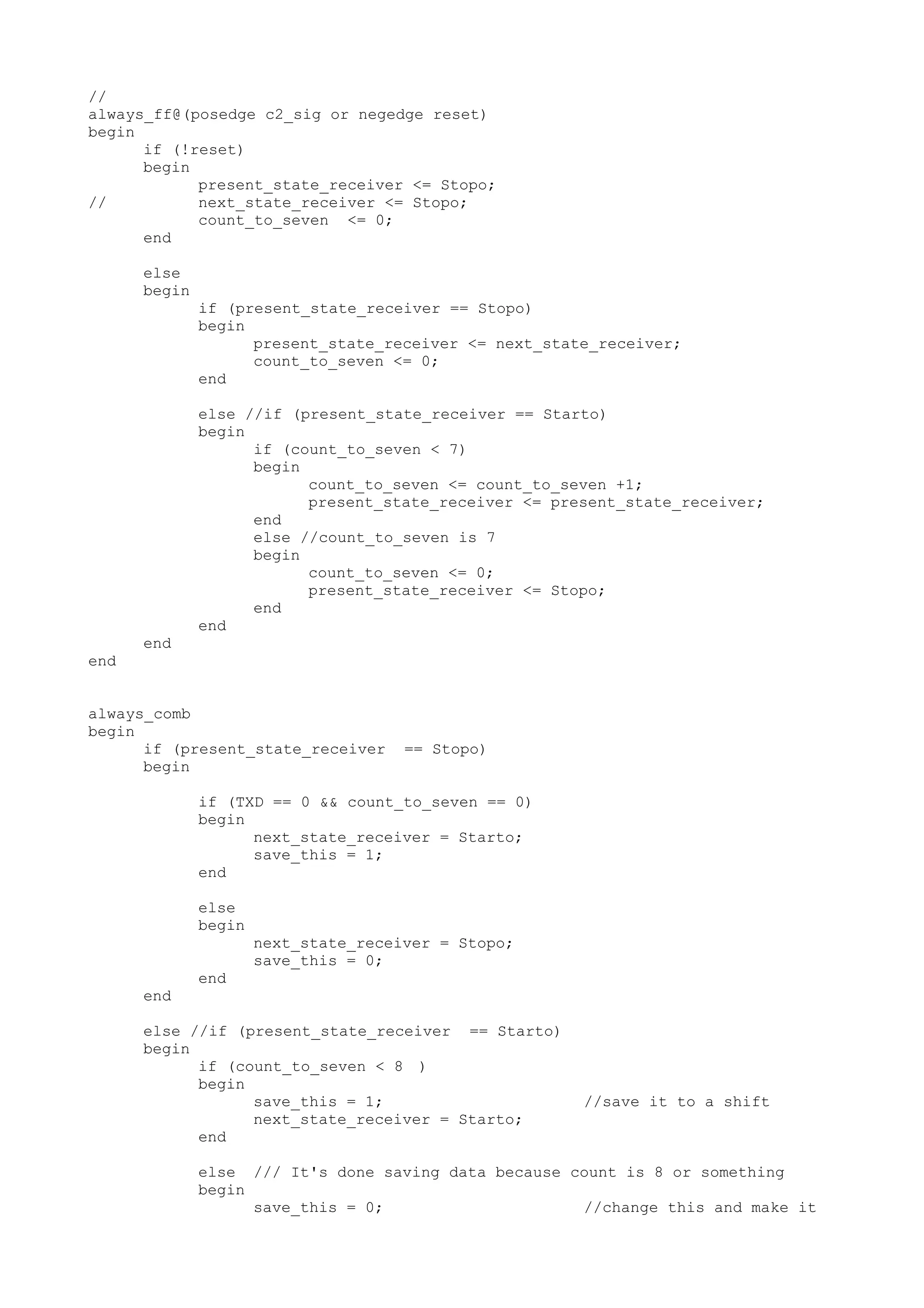

![////////////////////////////////////////// ////////////////////////////////////////////Shift Register///////////////////////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// /////////////////////////////////////// //logic bit_enabled; // //always_ff@(posedge Sclk) //begin // if (bit_count < 13) // bit_enabled <= 1; // else // bit_enabled <= 0; //end // //always_ff@(posedge Sclk or negedge reset) //begin // if (!reset) // begin // voltage_value_address<=0; // end // // else // begin // if (bit_enabled) // voltage_value_address<= {voltage_value_address[10:0], Dout}; // end //end logic [11:0] voltage_value_address; always_ff@(posedge Sclk or negedge reset) begin if (!reset) begin voltage_value_address<=0; end else begin if (bit_count == 12) begin voltage_value_address[11] <= Dout; end else if (bit_count == 11) begin voltage_value_address[10] <= Dout; end else if (bit_count == 10) begin voltage_value_address[9] <= Dout; end else if (bit_count == 9) begin voltage_value_address[8] <= Dout; end else if (bit_count == 8) begin voltage_value_address[7] <= Dout;](https://image.slidesharecdn.com/voltmentercode-160614052306/75/Digital-Voltmeter-displaying-voltage-level-on-a-seven-segment-display-and-computer-7-2048.jpg)

![end else if (bit_count == 7) begin voltage_value_address[6] <= Dout; end else if (bit_count == 6) begin voltage_value_address[5] <= Dout; end else if (bit_count == 5) begin voltage_value_address[4] <= Dout; end else if (bit_count == 4) begin voltage_value_address[3] <= Dout; end else if (bit_count == 3) begin voltage_value_address[2] <= Dout; end else if (bit_count == 2) begin voltage_value_address[1] <= Dout; end else if (bit_count == 1) begin voltage_value_address[0] <= Dout; end end end ///////////////////////////////////End of Shift Register//////////////////////////////////////////////////////////////////////// ///////// //////////////////////////////////////////////////////////////////////////////// /////////////////////////////////////////////////// ////////////////////////////////////ROM///////////////////////////////////////// ////////////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////////////////////////// wire clock_sig = get_adc_data; ///Rom Updation occurs once in 0.5secs(not system clock?) //wire address_sig = voltage_value_address; logic [11:0] voltage_reading; // Rom_for_voltage_levels Rom_for_voltage_levels_inst ( .address ( voltage_value_address ), .clock ( clock_sig ), .q ( voltage_reading ) );](https://image.slidesharecdn.com/voltmentercode-160614052306/75/Digital-Voltmeter-displaying-voltage-level-on-a-seven-segment-display-and-computer-8-2048.jpg)

![//////////////////////////////////End of ROM///////////////////////////////////////////////////////////////////////////// ////////////////// //////////////////////////////////////////////////////////////////////////////// ///// /////////////////////////////Separating digits///////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// /// logic [3:0] thousands_digit; logic [3:0] hundreds_digit; logic [3:0] tens_digit; logic [3:0] ones_digit; assign en2 = 1'b0; assign pwm_out = 1'b0; always@(posedge inclk0_sig) begin thousands_digit = voltage_reading/1000; hundreds_digit = (voltage_reading%1000)/100; tens_digit = ((voltage_reading%1000)%100)/10; ones_digit = ((voltage_reading%1000)%100)%10; end ////////////////////////////////////End of Separtaing deigits//////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// /////////////// ///////////////// State Machine present state of digit becomes new state every clock edge/////////////// //////////////////////////////////////////////////////////////////////////////// /////////////// logic [3:0] muxo; logic [3:0] present_state_digit; logic [3:0] next_state_digit; // always_ff@(posedge c1_sig) present_state_digit <= next_state_digit; ///Saving the state //////////////Making it go to the next state. Incrementing present state///////////////////// always_comb begin unique case (present_state_digit) 4'b0000 : next_state_digit = 4'b0001; //Ones Digit State 4'b0001 : next_state_digit = 4'b0010; //Idle State 4'b0010 : next_state_digit = 4'b0011; //Tens Digit State 4'b0011 : next_state_digit = 4'b0100; //Idle State](https://image.slidesharecdn.com/voltmentercode-160614052306/75/Digital-Voltmeter-displaying-voltage-level-on-a-seven-segment-display-and-computer-9-2048.jpg)

![always_comb begin casez (muxo) //gfedcba 4'b0000 : seven_segment = 7'b1000000; //seven segment display of 0 4'b0001 : seven_segment = 7'b1111001; //seven segment display of 1 4'b0010 : seven_segment = 7'b0100100; //seven segment display of 2 4'b0011 : seven_segment = 7'b0110000; //seven segment display of 3 4'b0100 : seven_segment = 7'b0011001; //seven segment display of 4 4'b0101 : seven_segment = 7'b0010010; //seven segment display of 5 4'b0110 : seven_segment = 7'b0000010; //seven segment display of 6 4'b0111 : seven_segment = 7'b1111000; //seven segment display of 7 4'b1000 : seven_segment = 7'b0000000; //seven segment display of 8 4'b1001 : seven_segment = 7'b0010000; //seven segment display of 9 4'b1111 : seven_segment = 7'b0000000; //Doesn't Matter Not Going to Display default : seven_segment = 7'b1000000; //seven segment displaying 0 endcase end // //////////////////////////////////////////////////////////////////////////////// /////////////// ////////////////////////////Binary Number to ASCII/////////////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ///////////////// logic [7:0] ASCII_Number_thousands; logic [7:0] ASCII_Number_hundreds; logic [7:0] ASCII_Number_tens; logic [7:0] ASCII_Number_ones; // always_comb begin ASCII_Number_thousands = thousands_digit + 48; ASCII_Number_hundreds = hundreds_digit + 48; ASCII_Number_tens = tens_digit + 48; ASCII_Number_ones = ones_digit + 48; end /////////////////////////////////End of Binary to ASCII///////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////// ////////////////////////////////MUX: For Char Select/////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ///////// logic [7:0] char_mux_output; logic [3:0] char_mux_sel;](https://image.slidesharecdn.com/voltmentercode-160614052306/75/Digital-Voltmeter-displaying-voltage-level-on-a-seven-segment-display-and-computer-12-2048.jpg)

![logic [3:0] char_mux_sel_next; // always_ff@(posedge c2_sig or negedge reset) begin if (!reset) char_mux_sel <= 6; else char_mux_sel <= char_mux_sel_next; ///Incrementing the state end // always_comb begin if (char_mux_sel == 0) begin char_mux_output = ASCII_Number_thousands; // sel ASCII number Thousand if (bit_mux_sel_present==9) char_mux_sel_next = 1; else char_mux_sel_next = 0; end else if (char_mux_sel == 1) begin char_mux_output = 46; // sel decimel-point (.) if (bit_mux_sel_present==9) char_mux_sel_next = 2; else char_mux_sel_next = 1; end else if (char_mux_sel == 2) begin char_mux_output = ASCII_Number_hundreds; // sel ASCII number Hundred if (bit_mux_sel_present==9) char_mux_sel_next = 3; else char_mux_sel_next = 2; end else if (char_mux_sel == 3) begin char_mux_output = ASCII_Number_tens; // sel ASCII number Tens if (bit_mux_sel_present==9) char_mux_sel_next = 4; else char_mux_sel_next = 3; end else if (char_mux_sel == 4) begin char_mux_output = ASCII_Number_ones; // sel ASCII number ones if (bit_mux_sel_present==9) char_mux_sel_next = 5; else char_mux_sel_next = 4;](https://image.slidesharecdn.com/voltmentercode-160614052306/75/Digital-Voltmeter-displaying-voltage-level-on-a-seven-segment-display-and-computer-13-2048.jpg)

![end else if (char_mux_sel == 5) begin char_mux_output = 10; // sel Line Feed if (bit_mux_sel_present==9) char_mux_sel_next = 6; else char_mux_sel_next = 5; end else //if (char_mux_sel == 6) begin char_mux_output = 13; // sel Carrage return if (bit_mux_sel_present==9) char_mux_sel_next = 0; else char_mux_sel_next = 6; end end ///////////////////////////////End of Char MUX Select//////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////// ////////////////////////////////Bit Mux going to USB/////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ///////// logic [3:0] bit_mux_sel_present; logic [3:0] bit_mux_sel_next; // always_ff@(posedge c2_sig or negedge reset) begin if (!reset) bit_mux_sel_present <= 9; else bit_mux_sel_present <= bit_mux_sel_next; ///Incrementing the state end // always_comb begin unique case (bit_mux_sel_present) 0 : bit_mux_sel_next = 1; 1 : bit_mux_sel_next = 2; 2 : bit_mux_sel_next = 3; 3 : bit_mux_sel_next = 4; 4 : bit_mux_sel_next = 5;](https://image.slidesharecdn.com/voltmentercode-160614052306/75/Digital-Voltmeter-displaying-voltage-level-on-a-seven-segment-display-and-computer-14-2048.jpg)

![5 : bit_mux_sel_next = 6; 6 : bit_mux_sel_next = 7; 7 : bit_mux_sel_next = 8; 8 : bit_mux_sel_next = 9; 9 : bit_mux_sel_next = 0; //Circles Back endcase end // always_comb begin unique case (bit_mux_sel_present) 0 : PC_Serial_data_output = 0; 1 : PC_Serial_data_output = char_mux_output[0]; 2 : PC_Serial_data_output = char_mux_output[1]; 3 : PC_Serial_data_output = char_mux_output[2]; 4 : PC_Serial_data_output = char_mux_output[3]; 5 : PC_Serial_data_output = char_mux_output[4]; 6 : PC_Serial_data_output = char_mux_output[5]; 7 : PC_Serial_data_output = char_mux_output[6]; 8 : PC_Serial_data_output = char_mux_output[7]; 9 : PC_Serial_data_output = 1; endcase end ////////////////////////////////End of Bit Mux going to USB///////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////// ////////////////////////////////////////////RECEIVER//////////////////////////// /////////////////////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////// ////////////////////////////State Machine for Receiving Data From Laptop///////////////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////// typedef enum { Stopo, Starto } RECEIVER; RECEIVER present_state_receiver; RECEIVER next_state_receiver; logic [3:0] count_to_seven; logic save_this; //](https://image.slidesharecdn.com/voltmentercode-160614052306/75/Digital-Voltmeter-displaying-voltage-level-on-a-seven-segment-display-and-computer-15-2048.jpg)

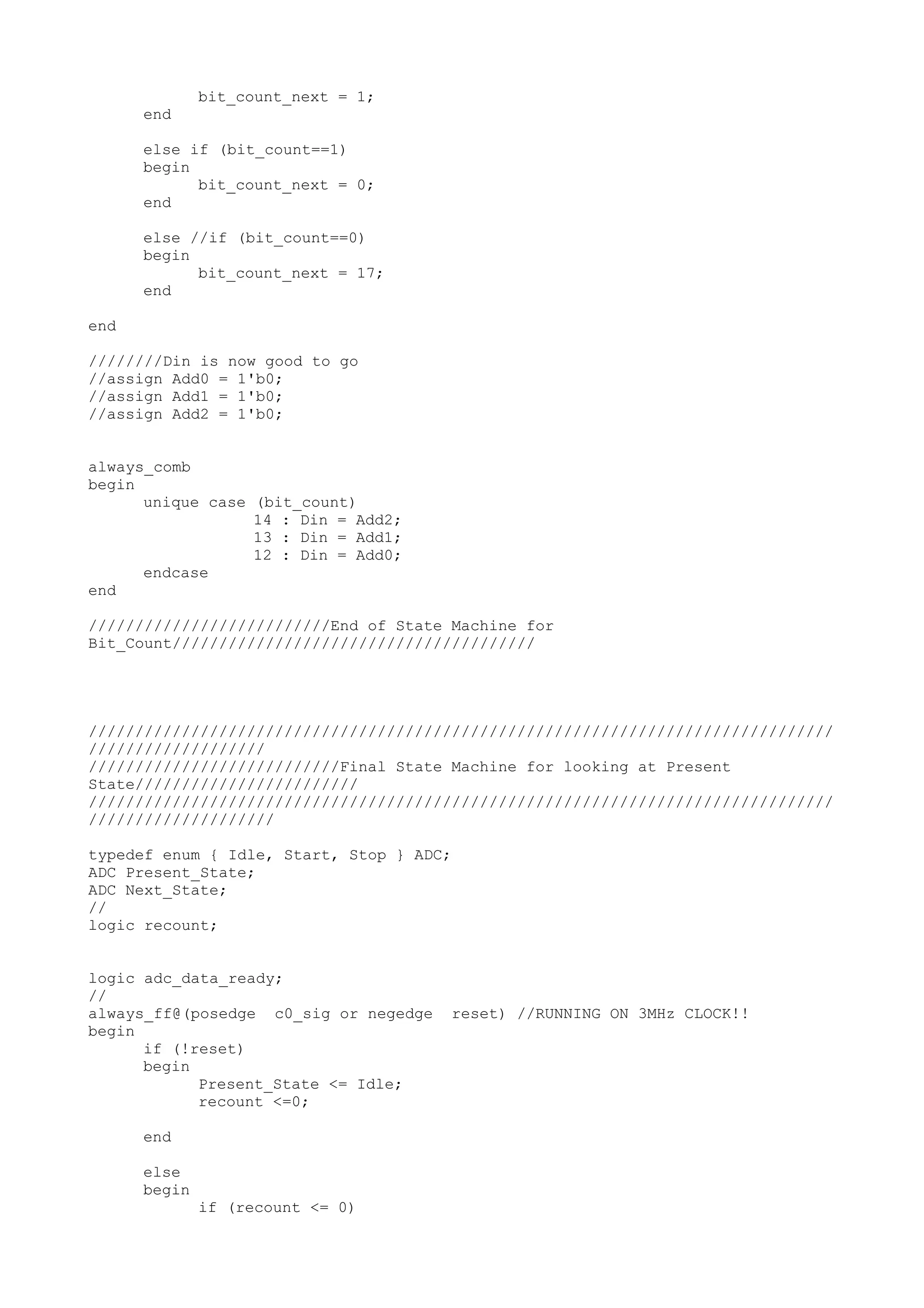

![stick to it next_state_receiver = Stopo; end end end ///////////////////////End of State Machine for Receiving Data From Laptop////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////// ////////////////////////////Shift Register for Collecting Data Received//////////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////// logic [7:0] ASCII_number_received; // always_ff@(posedge c2_sig or negedge reset) begin if (!reset) ASCII_number_received <= 0; else begin if (save_this == 1) begin if (count_to_seven < 7) begin if (count_to_seven == 0) begin ASCII_number_received[0] <= TXD; end else if (count_to_seven == 1) begin ASCII_number_received[1] <= TXD; end else if (count_to_seven == 2) begin ASCII_number_received[2] <= TXD; end else if (count_to_seven == 3) begin ASCII_number_received[3] <= TXD; end else if (count_to_seven == 4) begin ASCII_number_received[4] <= TXD; end else if (count_to_seven == 5) begin ASCII_number_received[5] <= TXD; end else if (count_to_seven == 6) begin](https://image.slidesharecdn.com/voltmentercode-160614052306/75/Digital-Voltmeter-displaying-voltage-level-on-a-seven-segment-display-and-computer-17-2048.jpg)

![ASCII_number_received[6] <= TXD; end else if (count_to_seven == 7) begin ASCII_number_received[7] <= TXD; end end else //count is 7 begin ASCII_number_received[0] <= ASCII_number_received[0]; ASCII_number_received[1] <= ASCII_number_received[1]; ASCII_number_received[2] <= ASCII_number_received[2]; ASCII_number_received[3] <= ASCII_number_received[3]; ASCII_number_received[4] <= ASCII_number_received[4]; ASCII_number_received[5] <= ASCII_number_received[5]; ASCII_number_received[6] <= ASCII_number_received[6]; ASCII_number_received[7] <= ASCII_number_received[7]; end end else //if (save_this == 0) DONT SAVE begin ASCII_number_received[0] <= ASCII_number_received[0]; ASCII_number_received[1] <= ASCII_number_received[1]; ASCII_number_received[2] <= ASCII_number_received[2]; ASCII_number_received[3] <= ASCII_number_received[3]; ASCII_number_received[4] <= ASCII_number_received[4]; ASCII_number_received[5] <= ASCII_number_received[5]; ASCII_number_received[6] <= ASCII_number_received[6]; ASCII_number_received[7] <= ASCII_number_received[7]; end end end /////////////////////////////////End of Shift Register for Collecting Data///////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////// //////////////////////////////////////////////////////////////////////////////// //////////////////////////////// //////////////////////////////////////////////Selecting Channel/////////////////////////////////////////////////// //////////////////////////////////////////////////////////////////////////////// ////////////////////////////// ////////////////////////LEDS On FPGA Indicating Which channel is selected//////////////////////////////////////////////////// always_comb begin case (ASCII_number_received) 48: LED_TEST = 1; 49: LED_TEST = 2; 50: LED_TEST = 4; 51: LED_TEST = 8;](https://image.slidesharecdn.com/voltmentercode-160614052306/75/Digital-Voltmeter-displaying-voltage-level-on-a-seven-segment-display-and-computer-18-2048.jpg)