Recommended introduction to embedded-converted new one

VON_NEUMANN_ARCHITECTURE_PPT_COAA final.pptx

digital principles and computer organization

Computer Architecture and Organization CAO

Computer Arithmetic and Processor Basics

Von-Neumann machine and IAS architecture

chapter 1 of computers organization .pdf

Chapter_3_Summary of my course pptx.pptx

CH01 - Computer Organization & Architecture - 10e_Stallings.pptx

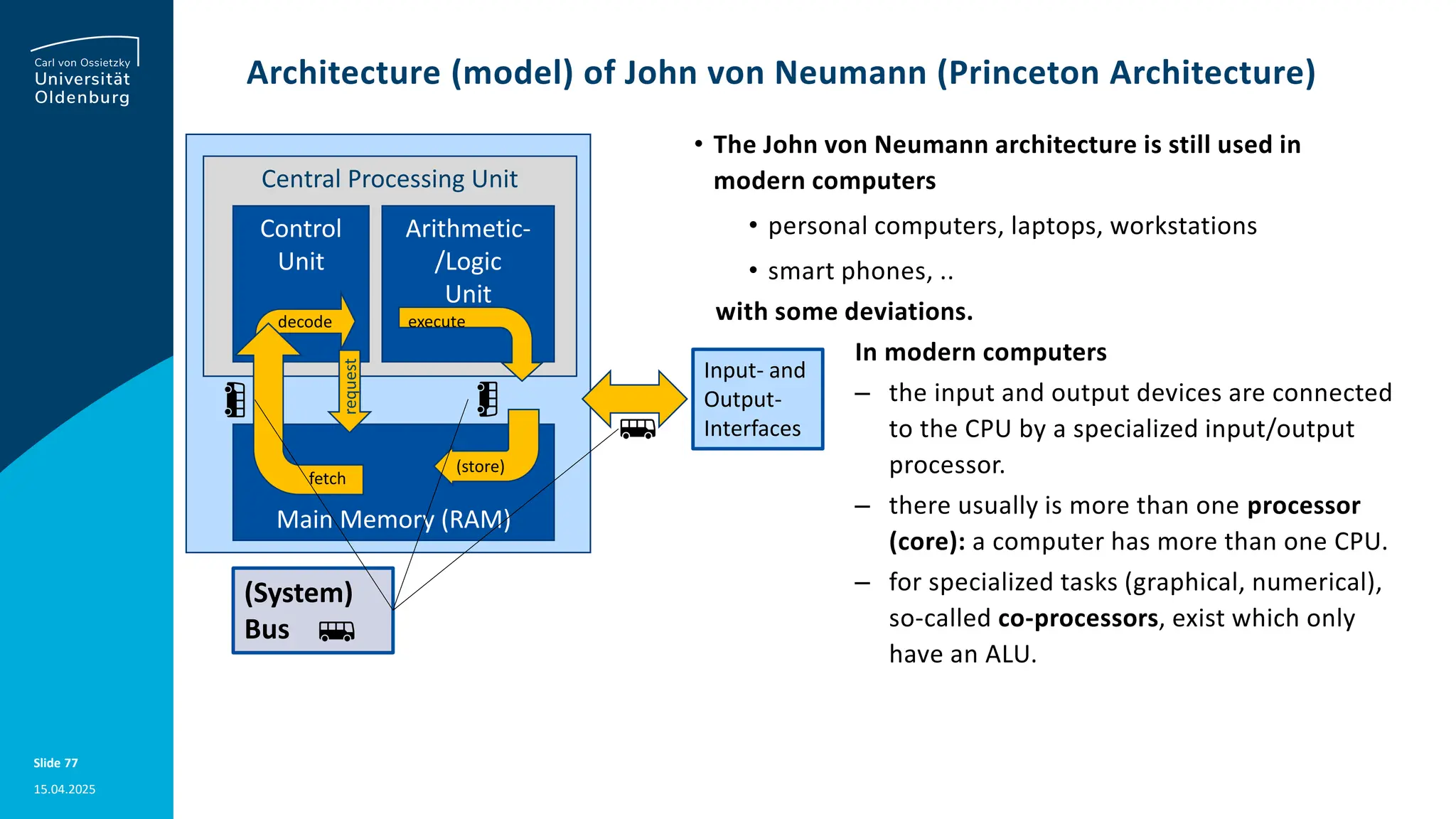

CMP 416-Architecture and system design.pdf

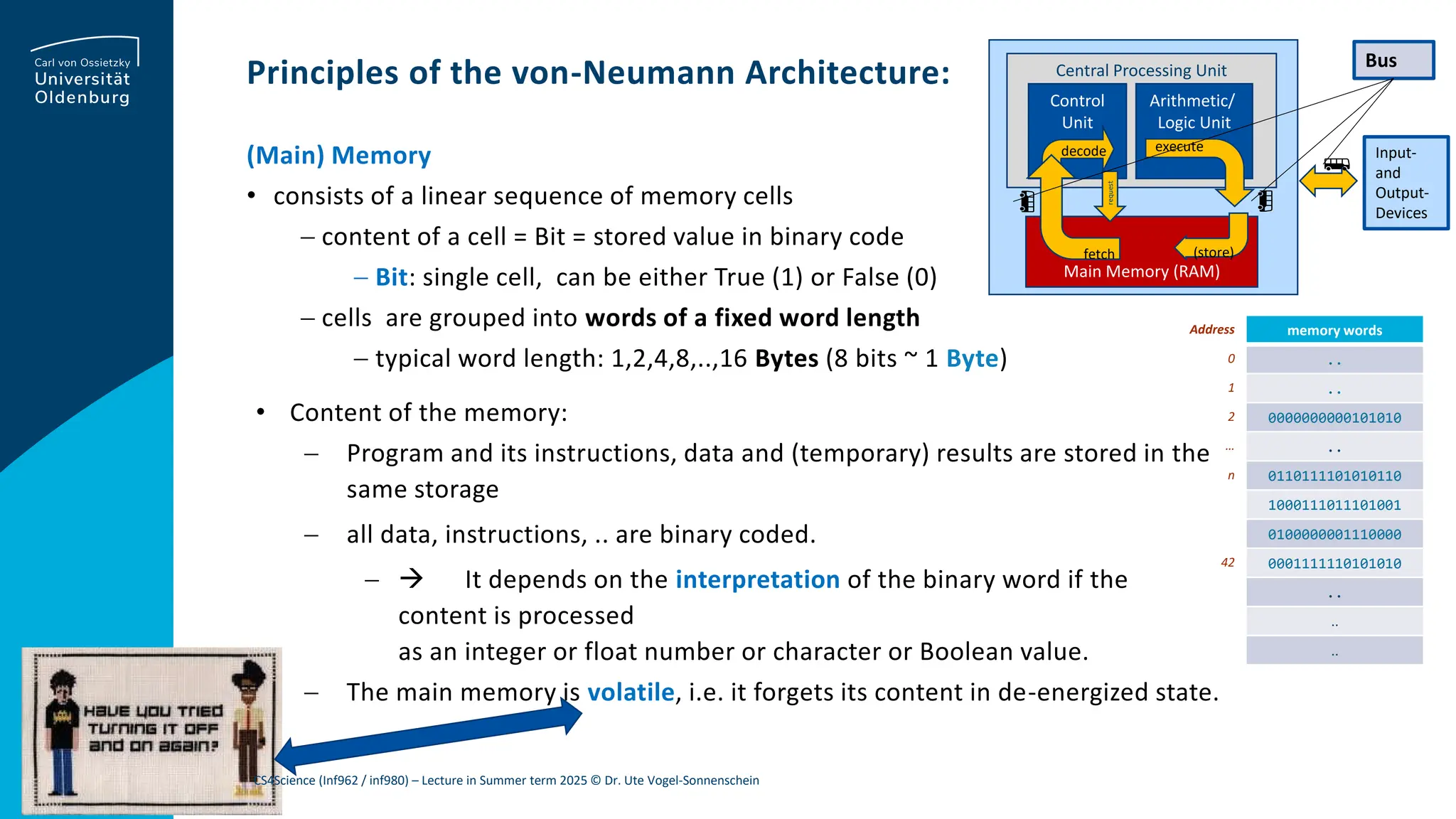

DSE LECTURE 1 -LRW_ Introduction_to_Computer.pptx

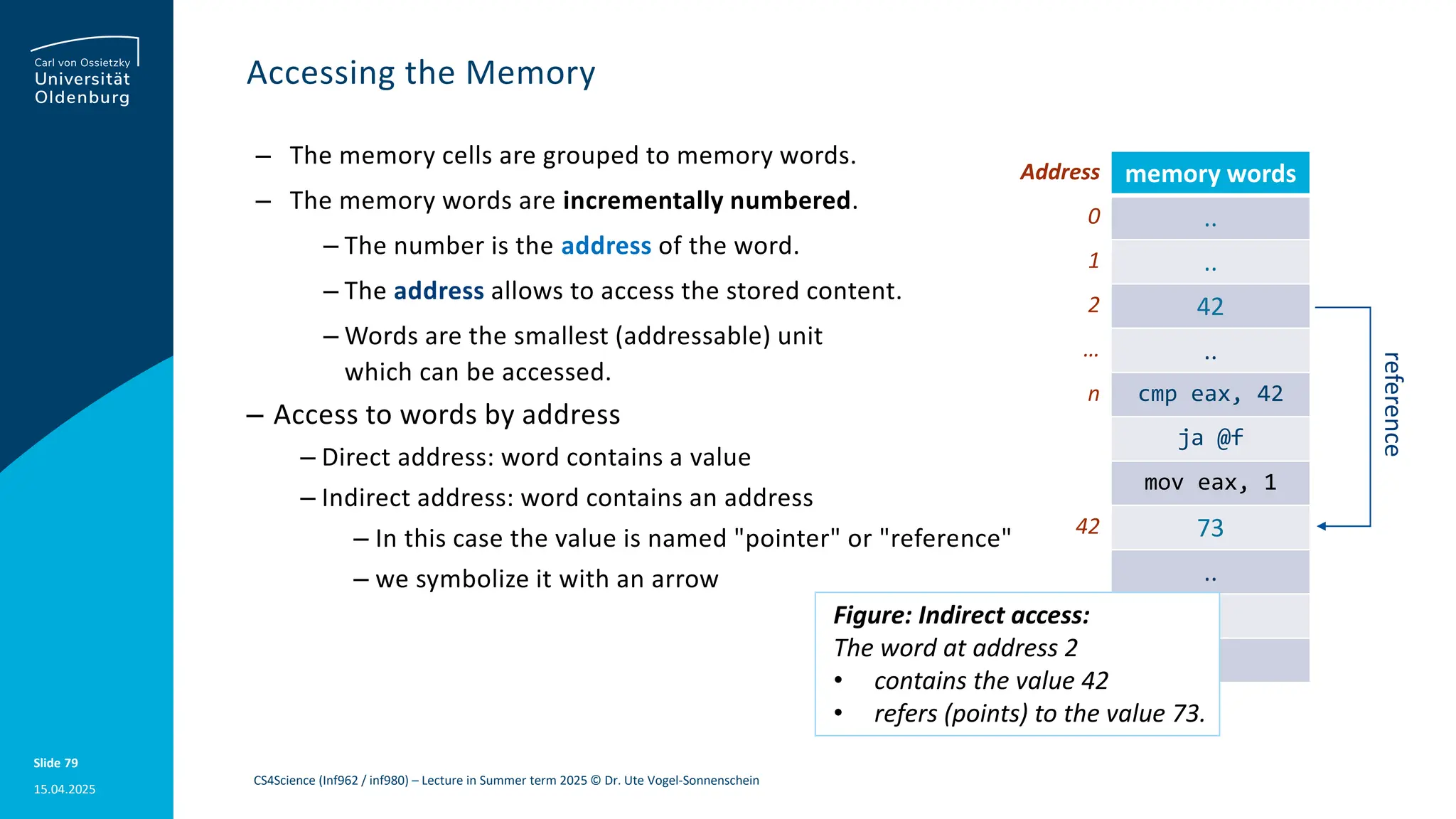

MI Unit-1.pdf a detailed presentation on microprocessors

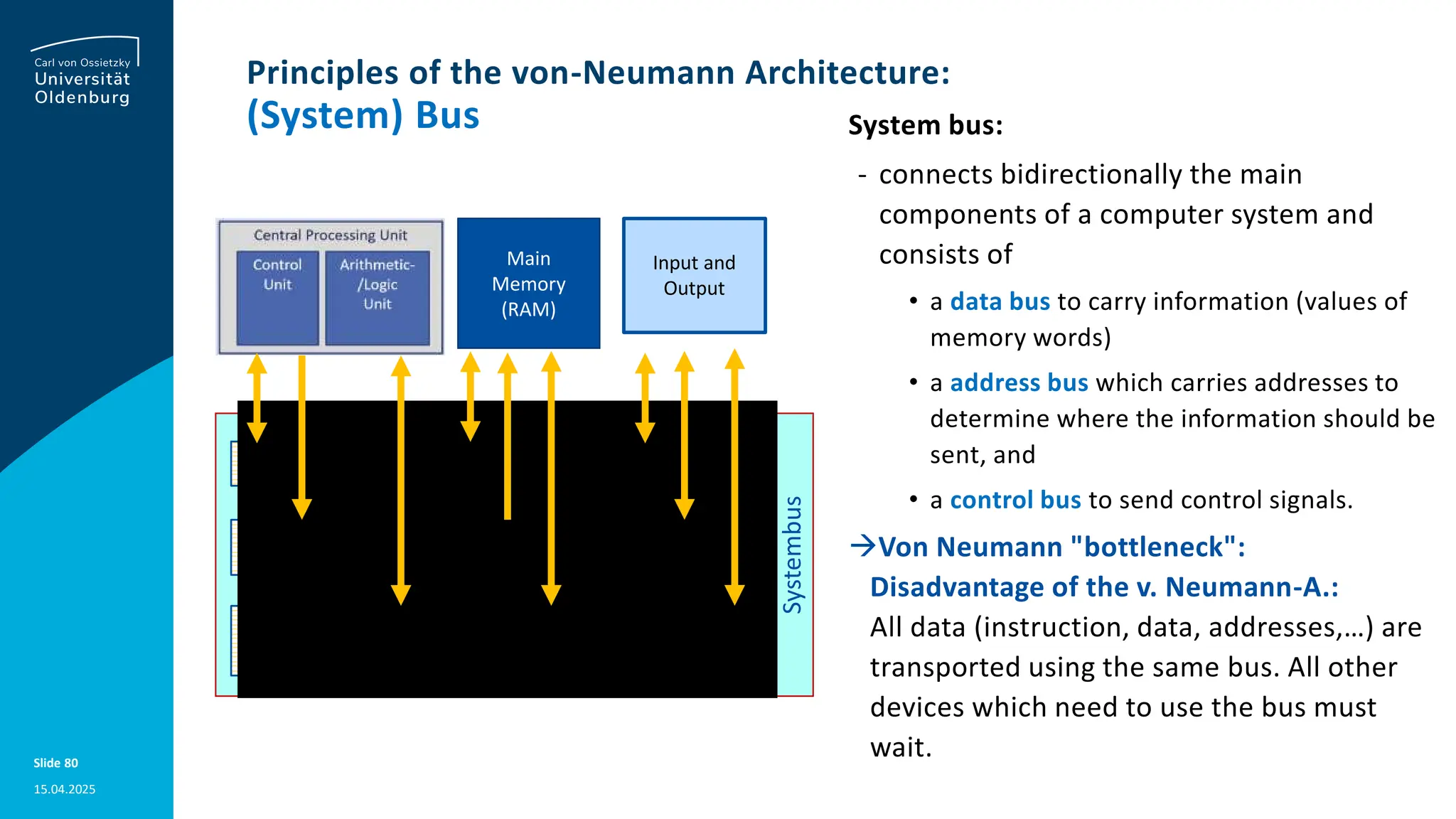

digital logic circuits, digital component

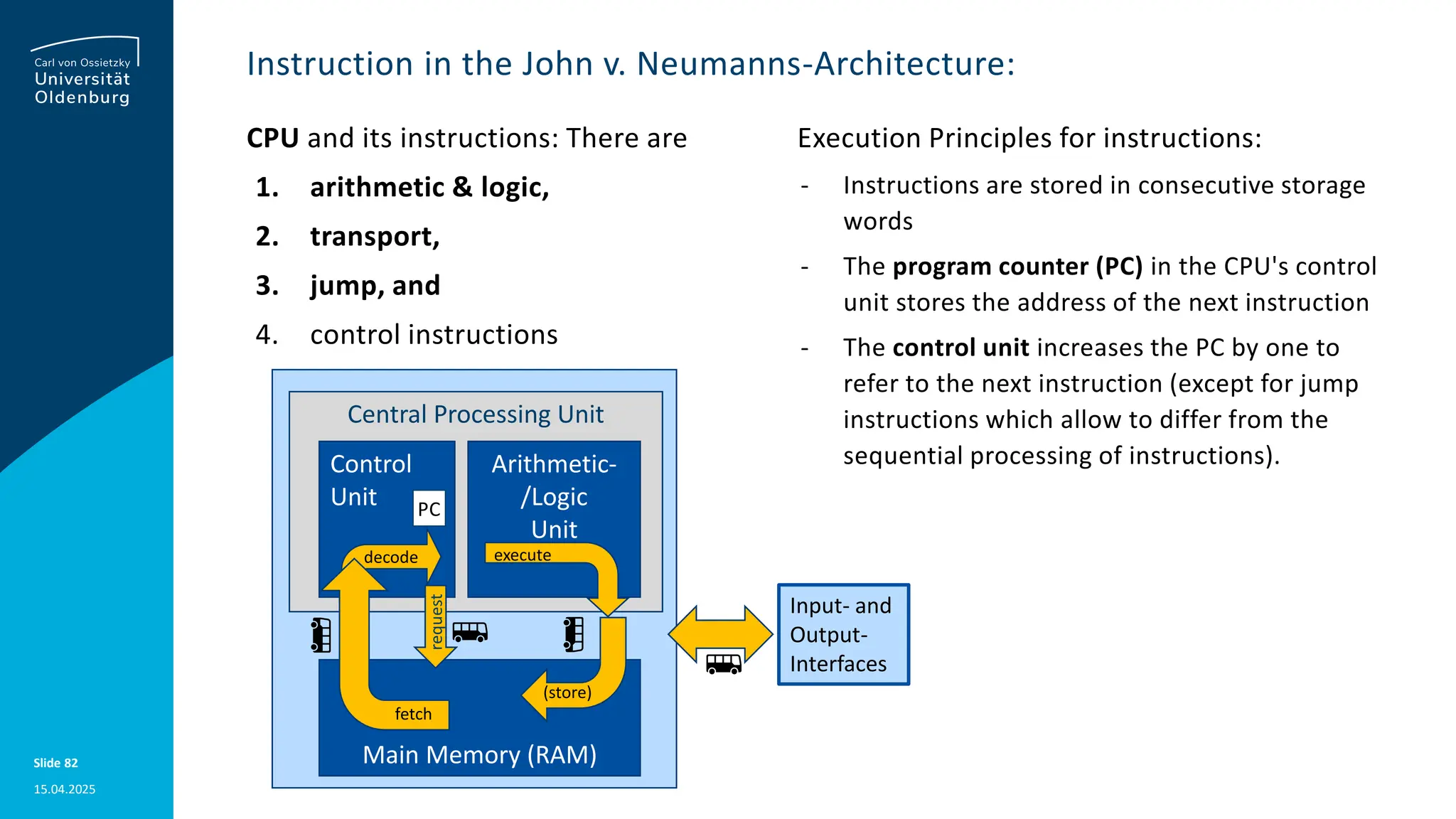

Bca 2nd sem-u-1.2 digital logic circuits, digital component

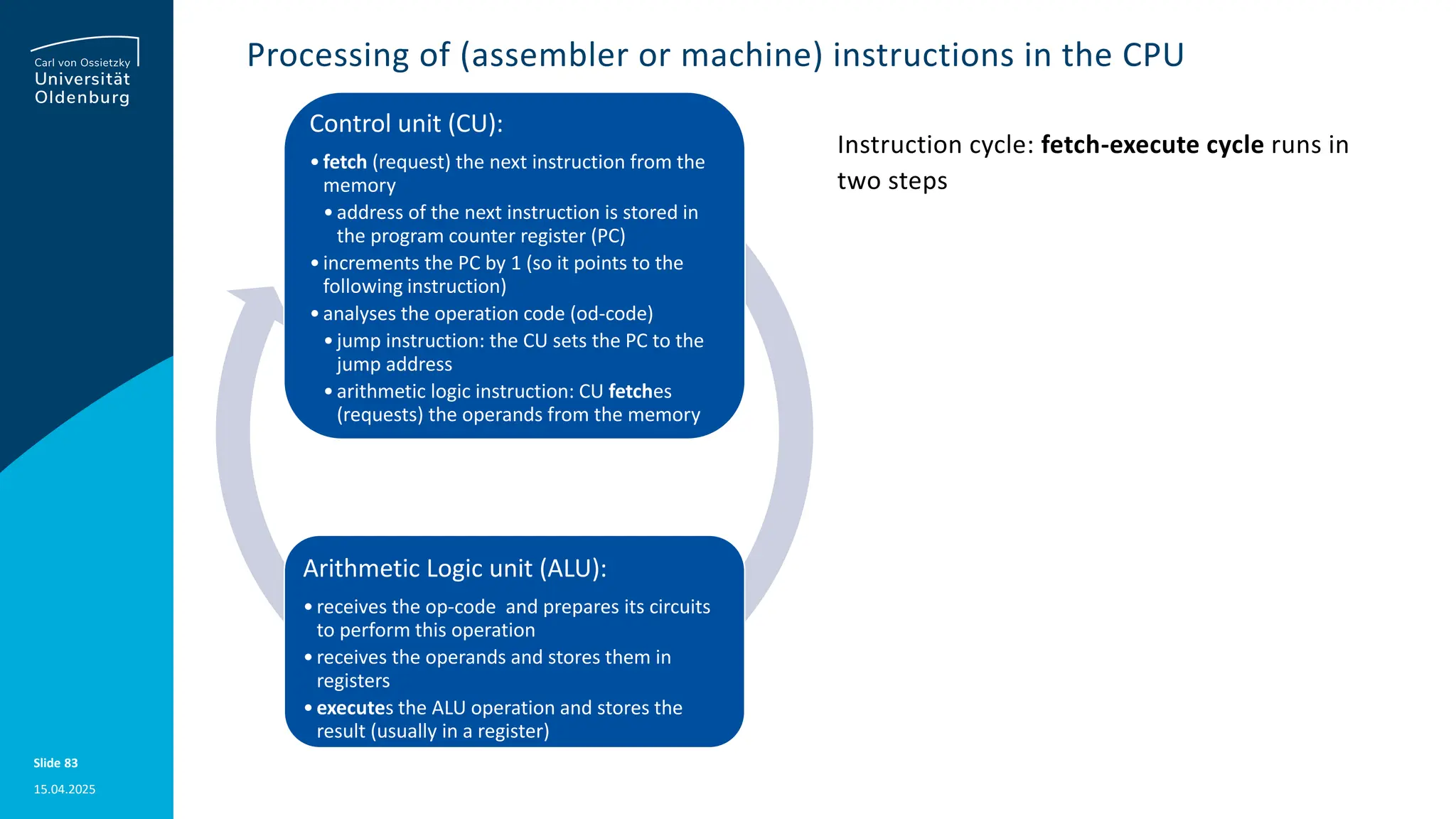

B.sc cs-ii -u-1.2 digital logic circuits, digital component

Microprocessor and Microcontroller Lecture.pptx

Computer organization basics

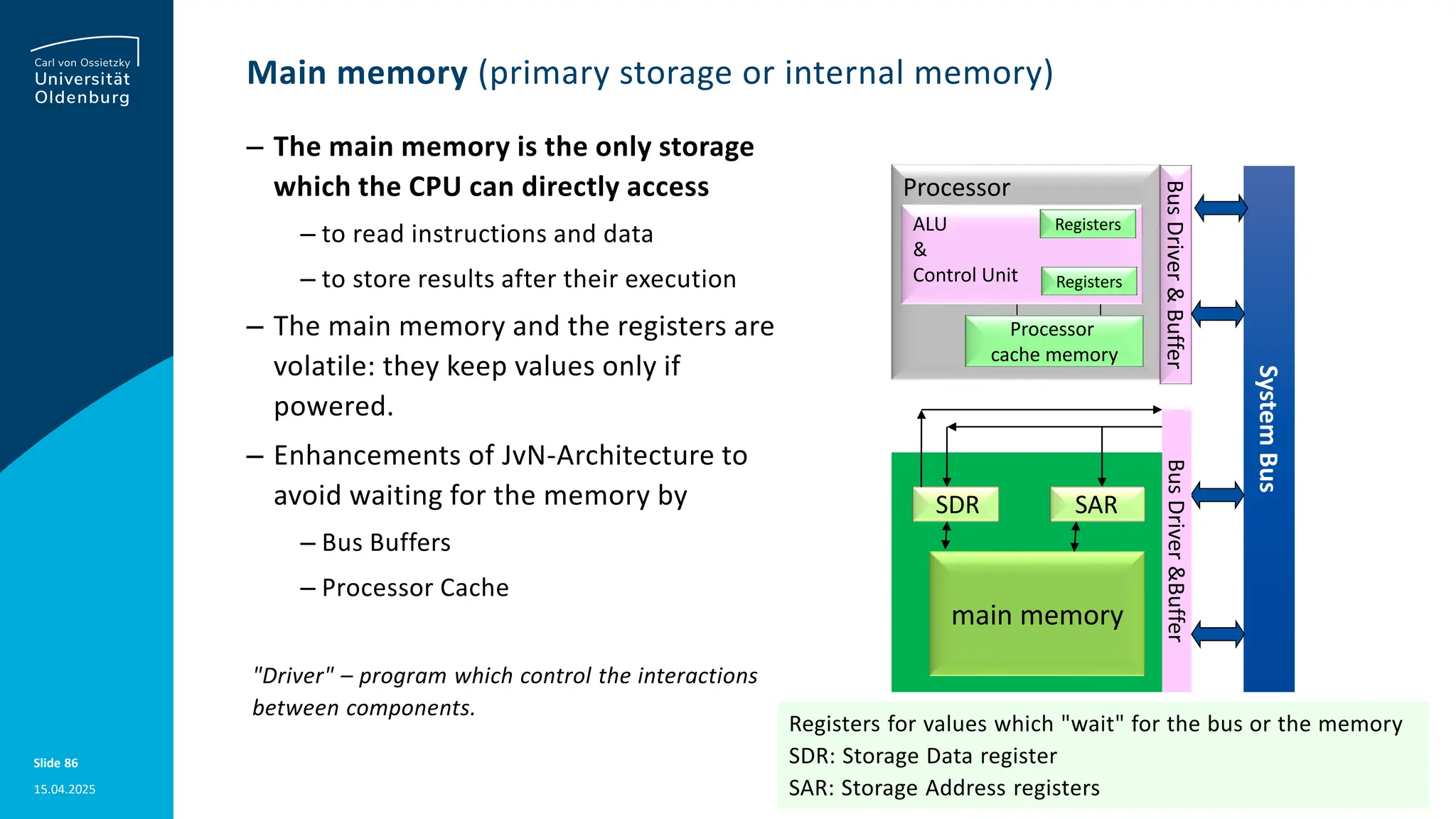

mohammad ghadery moghaddam treatment esra

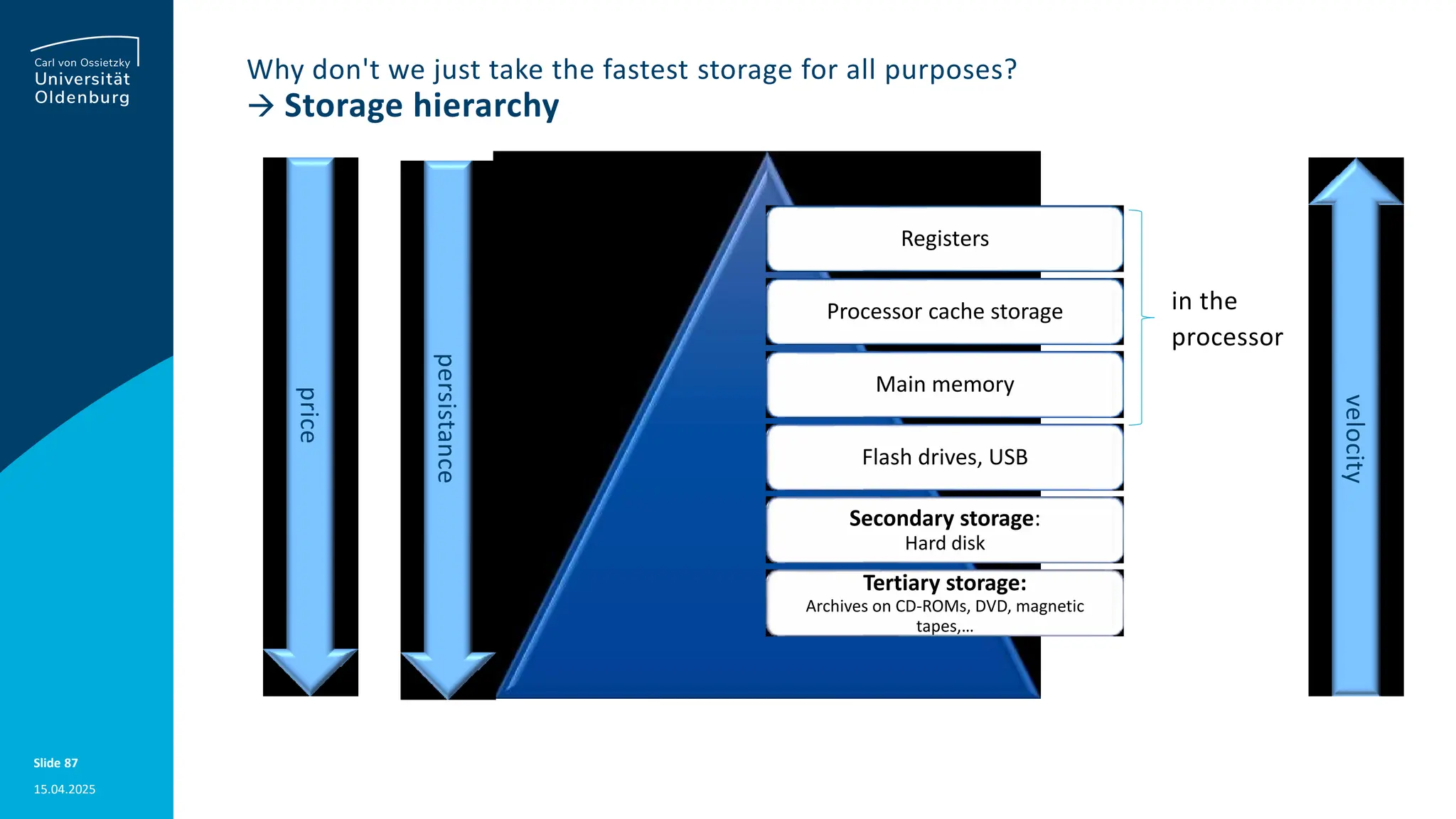

How To Buy Verified PayPal Accounts A Step By Step Guide.docx

More Related Content introduction to embedded-converted new one

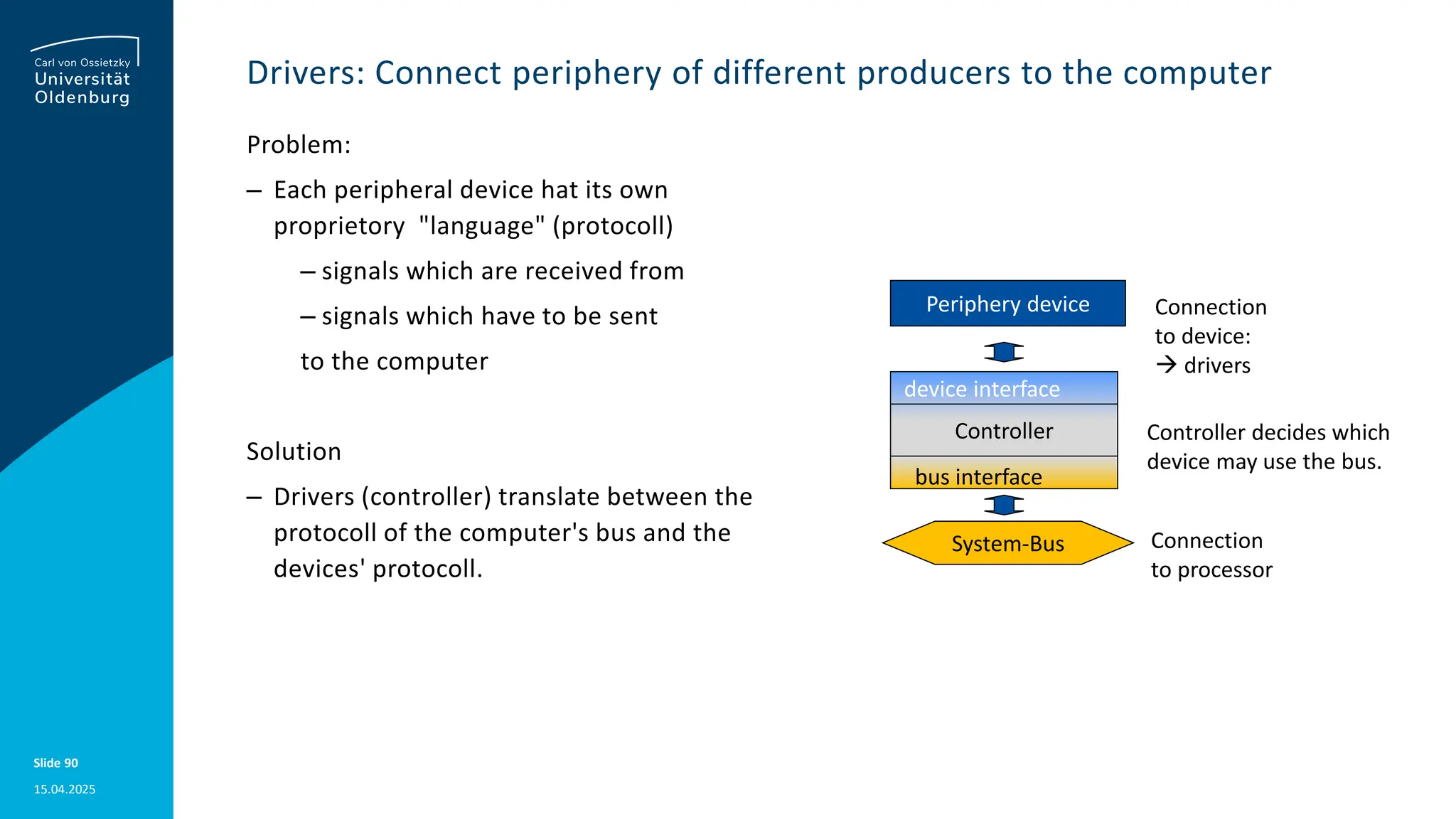

VON_NEUMANN_ARCHITECTURE_PPT_COAA final.pptx

digital principles and computer organization

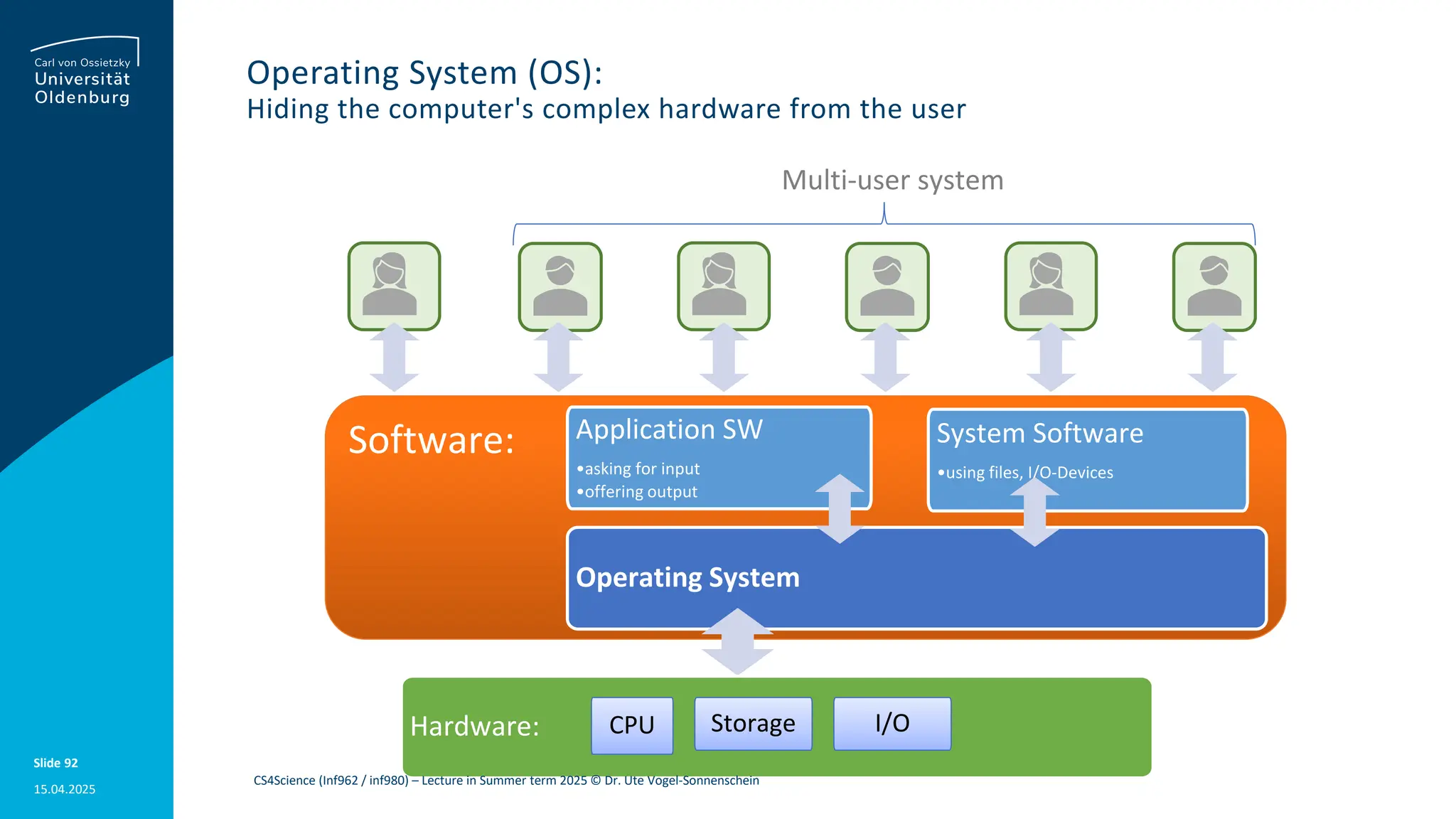

Computer Architecture and Organization CAO

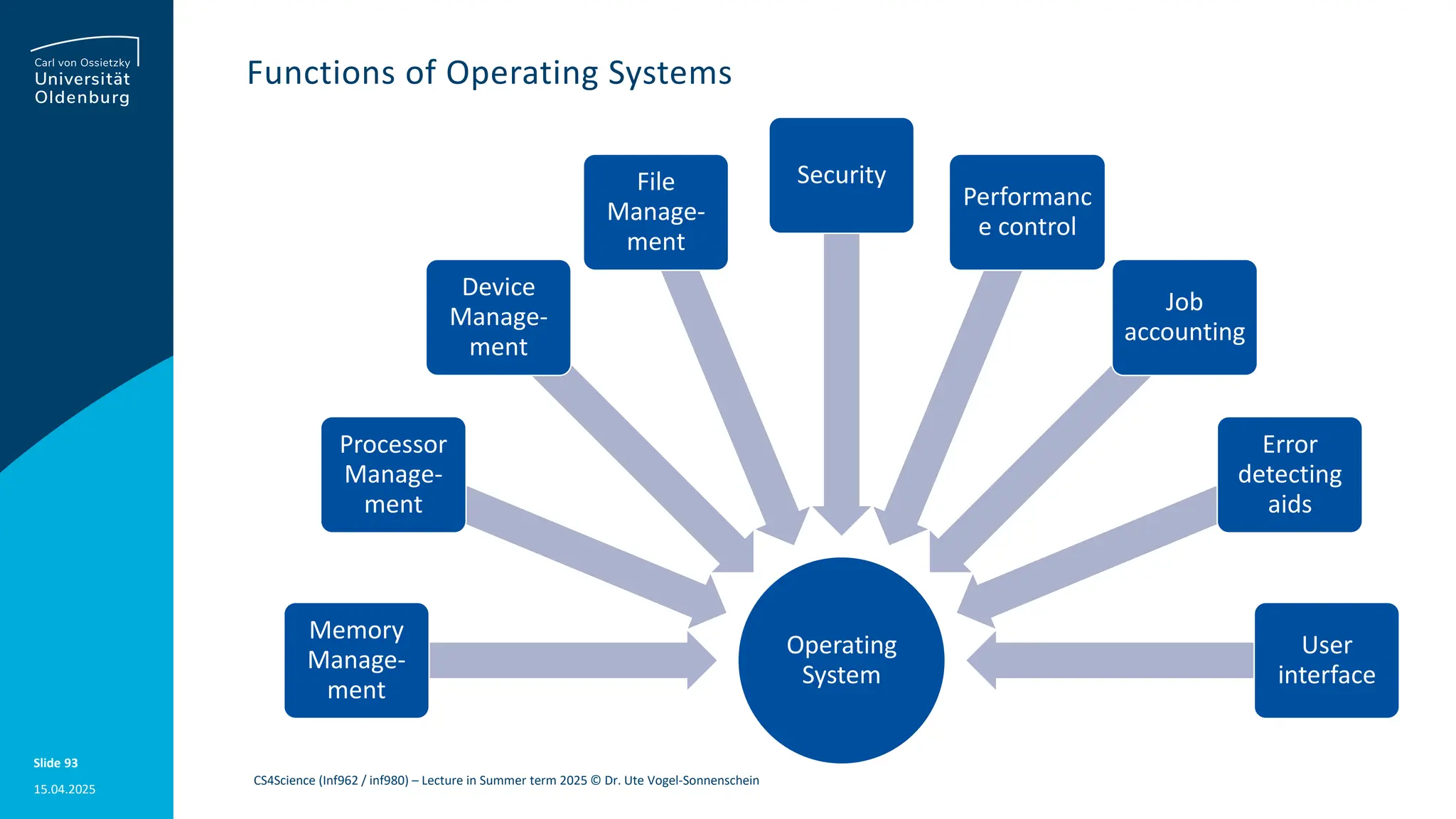

Computer Arithmetic and Processor Basics

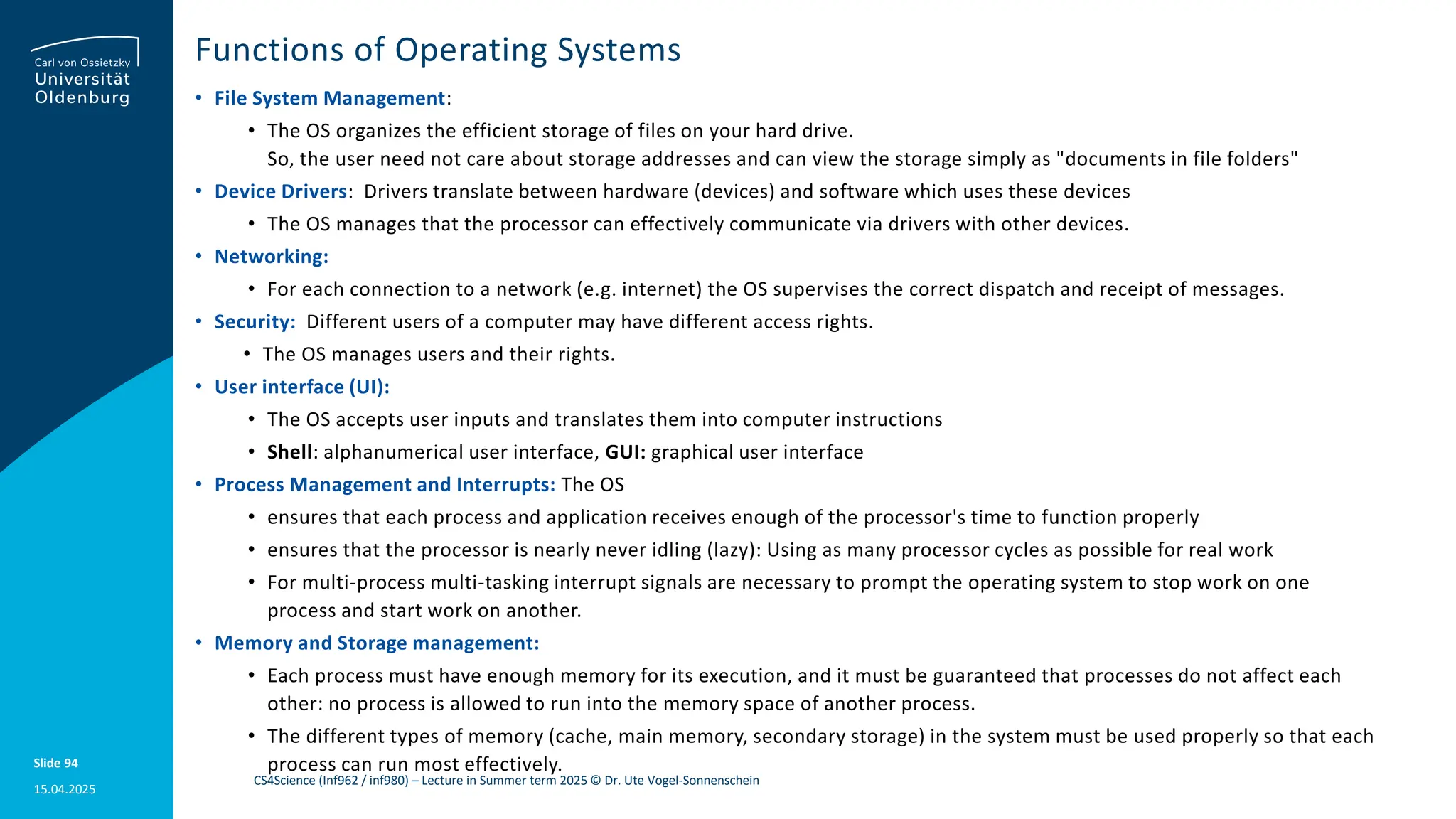

Von-Neumann machine and IAS architecture

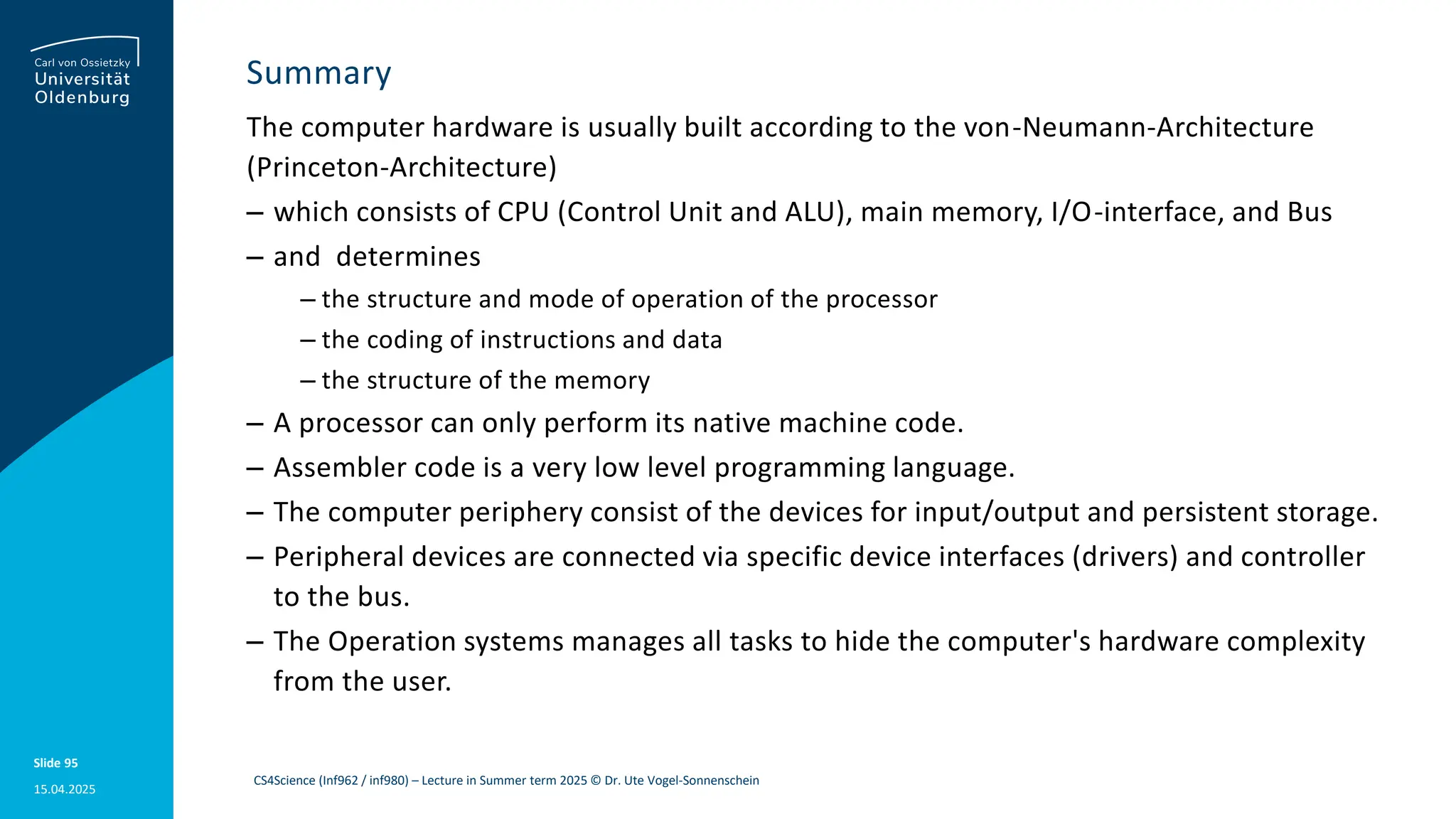

Similar to 2025_CS4Science_Part1-2a python data coding chapter 1 of computers organization .pdf

Chapter_3_Summary of my course pptx.pptx

CH01 - Computer Organization & Architecture - 10e_Stallings.pptx

CMP 416-Architecture and system design.pdf

DSE LECTURE 1 -LRW_ Introduction_to_Computer.pptx

MI Unit-1.pdf a detailed presentation on microprocessors

digital logic circuits, digital component

Bca 2nd sem-u-1.2 digital logic circuits, digital component

B.sc cs-ii -u-1.2 digital logic circuits, digital component

Microprocessor and Microcontroller Lecture.pptx

Computer organization basics

Recently uploaded mohammad ghadery moghaddam treatment esra

How To Buy Verified PayPal Accounts A Step By Step Guide.docx

SABRE BASIC AND ADVANCED TRAINING MANUAL BOOK BY MD SHAIFULLAR RABBI

IGNOU MMPC-007 BUSINESS COMMUNICATION.docx

Don_t_Waste_Your_Life_God.....powerpoint

Computer Network Architect Informational Powerpoint

Types of Leaders - Leadership Training Must Know

Good readers lead, when in a quiet spot i

Student Support and Guidance Programme (SSGP).pptx

Ppsc Chemistry Syllabus Guidance Book.pdf

How To Buy GOOGLE VOICE Accounts Safely In 2026-2027_.docx

The Making of an Architectural Portfolio

Everything You Need to Know About USA,UK Verified Payeer Accounts in 2025.docx

AI Took the Jobs – Now Professional Résumé Writers Are Bringing Them Back

Top 12 Sites To Buy Old Github Accounts In 2025

Paleozoic fauna Brachiopoda.pptx igneous

20251105 SIRS AI Talk - Artificial Intelligence.pptx

L21 internal and external diffusion.pptx

The Importance of Purchasing Verified Chime accounts for ....pdf

Top 9 Sites To Buy Verified Cash App Accounts in 2025 ....docx

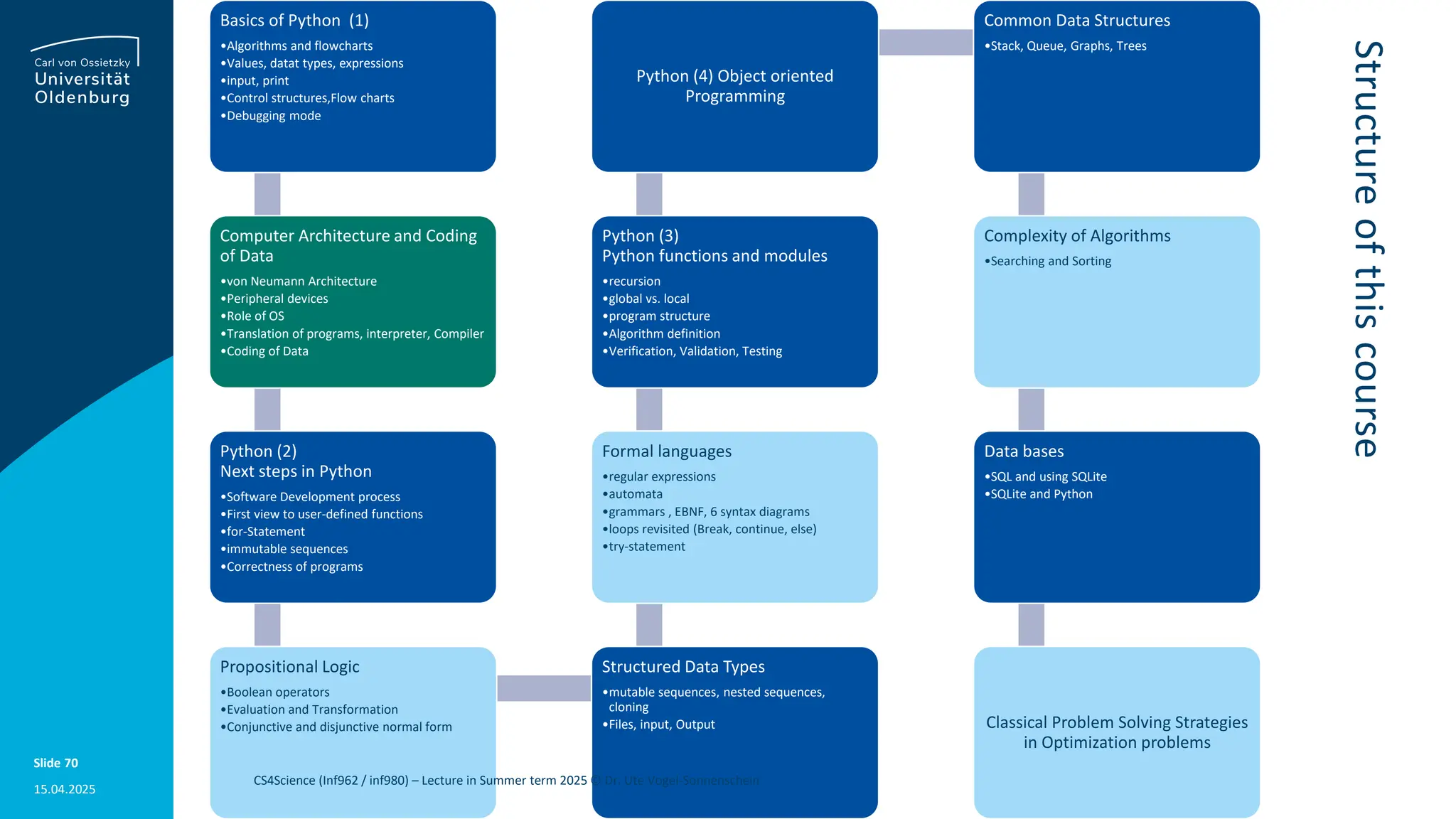

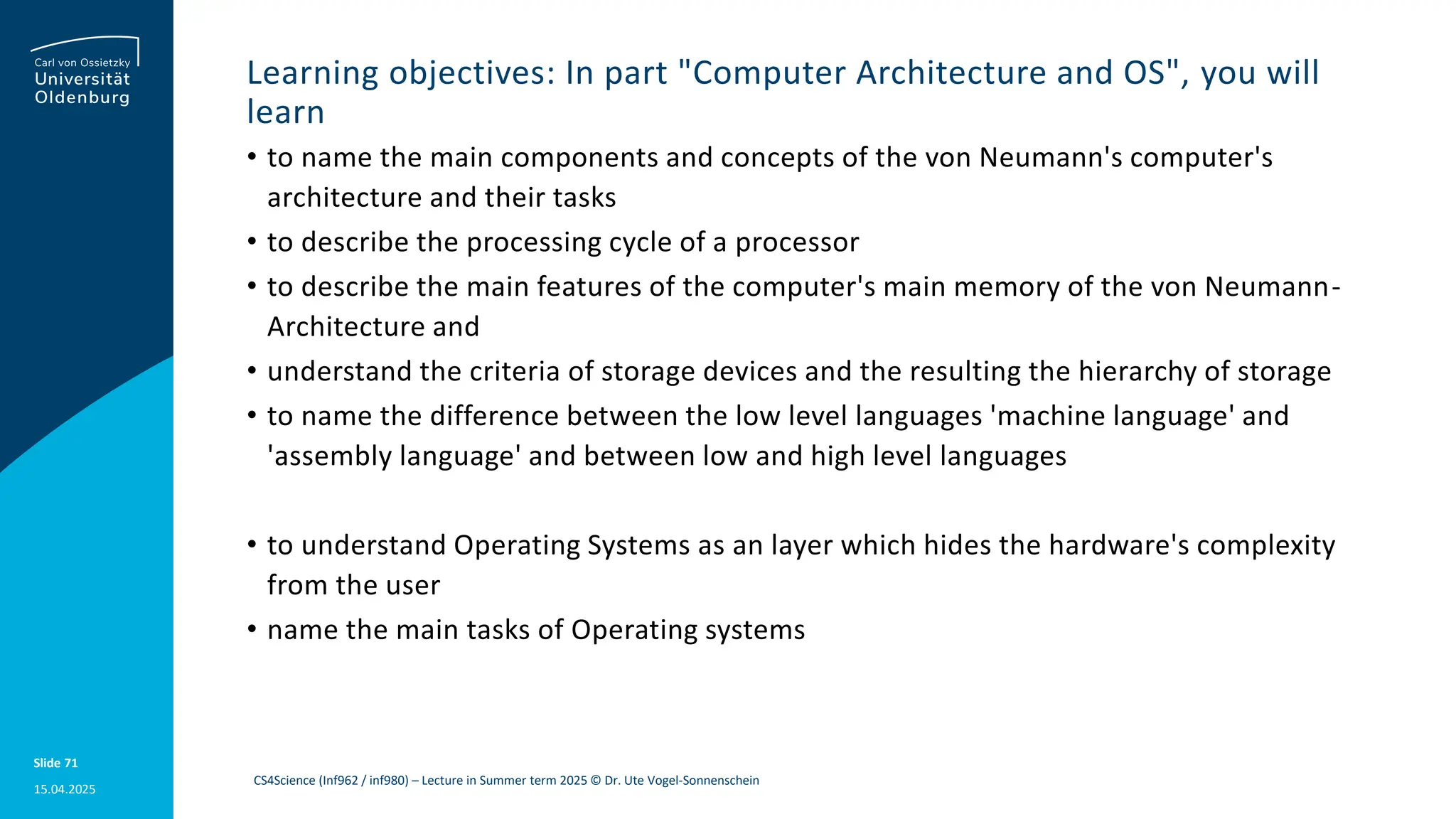

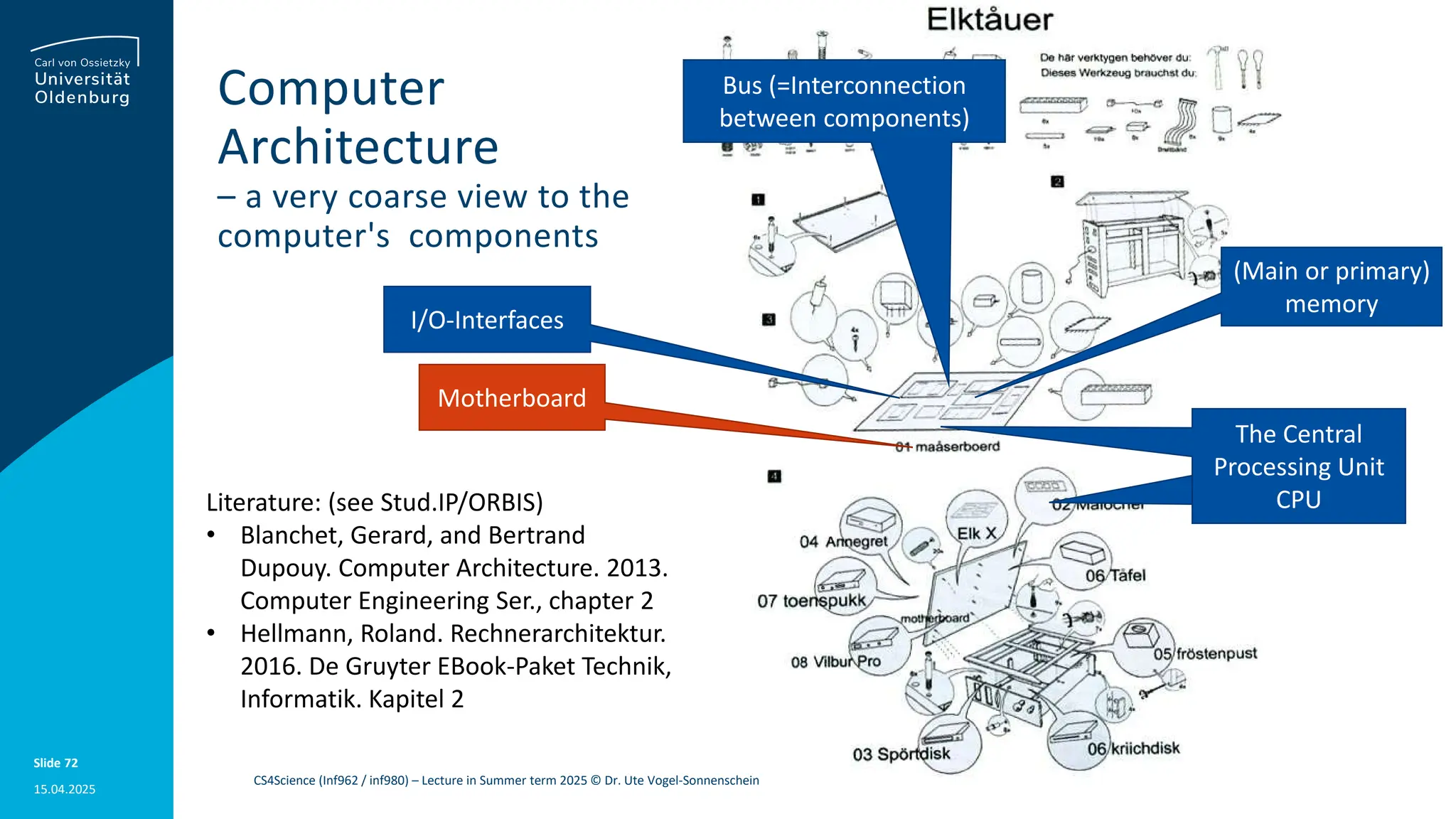

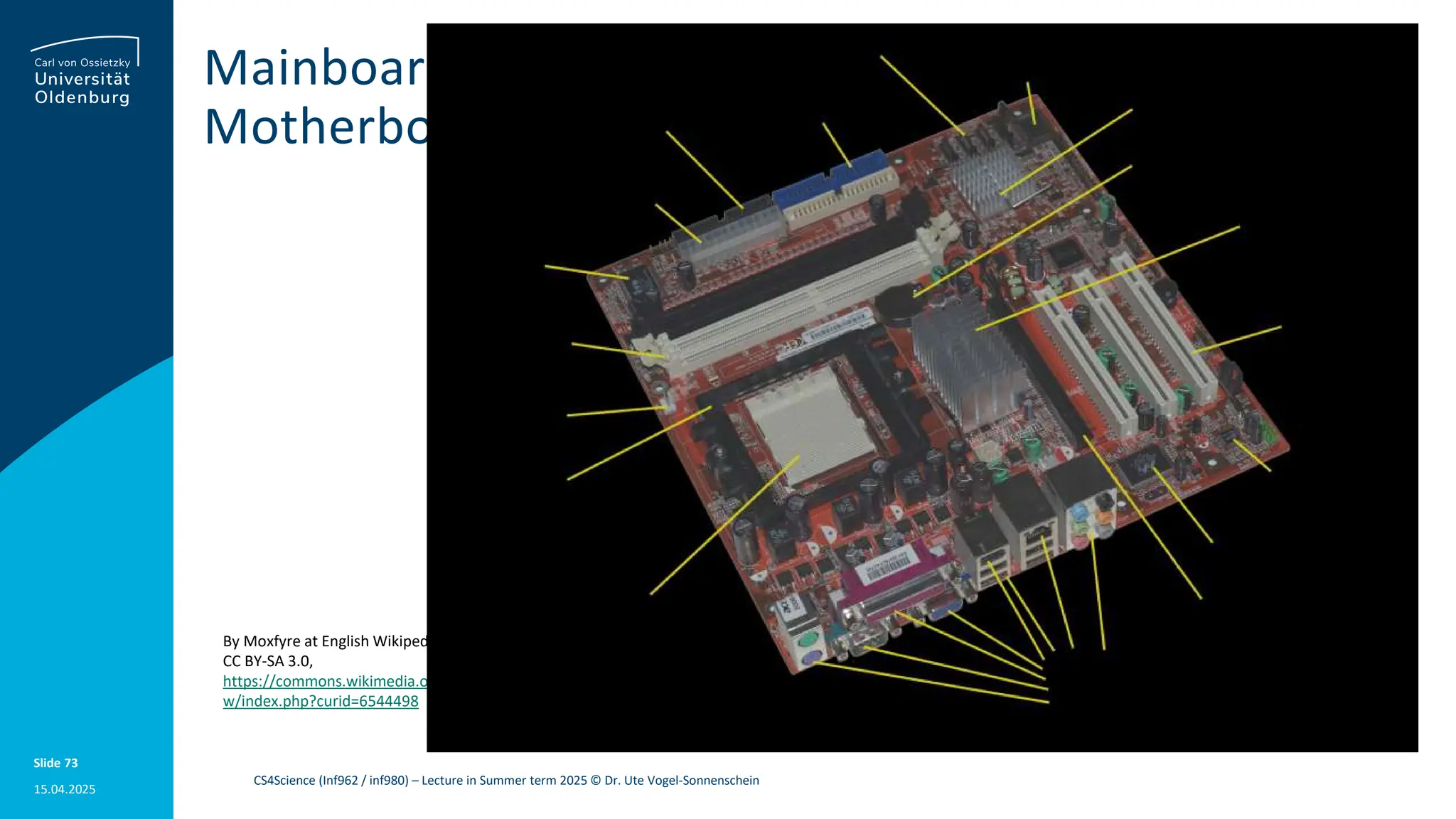

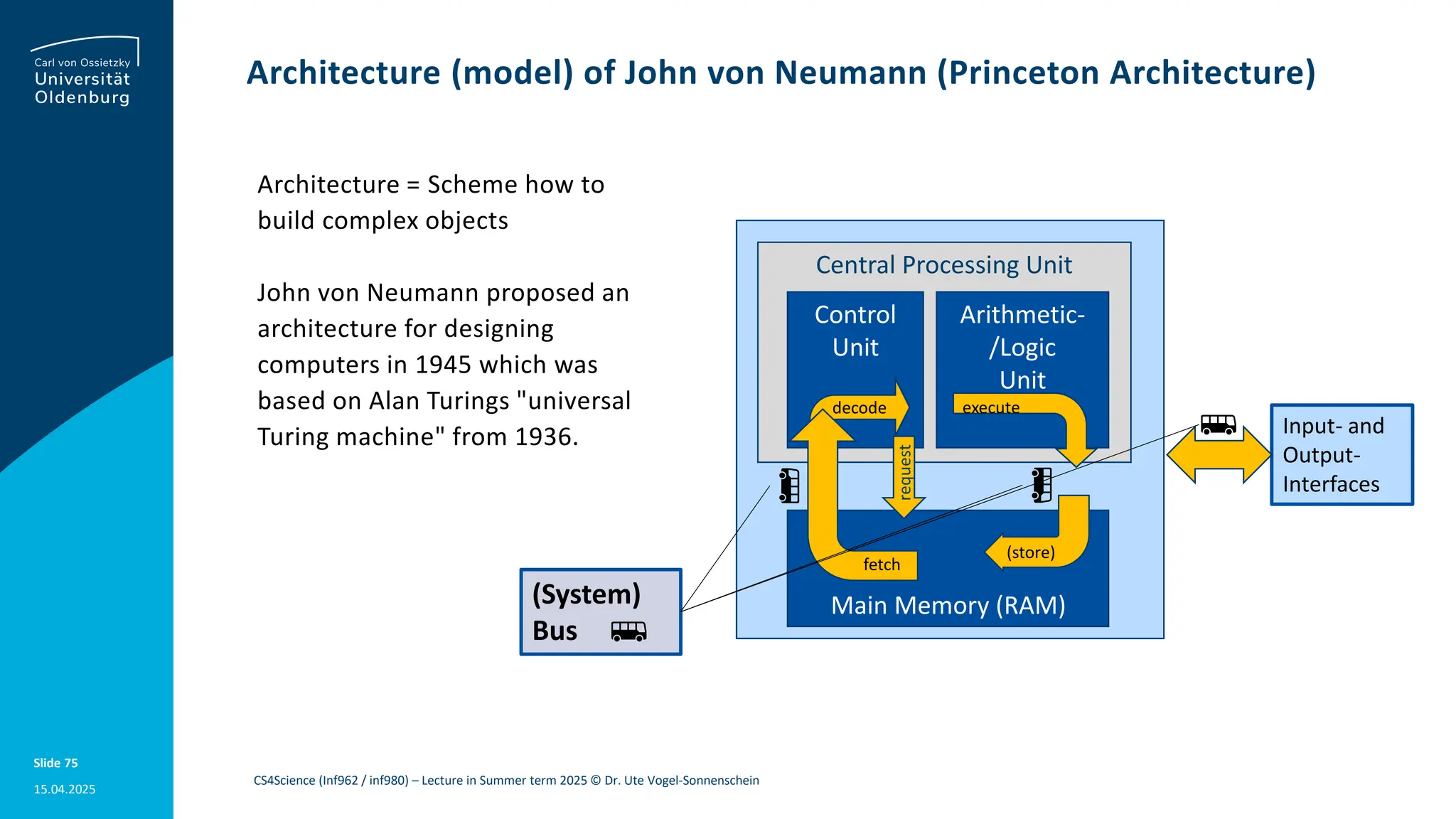

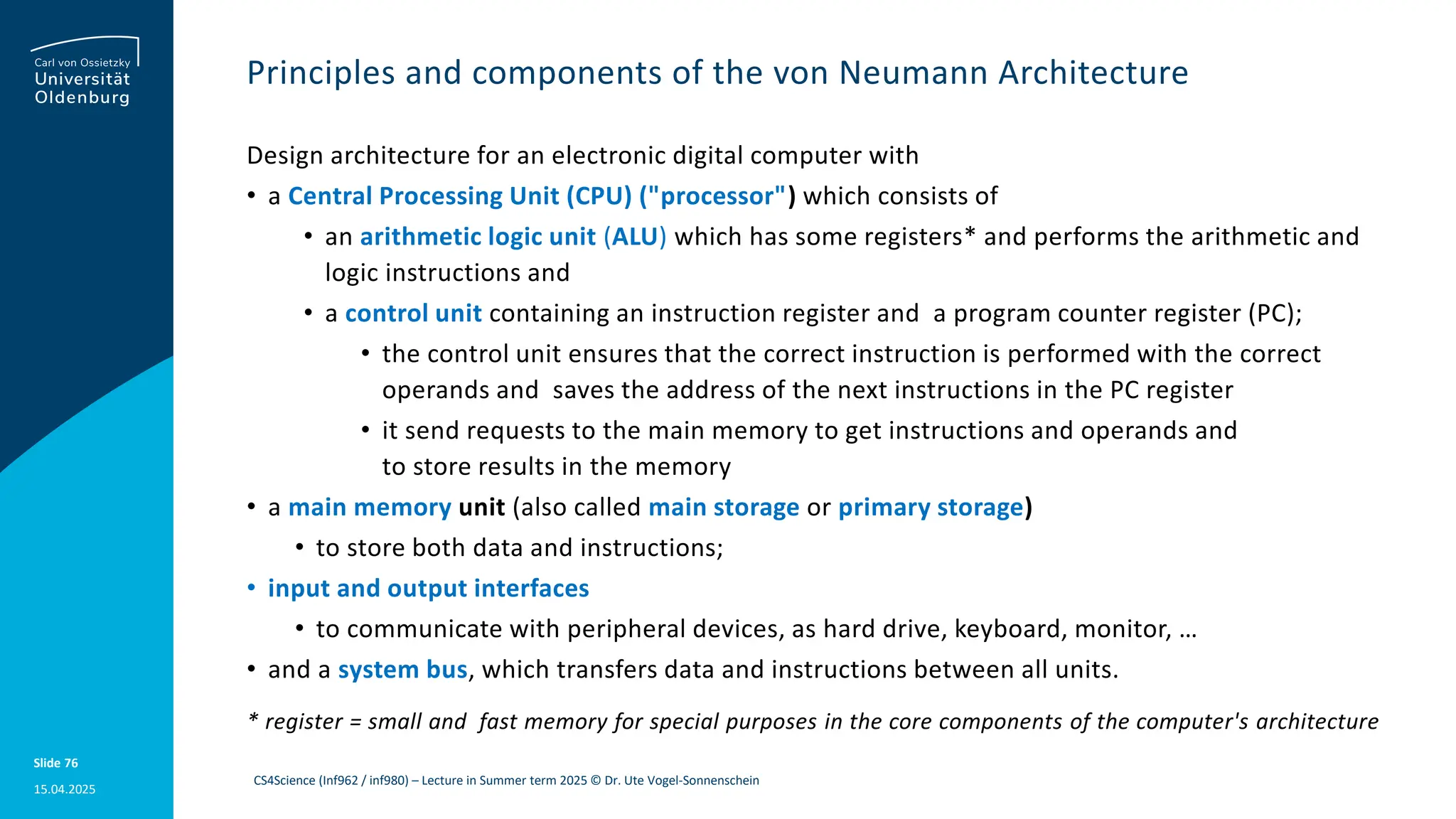

2025_CS4Science_Part1-2a python data coding 1. 2. 15.04.2025 Slide 70 Structure of this course Basics of Python (1) •Algorithms and flowcharts •Values, datat types, expressions •input, print •Control structures,Flow charts •Debugging mode Computer Architecture and Coding of Data •von Neumann Architecture •Peripheral devices •Role of OS •Translation of programs, interpreter, Compiler •Coding of Data Python (2) Next steps in Python •Software Development process •First view to user-defined functions •for-Statement •immutable sequences •Correctness of programs Propositional Logic •Boolean operators •Evaluation and Transformation •Conjunctive and disjunctive normal form Structured Data Types •mutable sequences, nested sequences, cloning •Files, input, Output Formal languages •regular expressions •automata •grammars , EBNF, 6 syntax diagrams •loops revisited (Break, continue, else) •try-statement Python (3) Python functions and modules •recursion •global vs. local •program structure •Algorithm definition •Verification, Validation, Testing Python (4) Object oriented Programming Common Data Structures •Stack, Queue, Graphs, Trees Complexity of Algorithms •Searching and Sorting Data bases •SQL and using SQLite •SQLite and Python Classical Problem Solving Strategies in Optimization problems CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein 3. 15.04.2025 Slide 71 Learning objectives: In part "Computer Architecture and OS", you will learn • to name the main components and concepts of the von Neumann's computer's architecture and their tasks • to describe the processing cycle of a processor • to describe the main features of the computer's main memory of the von Neumann- Architecture and • understand the criteria of storage devices and the resulting the hierarchy of storage • to name the difference between the low level languages 'machine language' and 'assembly language' and between low and high level languages • to understand Operating Systems as an layer which hides the hardware's complexity from the user • name the main tasks of Operating systems CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein 4. 15.04.2025 Slide 72 Computer Architecture – a very coarse view to the computer's components I/O-Interfaces (Main or primary) memory The Central Processing Unit The Central Processing Unit CPU Motherboard Bus (=Interconnection between components) Literature: (see Stud.IP/ORBIS) • Blanchet, Gerard, and Bertrand Dupouy. Computer Architecture. 2013. Computer Engineering Ser., chapter 2 • Hellmann, Roland. Rechnerarchitektur. 2016. De Gruyter EBook-Paket Technik, Informatik. Kapitel 2 CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein 5. 6. 7. 15.04.2025 Slide 75 Architecture (model) of John von Neumann (Princeton Architecture) Main Memory (RAM) Central Processing Unit Control Unit Arithmetic- /Logic Unit decode execute fetch (store) request Input- and Output- Interfaces (System) Bus Architecture = Scheme how to build complex objects John von Neumann proposed an architecture for designing computers in 1945 which was based on Alan Turings "universal Turing machine" from 1936. CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein 8. 15.04.2025 Slide 76 Principles and components of the von Neumann Architecture Design architecture for an electronic digital computer with • a Central Processing Unit (CPU) ("processor") which consists of • an arithmetic logic unit (ALU) which has some registers* and performs the arithmetic and logic instructions and • a control unit containing an instruction register and a program counter register (PC); • the control unit ensures that the correct instruction is performed with the correct operands and saves the address of the next instructions in the PC register • it send requests to the main memory to get instructions and operands and to store results in the memory • a main memory unit (also called main storage or primary storage) • to store both data and instructions; • input and output interfaces • to communicate with peripheral devices, as hard drive, keyboard, monitor, … • and a system bus, which transfers data and instructions between all units. * register = small and fast memory for special purposes in the core components of the computer's architecture CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein 9. 15.04.2025 Slide 77 Architecture (model) of John von Neumann (Princeton Architecture) • The John von Neumann architecture is still used in modern computers • personal computers, laptops, workstations • smart phones, .. with some deviations. In modern computers ‒ the input and output devices are connected to the CPU by a specialized input/output processor. ‒ there usually is more than one processor (core): a computer has more than one CPU. ‒ for specialized tasks (graphical, numerical), so-called co-processors, exist which only have an ALU. Main Memory (RAM) Central Processing Unit Control Unit Arithmetic- /Logic Unit decode execute fetch (store) request Input- and Output- Interfaces (System) Bus 10. 15.04.2025 Slide 78 Address memory words 0 .. 1 .. 2 0000000000101010 … .. n 0110111101010110 1000111011101001 0100000001110000 42 0001111110101010 .. .. .. Principles of the von-Neumann Architecture: (Main) Memory • consists of a linear sequence of memory cells − content of a cell = Bit = stored value in binary code − Bit: single cell, can be either True (1) or False (0) − cells are grouped into words of a fixed word length − typical word length: 1,2,4,8,..,16 Bytes (8 bits ~ 1 Byte) • Content of the memory: − Program and its instructions, data and (temporary) results are stored in the same storage − all data, instructions, .. are binary coded. − → It depends on the interpretation of the binary word if the content is processed as an integer or float number or character or Boolean value. − The main memory is volatile, i.e. it forgets its content in de-energized state. Main Memory (RAM) Central Processing Unit Control Unit Arithmetic/ Logic Unit decode execute fetch (store) request Input- and Output- Devices Bus CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein 11. 15.04.2025 Slide 79 Accessing the Memory ‒ The memory cells are grouped to memory words. ‒ The memory words are incrementally numbered. ‒ The number is the address of the word. ‒ The address allows to access the stored content. ‒ Words are the smallest (addressable) unit which can be accessed. ‒ Access to words by address ‒ Direct address: word contains a value ‒ Indirect address: word contains an address ‒ In this case the value is named "pointer" or "reference" ‒ we symbolize it with an arrow Address memory words 0 .. 1 .. 2 42 … .. n cmp eax, 42 ja @f mov eax, 1 42 73 .. .. .. reference Figure: Indirect access: The word at address 2 • contains the value 42 • refers (points) to the value 73. CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein 12. 15.04.2025 Slide 80 Systembus Principles of the von-Neumann Architecture: (System) Bus System bus: - connects bidirectionally the main components of a computer system and consists of • a data bus to carry information (values of memory words) • a address bus which carries addresses to determine where the information should be sent, and • a control bus to send control signals. →Von Neumann "bottleneck": Disadvantage of the v. Neumann-A.: All data (instruction, data, addresses,…) are transported using the same bus. All other devices which need to use the bus must wait. Input and Output Main Memory (RAM) Address bus Data bus Control bus 13. 15.04.2025 Slide 82 Instruction in the John v. Neumanns-Architecture: CPU and its instructions: There are 1. arithmetic & logic, 2. transport, 3. jump, and 4. control instructions Execution Principles for instructions: - Instructions are stored in consecutive storage words - The program counter (PC) in the CPU's control unit stores the address of the next instruction - The control unit increases the PC by one to refer to the next instruction (except for jump instructions which allow to differ from the sequential processing of instructions). Main Memory (RAM) Central Processing Unit Control Unit Arithmetic- /Logic Unit decode execute fetch (store) request Input- and Output- Interfaces PC 14. 15.04.2025 Slide 83 Processing of (assembler or machine) instructions in the CPU Control unit (CU): •fetch (request) the next instruction from the memory •address of the next instruction is stored in the program counter register (PC) •increments the PC by 1 (so it points to the following instruction) •analyses the operation code (od-code) •jump instruction: the CU sets the PC to the jump address •arithmetic logic instruction: CU fetches (requests) the operands from the memory Arithmetic Logic unit (ALU): •receives the op-code and prepares its circuits to perform this operation •receives the operands and stores them in registers •executes the ALU operation and stores the result (usually in a register) Instruction cycle: fetch-execute cycle runs in two steps 15. 15.04.2025 Slide 84 Low Level Languages: Machine L. and assembly L. Low Level Languages: ‒ easy to execute by the computer's processor ‒ but difficult to understand by humans ‒ Machine language ‒ is specific to the type of processor ‒ instructions can be directly executed by the machine's processor ‒ instructions are represented in binary code ‒ there are jump, arithmetic & logic (ALU), or transfer operations which move data in a CPU register or in memory. ‒ Assembly language ‒ "symbolic" machine code: one-to-one-translation of machine code into more readable words 8B54240883FA007 706B800000000C3 83FA027706B8010 00000C353BB0100 0000B9010000008 D041983FA037607 8BD989C14AEBF15 BC3 8B54240883FA007 706B800000000C3 83FA027706B8010 00000C353BB0100 0000B9010000008 D041983FA037607 8BD989C14AEBF15 BC3 fib: mov edx, [esp+8] cmp edx, 0 ja @f mov eax, 0 ret @@: cmp edx, 2 ja @f mov eax, 1 ret @@: push ebx mov ebx, 1 mov ecx, 1 @@: lea eax, [ebx+ecx] cmp edx, 3 jbe @f mov ebx, ecx mov ecx, eax dec edx jmp @b @@: pop ebx ret fib: mov edx, [esp+8] cmp edx, 0 ja @f mov eax, 0 ret @@: cmp edx, 2 ja @f mov eax, 1 ret @@: push ebx mov ebx, 1 mov ecx, 1 @@: lea eax, [ebx+ecx] cmp edx, 3 jbe @f mov ebx, ecx mov ecx, eax dec edx jmp @b @@: pop ebx ret 32-bit x86 machine and MAMS-assembly code Quelle: https://en.wikipedia.org/wiki/Low-level_programming_language#Low- level_programming_in_high-level_languages Program in hexadecimal machine code CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein 16. 15.04.2025 Slide 85 Examples of assembly instructions MAMS-assembly code: Two-address code ‒ Structure of a machine instruction (here: two address code) <operation code> <operand1> <operand2> mov eax, 0 ‒ Put the value 0 into register eax → Transport instruction ‒ A register is a small but very fast memory word for storing temporary values lea eax, [ebx+ecx] → Arithmetic instruction ‒ add the value which is stored at address ebx +ecx to the value in register eax dec edx → Arithmetic instruction ‒ subtract 1 from the value in register edx cmp edx, 3 → Arithmetic/Logic instruction ‒ Compare the value in register edx with 3. If equal, a flag will be set to inform the next instruction jbe @f → Jump instruction ‒ jbe means "jump if equal" (i.e. if the flag is set) ‒ @f is a symbol for the next (unnamed) label @@ fib: mov edx, [esp+8] cmp edx, 0 ja @f mov eax, 0 ret @@: cmp edx, 2 ja @f mov eax, 1 ret @@: push ebx mov ebx, 1 mov ecx, 1 @@: lea eax, [ebx+ecx] cmp edx, 3 jbe @f mov ebx, ecx mov ecx, eax dec edx jmp @b @@: pop ebx ret fib: mov edx, [esp+8] cmp edx, 0 ja @f mov eax, 0 ret @@: cmp edx, 2 ja @f mov eax, 1 ret @@: push ebx mov ebx, 1 mov ecx, 1 @@: lea eax, [ebx+ecx] cmp edx, 3 jbe @f mov ebx, ecx mov ecx, eax dec edx jmp @b @@: pop ebx ret CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein 17. 15.04.2025 Slide 86 Main memory (primary storage or internal memory) ‒ The main memory is the only storage which the CPU can directly access ‒ to read instructions and data ‒ to store results after their execution ‒ The main memory and the registers are volatile: they keep values only if powered. ‒ Enhancements of JvN-Architecture to avoid waiting for the memory by ‒ Bus Buffers ‒ Processor Cache "Driver" – program which control the interactions between components. main memory SAR SDR System Bus System Bus Processor Bus Driver &Buffer Bus Driver &Buffer Bus Driver & Buffer Processor cache memory ALU & Control Unit Registers Registers Registers for values which "wait" for the bus or the memory SDR: Storage Data register SAR: Storage Address registers 18. 15.04.2025 Slide 87 Why don't we just take the fastest storage for all purposes? → Storage hierarchy Registers Processor cache storage Main memory Flash drives, USB Secondary storage: Hard disk Tertiary storage: Archives on CD-ROMs, DVD, magnetic tapes,… price persistance velocity in the processor 19. 15.04.2025 Slide 89 Computer Periphery – name other devices which you use with your computer: • Input devices • Output devices • Mixed Input/output devices • External (persistent) storage • sometimes visible, sometimes integrated 20. 15.04.2025 Slide 90 Drivers: Connect periphery of different producers to the computer Problem: ‒ Each peripheral device hat its own proprietory "language" (protocoll) ‒ signals which are received from ‒ signals which have to be sent to the computer Solution ‒ Drivers (controller) translate between the protocoll of the computer's bus and the devices' protocoll. Periphery device Controller System-Bus device interface bus interface Connection to processor Connection to device: → drivers Controller decides which device may use the bus. 21. 15.04.2025 Slide 91 OPERATING SYSTEMS: Why do we usually need not care for these hardware aspects? Modern operating systems von Andrew S. Tanenbaum , Pearson , 4th edition, chapter 1. • contains basics about computer architecture (chapter 1.3) also Tutorialspoint: Operating Systems - https://www.tutorialspoint.com/operating_system/os_quick_guide.htm CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel- Sonnenschein 22. 15.04.2025 Slide 92 Operating System (OS): Hiding the computer's complex hardware from the user Software: Software: Application SW •asking for input •offering output Operating System System Software •using files, I/O-Devices Hardware: CPU CPU Storage Storage I/O I/O Multi-user system CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein 23. 15.04.2025 Slide 93 Functions of Operating Systems Operating System Memory Manage- ment Processor Manage- ment Device Manage- ment File Manage- ment Security Performanc e control Job accounting Error detecting aids User interface CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein 24. 15.04.2025 Slide 94 Functions of Operating Systems • File System Management: • The OS organizes the efficient storage of files on your hard drive. So, the user need not care about storage addresses and can view the storage simply as "documents in file folders" • Device Drivers: Drivers translate between hardware (devices) and software which uses these devices • The OS manages that the processor can effectively communicate via drivers with other devices. • Networking: • For each connection to a network (e.g. internet) the OS supervises the correct dispatch and receipt of messages. • Security: Different users of a computer may have different access rights. • The OS manages users and their rights. • User interface (UI): • The OS accepts user inputs and translates them into computer instructions • Shell: alphanumerical user interface, GUI: graphical user interface • Process Management and Interrupts: The OS • ensures that each process and application receives enough of the processor's time to function properly • ensures that the processor is nearly never idling (lazy): Using as many processor cycles as possible for real work • For multi-process multi-tasking interrupt signals are necessary to prompt the operating system to stop work on one process and start work on another. • Memory and Storage management: • Each process must have enough memory for its execution, and it must be guaranteed that processes do not affect each other: no process is allowed to run into the memory space of another process. • The different types of memory (cache, main memory, secondary storage) in the system must be used properly so that each process can run most effectively. CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein 25. 15.04.2025 Slide 95 Summary The computer hardware is usually built according to the von-Neumann-Architecture (Princeton-Architecture) ‒ which consists of CPU (Control Unit and ALU), main memory, I/O-interface, and Bus ‒ and determines ‒ the structure and mode of operation of the processor ‒ the coding of instructions and data ‒ the structure of the memory ‒ A processor can only perform its native machine code. ‒ Assembler code is a very low level programming language. ‒ The computer periphery consist of the devices for input/output and persistent storage. ‒ Peripheral devices are connected via specific device interfaces (drivers) and controller to the bus. ‒ The Operation systems manages all tasks to hide the computer's hardware complexity from the user. CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein

![15.04.2025 Slide 84 Low Level Languages: Machine L. and assembly L. Low Level Languages: ‒ easy to execute by the computer's processor ‒ but difficult to understand by humans ‒ Machine language ‒ is specific to the type of processor ‒ instructions can be directly executed by the machine's processor ‒ instructions are represented in binary code ‒ there are jump, arithmetic & logic (ALU), or transfer operations which move data in a CPU register or in memory. ‒ Assembly language ‒ "symbolic" machine code: one-to-one-translation of machine code into more readable words 8B54240883FA007 706B800000000C3 83FA027706B8010 00000C353BB0100 0000B9010000008 D041983FA037607 8BD989C14AEBF15 BC3 8B54240883FA007 706B800000000C3 83FA027706B8010 00000C353BB0100 0000B9010000008 D041983FA037607 8BD989C14AEBF15 BC3 fib: mov edx, [esp+8] cmp edx, 0 ja @f mov eax, 0 ret @@: cmp edx, 2 ja @f mov eax, 1 ret @@: push ebx mov ebx, 1 mov ecx, 1 @@: lea eax, [ebx+ecx] cmp edx, 3 jbe @f mov ebx, ecx mov ecx, eax dec edx jmp @b @@: pop ebx ret fib: mov edx, [esp+8] cmp edx, 0 ja @f mov eax, 0 ret @@: cmp edx, 2 ja @f mov eax, 1 ret @@: push ebx mov ebx, 1 mov ecx, 1 @@: lea eax, [ebx+ecx] cmp edx, 3 jbe @f mov ebx, ecx mov ecx, eax dec edx jmp @b @@: pop ebx ret 32-bit x86 machine and MAMS-assembly code Quelle: https://en.wikipedia.org/wiki/Low-level_programming_language#Low- level_programming_in_high-level_languages Program in hexadecimal machine code CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein](https://image.slidesharecdn.com/2025cs4sciencepart1-2a-250527165744-b1426572/75/2025_CS4Science_Part1-2a-python-data-coding-15-2048.jpg)

![15.04.2025 Slide 85 Examples of assembly instructions MAMS-assembly code: Two-address code ‒ Structure of a machine instruction (here: two address code) <operation code> <operand1> <operand2> mov eax, 0 ‒ Put the value 0 into register eax → Transport instruction ‒ A register is a small but very fast memory word for storing temporary values lea eax, [ebx+ecx] → Arithmetic instruction ‒ add the value which is stored at address ebx +ecx to the value in register eax dec edx → Arithmetic instruction ‒ subtract 1 from the value in register edx cmp edx, 3 → Arithmetic/Logic instruction ‒ Compare the value in register edx with 3. If equal, a flag will be set to inform the next instruction jbe @f → Jump instruction ‒ jbe means "jump if equal" (i.e. if the flag is set) ‒ @f is a symbol for the next (unnamed) label @@ fib: mov edx, [esp+8] cmp edx, 0 ja @f mov eax, 0 ret @@: cmp edx, 2 ja @f mov eax, 1 ret @@: push ebx mov ebx, 1 mov ecx, 1 @@: lea eax, [ebx+ecx] cmp edx, 3 jbe @f mov ebx, ecx mov ecx, eax dec edx jmp @b @@: pop ebx ret fib: mov edx, [esp+8] cmp edx, 0 ja @f mov eax, 0 ret @@: cmp edx, 2 ja @f mov eax, 1 ret @@: push ebx mov ebx, 1 mov ecx, 1 @@: lea eax, [ebx+ecx] cmp edx, 3 jbe @f mov ebx, ecx mov ecx, eax dec edx jmp @b @@: pop ebx ret CS4Science (Inf962 / inf980) – Lecture in Summer term 2025 © Dr. Ute Vogel-Sonnenschein](https://image.slidesharecdn.com/2025cs4sciencepart1-2a-250527165744-b1426572/75/2025_CS4Science_Part1-2a-python-data-coding-16-2048.jpg)