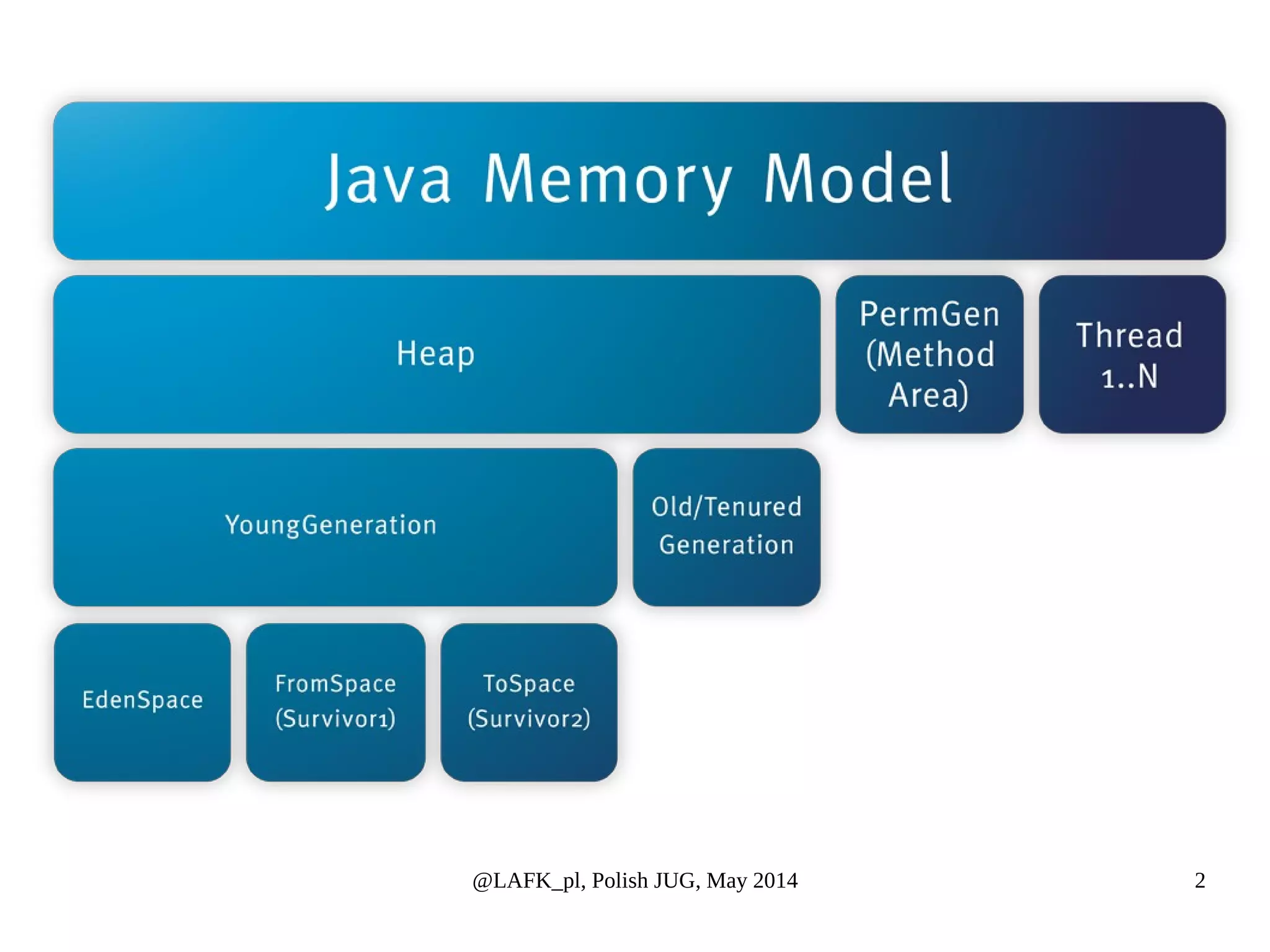

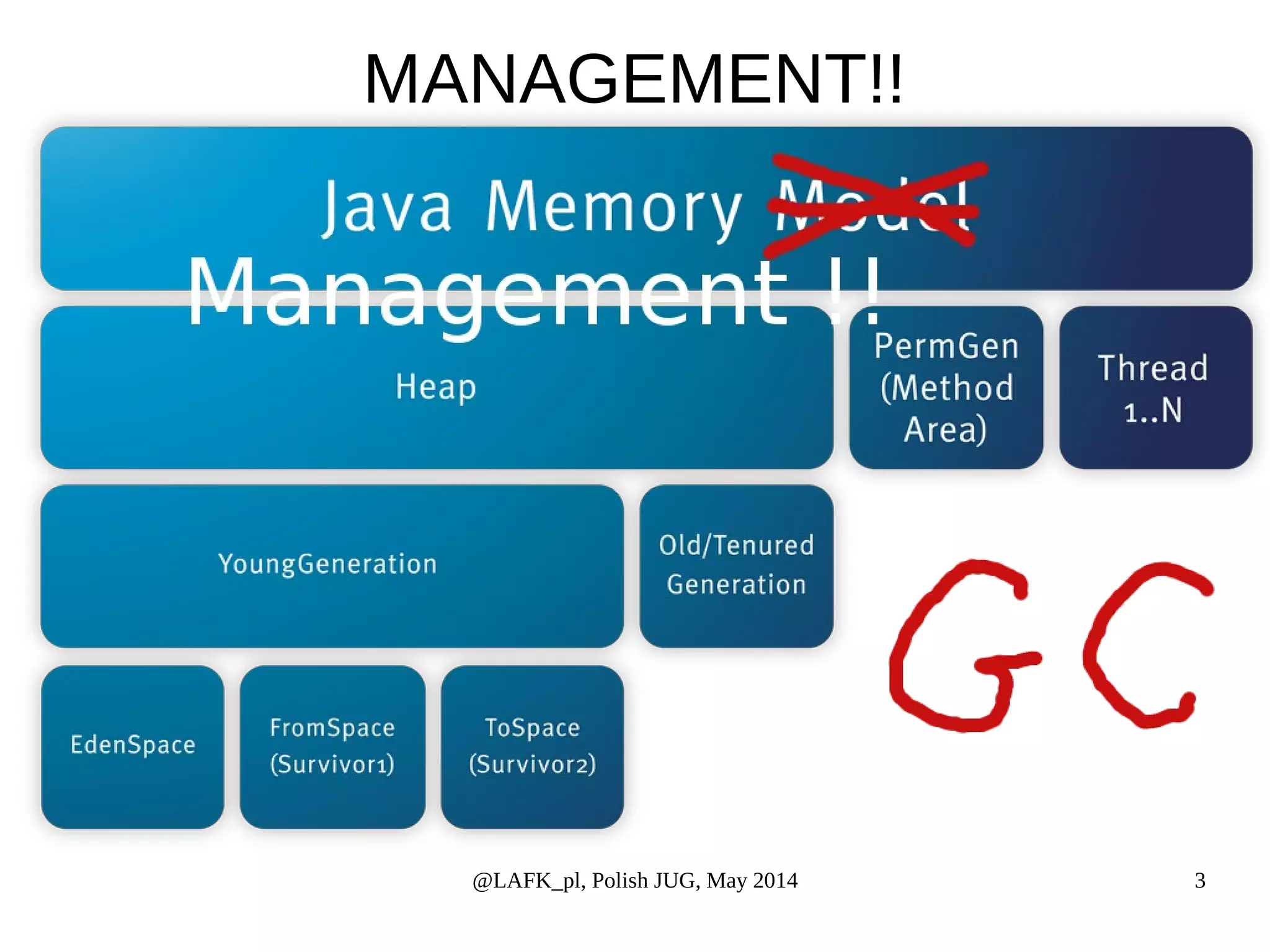

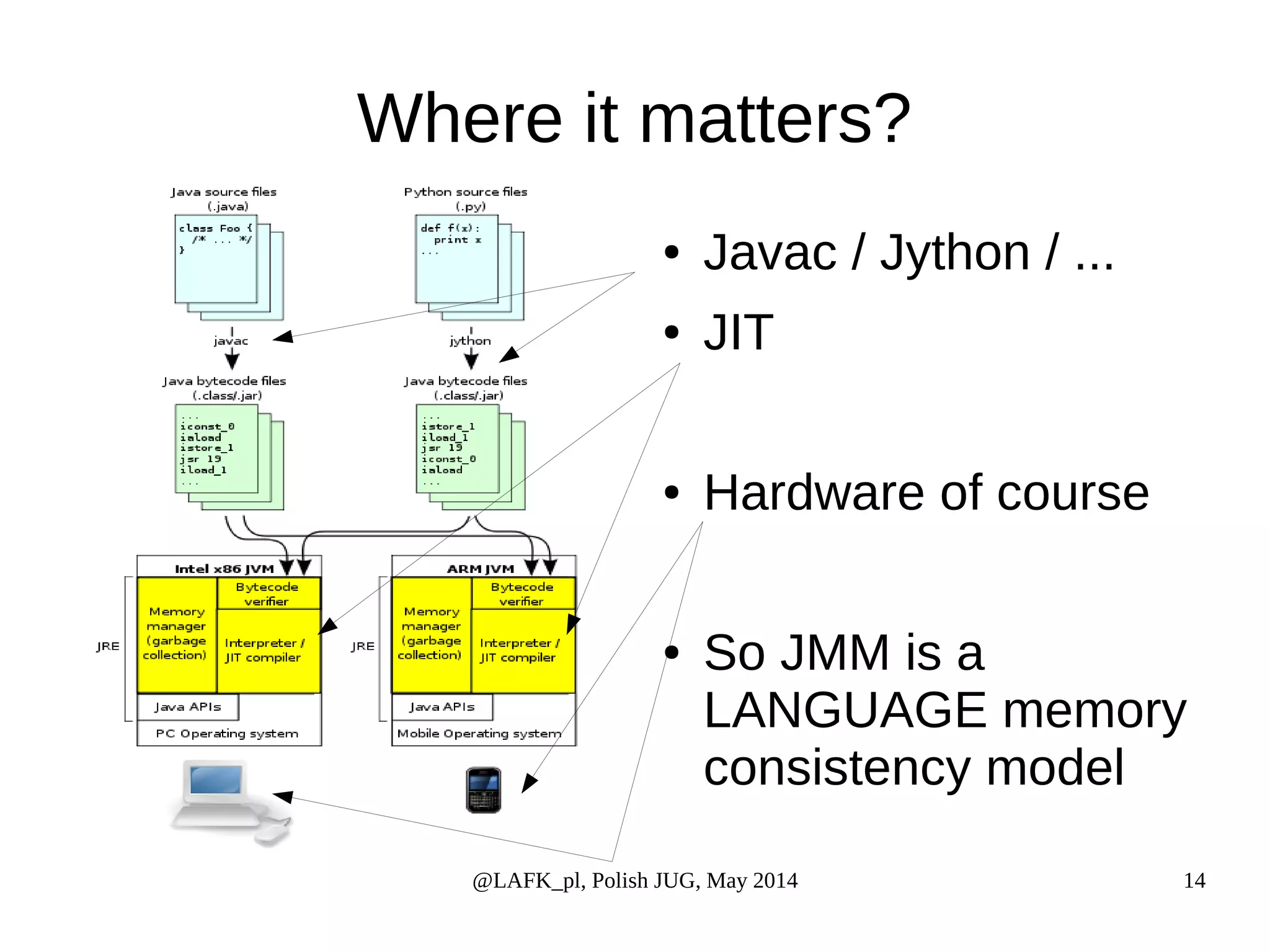

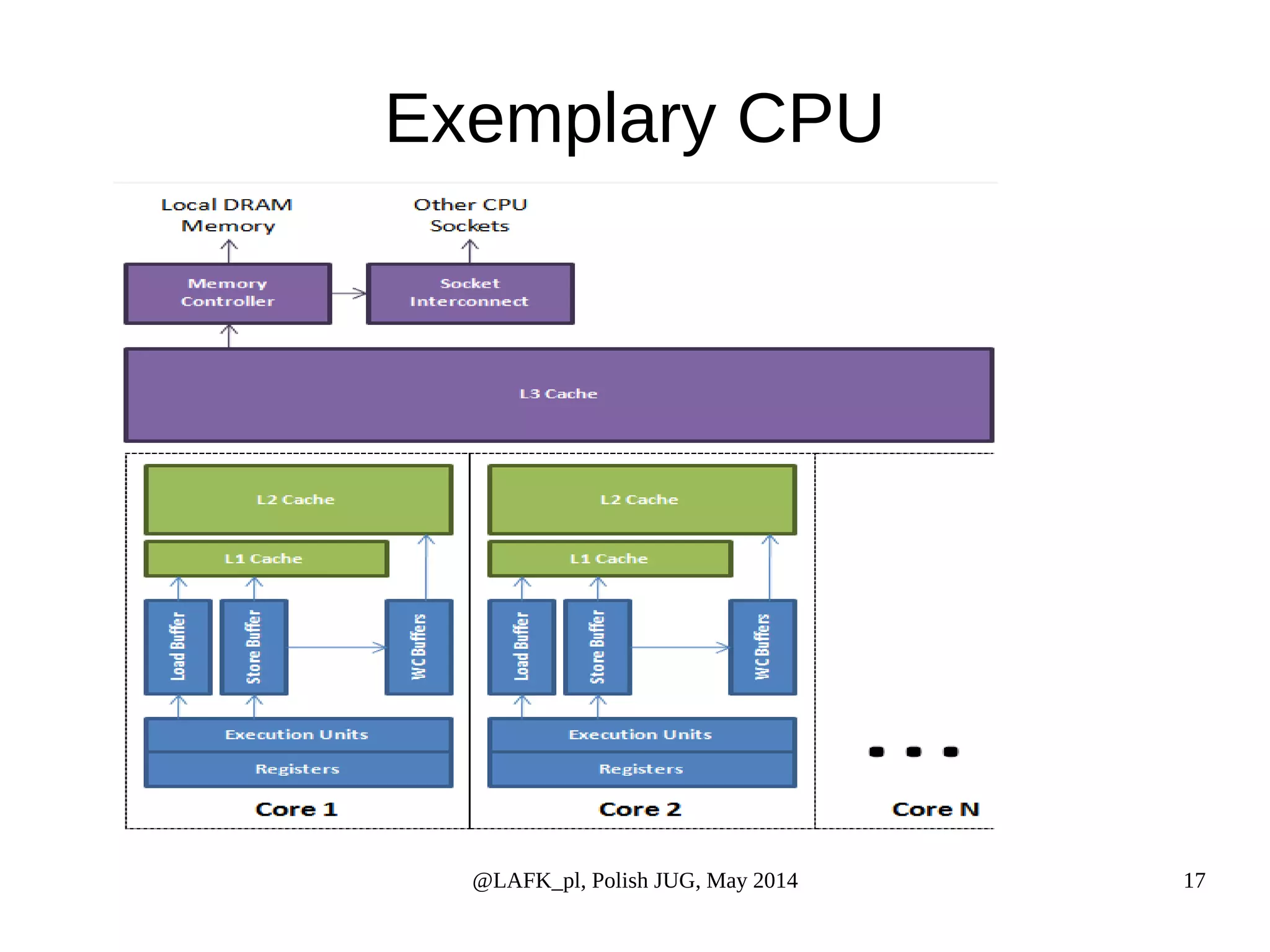

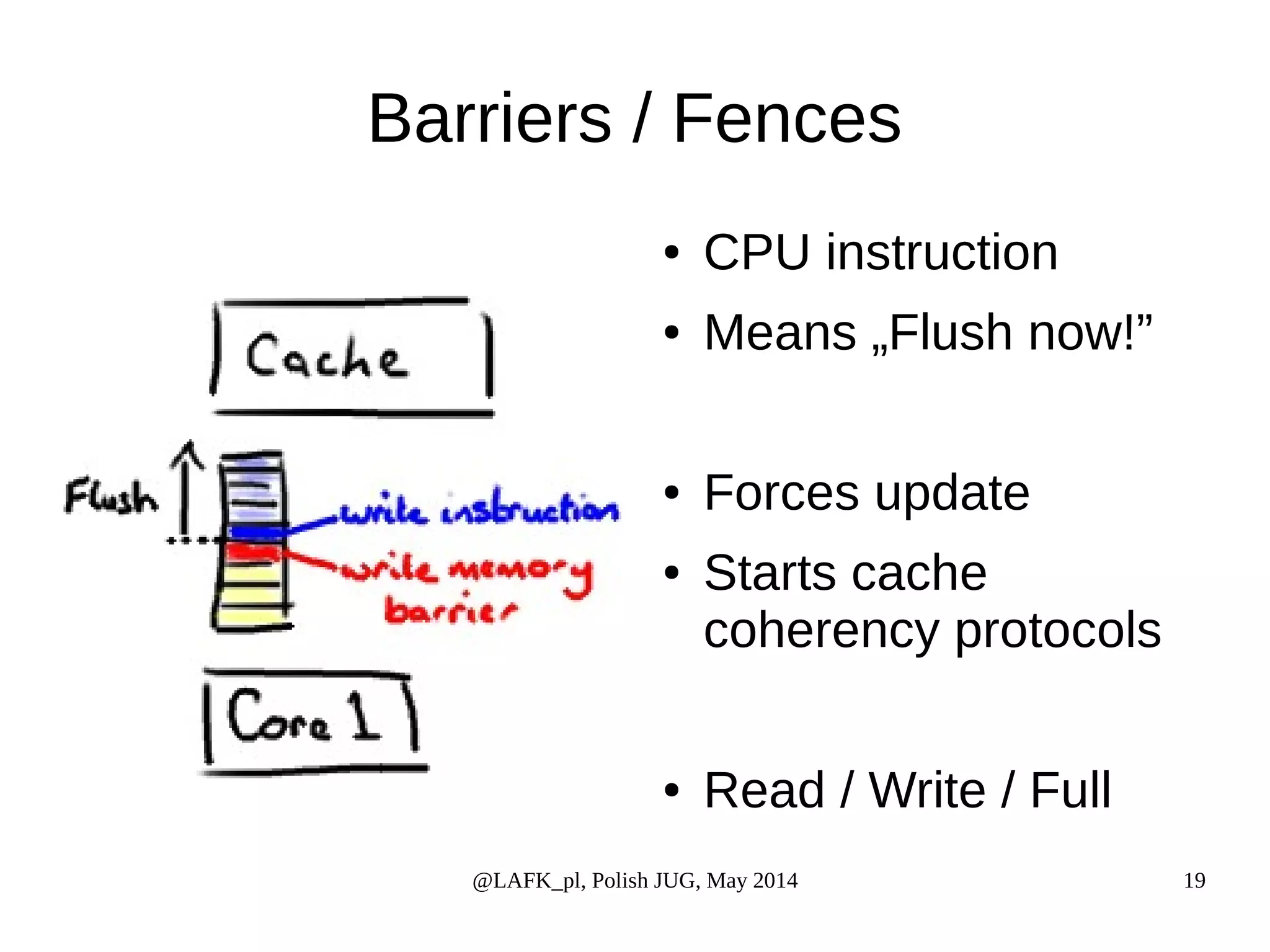

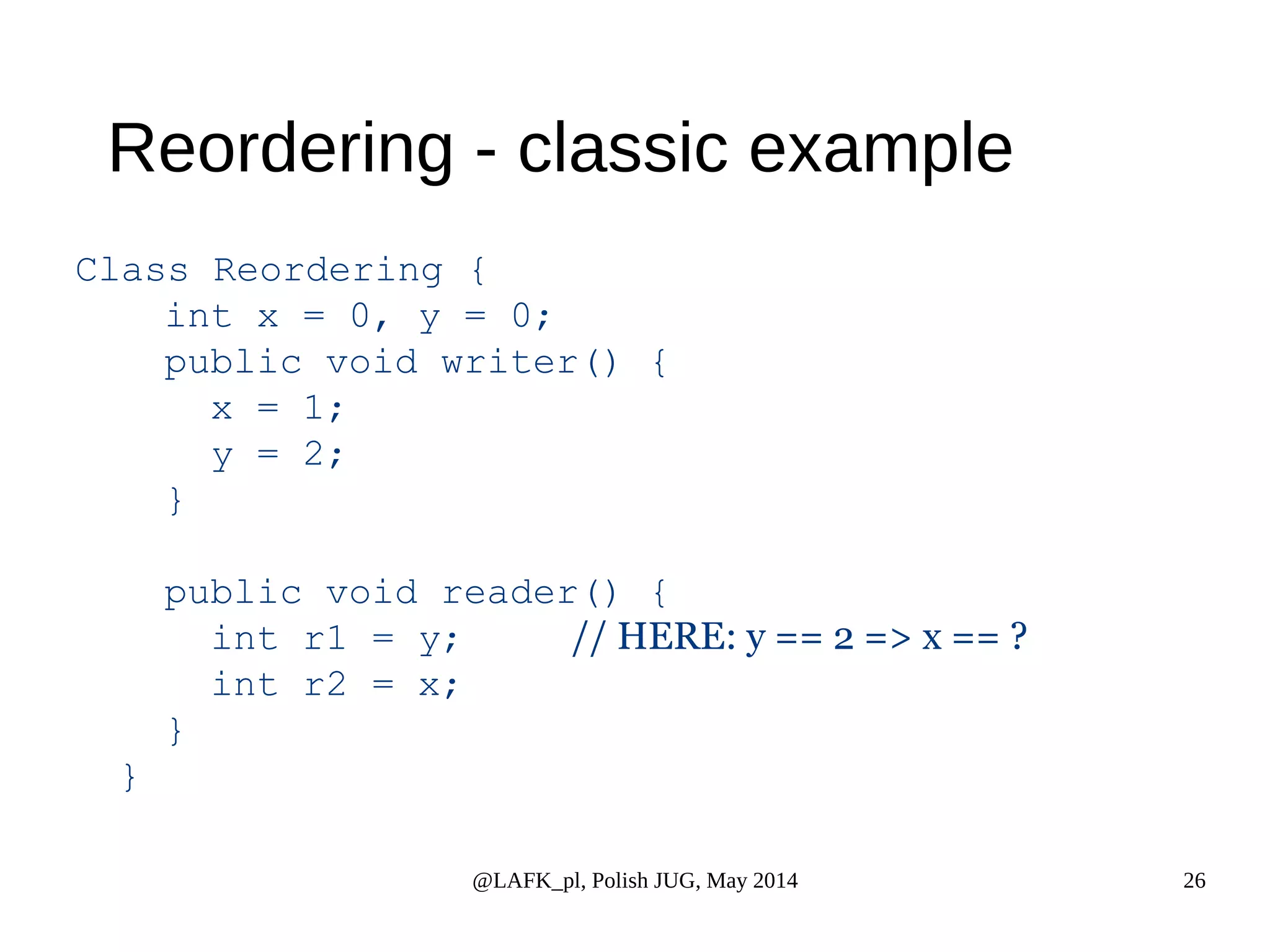

The document discusses the Java Memory Model (JMM), highlighting issues with memory consistency, execution traces, and optimizations in multi-threaded environments. It outlines the significance of barriers, fences, and specific constructs like 'volatile' and 'synchronized' in ensuring visibility and legal executions of programs. Additionally, it contrasts past and current practices in Java's handling of memory to enhance performance and consistency.