The document presents a novel feedback architecture-based design for the AES-128 encryption algorithm aimed at optimizing chip size and enhancing encryption speed. The proposed solution simplifies the chip pin count and effectively reduces the overall area through a modified data transmission mode. The paper compares this feedback architecture to a traditional pipeline approach, demonstrating significant performance improvements and applications for high-speed data encryption in various fields.

![slightly different from other rounds in that the MixCloumns transformation is removed. The output of each round is fed to the next round as input. Total ten rounds of transformations produces encrypted output called cipher text. B. Decryption The Decryption process is reverse process of Encryption and it also consists of ten rounds of transformation. But the input to round #1 will be EX-OR of cipher text and key 10. Each round from round #1 to round #9 again consists of four different transformation internally except 10 round. These transformations are namely InvSubBytes, InvShiftRows, InvMixColumns and InvAddRound key transformation. Round #10 is slightly different from other rounds in that the InvMixColumns transformation is removed. Like in Encryption output of one round is fed as input to the next round. The usage of keys also reverse in this case i.e. round #1 uses key 9 and round #2 uses key 8 and so on. Total ten rounds of transformations produces decrypted output i.e. Plain Text. C. Key Generation This part takes a 128 bit key. The 128 bit key is divided into four words represented in w[0,3]. These four words are used as it is for encryption initially before starting of a round and for round 10 of decryption part. These 4 words are used for producing a new key represented by w[4,7]. Which is used for round #1 of encryption and round #9 of decryption. These 4 words represented by w[4,7] which is key 1, is used for producing key2 represented by w[8,11]. Like this it will generate total 40 words i.e. 10 keys. III. AES Specification For the AES algorithm, the number of rounds to be performed during the execution of the algorithm is dependent on the key size. The number of rounds is represented by Nr, where Nr = 10 when Nk = 4, Nr = 12 when Nk = 6, and Nr = 14 when Nk = 8. The only KeyBlock-Round combinations that conform to this standard are given in Fig. 2. array of 4-byte words, denoted [wi], with I in the range 0≤ I <Nb(Nr + 1). The key expansion has Temp, Subword(), Rotword(), Rcon[i],w[i - Nk] stages. The following example will show its detail. Cipher Key = 2b 7e 15 16 28 ae d2 a6 ab f7 15 88 09 cf 4f 3c for Nk = 4, which results in w0 = 2b7e1516, w1 = 28aed2a6, w2 = abf71588, w3 = 09cf4f3c Figure 3:Key Generation Example. B. Encryption (cipher) The Encryption consists of 4 different transformation. The individual transformations SubBytes(), ShiftRows(), MixColumns(), and AddRoundKey() process the State and are described in the following subsections. All Nr rounds are identical with the exception of the final round, which does not include the MixColumns()transformation. 1. SubBytes( ). The SubBytes() transformation is a non-linear byte substitution that operates independently on each byte of the State using a substitution table (S-box). This S-box is invertible, is constructed by composing two transformations: The following Figure.4. illustrates the effect of the SubBytes() function on the state. Figure 4: Subbytes applies the s-box to each of the state. Figure 2: Key-Block-Round Combinations. A. Key Generation The AES algorithm takes the cipher key, K, and performs a Key Expansion routine to generate a key schedule. The Key Expansion generates a total of Nb (Nr + 1) words: the algorithm requires an initial set of Nb words, and each of the Nr rounds require Nb words of key data. The resulting key schedule consists of a linear 2. ShiftRows( ). In the ShiftRows() transformation, the bytes in the last three rows of the State are cyclically shifted over different numbers of bytes (offsets). The first row,r=0,is not shifted.Specifically, the ShiftRows( ) transformation proceeds as follows:](https://image.slidesharecdn.com/ieeeonfpga-140124033312-phpapp02/75/Paper-on-Optimized-AES-Algorithm-Core-Using-FeedBack-Architecture-2-2048.jpg)

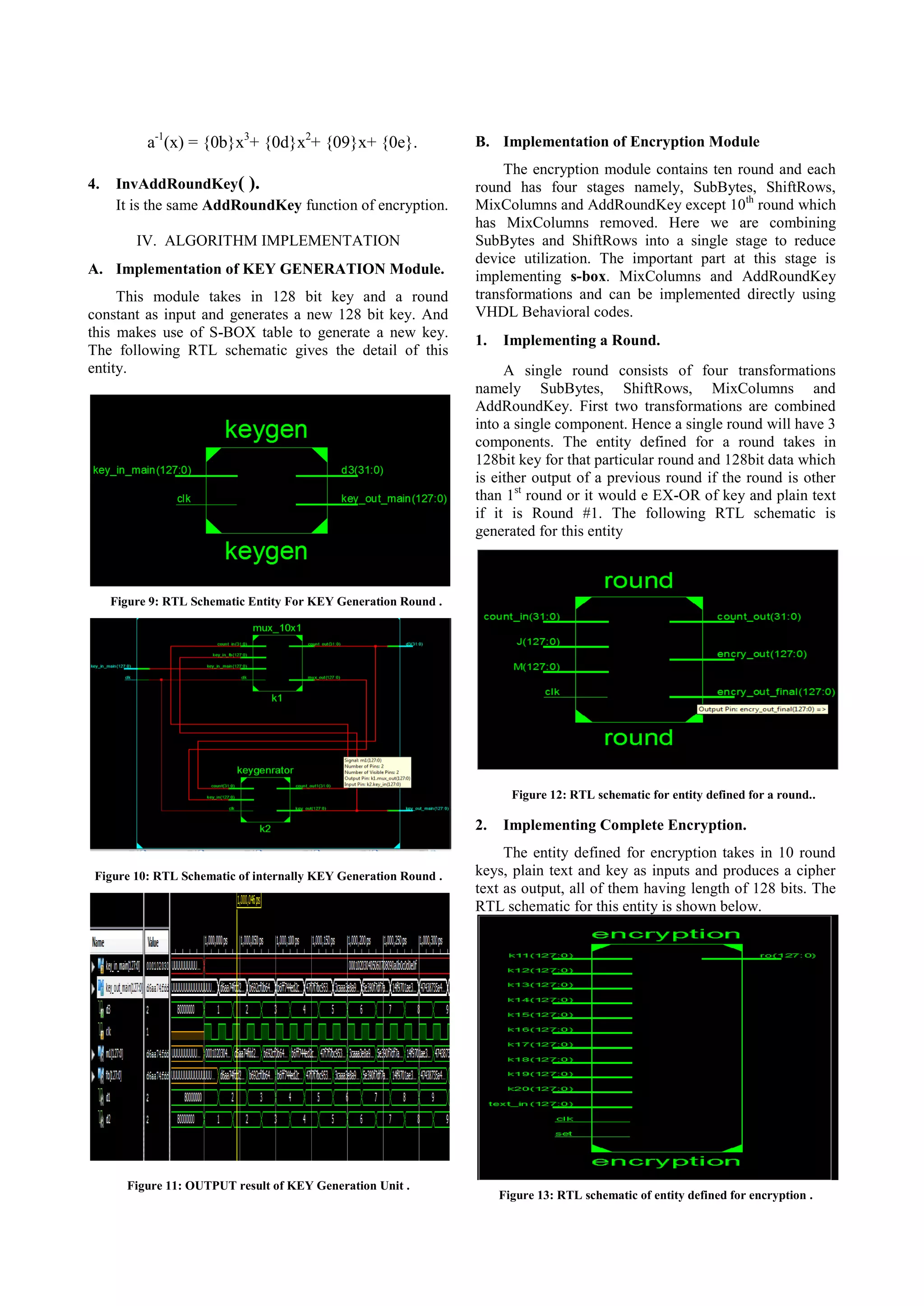

![V.COMPARISON BASED ON TWO DISTINCT ARCH. The following chart compares the previous Pipeline Architecture and Latest Feedback Architecture. In which it compares the resources used by these both Architecture. 400 applied for the computer forensics which requires high speed of data encryption. In the future, we will focus on efficient implementations of other common symmetrickey encryption algorithms, such as Blowfish, Serpent and Twofish. Besides, future work will also include GPU implementations of hashing and public key algorithms(e.g. MD5, SHA-1 and RSA) in order to create a complete cryptographic framework. REFERENCE 300 [1]. J. Daemen and V. Rijmen, AES Proposal:Rijndael, AES Algorithm Submission, September 3, 1999. http://csrc.nist.gov/encryption/aes/rijndael/Rijndael.p df. 200 100 0 PIPELINE ARCH [2]. J. Daemen and V. Rijmen, The block cipher Rijndael, Smart Card research and Applications, LNCS 1820, Springer-Verlag, pp. 288-296. FEEDBACK ARCH Figure 18: No. Of Resources Used By Individual Arch. Number Of ROM’s used by an individual architecture Architecture FeedBack PipeLine Encryption 16 160 Decryption 16 160 Key Generation 04 [3]. Maire McLoone, John V. McCanny:Single-Chip FPGA Implementation of the advanced encryption standard algorithm. www.springerlink.com/index/eajtwybnuw9hhejjh. [4]. FIPS PUB197, Advanced Encryption Standard (AES),National Institute of Standards and Technology, U.S. Department of Commerce, November 2001. http://csrc.nist.gov/publications/fips/fips197/fips-197 20 Figure 19: Comparison Of Two Arch. VI. APPLICATION OF AES ALGORITHM. 1. 2. 3. 4. 5. 6. For wireless communication devices like PDA’s multimedia cellular phones AES can apply. It can be used for security of Smart cards, wireless sensor networks, wireless mesh Networks. AES have high computational efficiency, so as to be usable in high speed applications, such as broad band links. AES is very well suited for restricted-space environments where either encryption or decryption is implemented. It has very low RAM and ROM requirements. Web servers that need to handle many encryption sessions. Any kind application where security is needed for our current cryptosystems. CONCLUSION AND FUTURE WORK To overcome the issue of low efficiency over the traditional CPU-based implementation of AES, we proposed a new algorithm for AES method in this paper. According to our proposal, we designed and implemented the feedback AES algorithm. Our implementation achieves up to 10x speedup over the implementation of AES on a comparable CPU. Our implementation can be [5]. Suresh Sharma, T S BSudarshan: Design of an Efficient Architecture for Advanced Encryption Standard Algorithm Using Systonic Structure. http://www.hipc.org/hipc2005/posters/systolic.pdf](https://image.slidesharecdn.com/ieeeonfpga-140124033312-phpapp02/75/Paper-on-Optimized-AES-Algorithm-Core-Using-FeedBack-Architecture-6-2048.jpg)