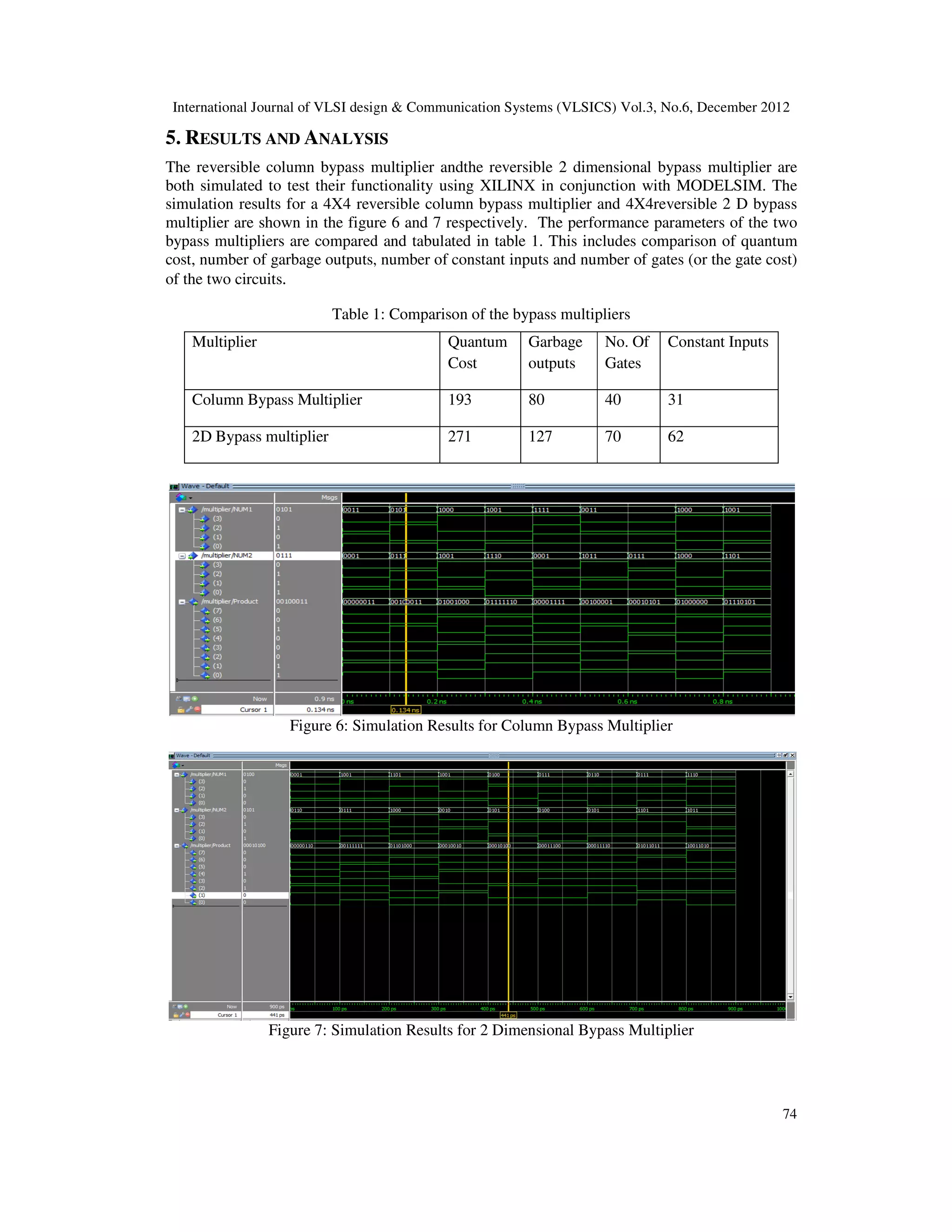

This paper presents the design of reversible multipliers aimed at reducing power dissipation in digital signal processing (DSP) applications, focusing on bypass multipliers that optimize performance during linear filtering and FFT computations. The design incorporates techniques such as column and 2-D bypassing to minimize switching activities when input coefficients are zero, effectively utilizing reversible logic to achieve further energy efficiency. The paper includes comparisons of the proposed multipliers' performance parameters and discusses their applications in scenarios requiring significant zero padding.

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.6, December 2012 DOI : 10.5121/vlsic.2012.3606 67 DESIGN OF REVERSIBLE MULTIPLIERS FOR LINEAR FILTERING APPLICATIONS IN DSP Rakshith Saligram1 and Rakshith T.R2 1 Department of Electronics and Communication, B.M.S College of Engineering, Bangalore, India rsaligram@gmail.com 2 Department of Telecommunication, R. V College of Engineering, Bangalore, India rakshithtgm91@gmail.com ABSTRACT Multipliers in DSP computations are crucial. Thus modern DSP systems need to develop low power multipliers to reduce the power dissipation. One of the efficient ways to reduce power dissipation is by the use of bypassing technique. If a bit in the multiplier and/or multiplicand is zero the whole array of row and/or diagonal will be bypassed and hence the name bypass multipliers. This paper presents the column Bypass multiplier and 2-D bypass multiplier using reversible logic; Reversible logic is a more prominent technology, having its applications in Low Power CMOS and quantum computations. The switching activity of any component in the bypass multiplier depends only on the input bit coefficients. These multipliers find application in linear filtering FFT computational units, particularly during zero padding where there will be umpteen numbers of zeros. A bypass multiplier reduces the number of switching activities as well as the power consumption, above which reversible logic design acts to further almost nullify the dissipations. KEYWORDS Reversible logic, Low power Multipliers, Column Bypass multiplier, 2-D Bypass Multiplier ,Reduced Switching Activity, Fast Fourier Transform, Zero Padding. 1. INTRODUCTION Multiplication is an essential arithmetic operation for common DSP applications such as Filtering, computation of FFTs etc. High end DSP processors also need to cater to the execution speed, accuracy of the results and also keep an eye on the power consumption. To achieve this, parallel array multipliers are used, where there is a need to check the power efficiency. The dynamic power consumption (i.e., power loss due to switching activity) can be reduced by bypassing technique. The switching activity of the component used in the design depends on the input bit coefficient. This means that if the input bit coefficient is zero corresponding rows or column of the adders need not be activated. If the multiplicand (or the multiplier) contains more zeros, then higher power reduction can be achieved, which is the case in FFT computation. Conventional combinational logic circuits are known to dissipate heat for every bit of information that is lost. This is also evident from the second law of thermodynamics which states that any irreversible process leads to loss of energy. R.Landauer [1] showed that any gate that is irreversible necessarily dissipates energy, and each irreversible bit generates k*T ln2 joules of heat where k is Boltzmann’s constant (1.38 x 10-23 joules/Kelvin) and T is temperature in Kelvin. C.H.Bennett in 1973 [2] showed that an irreversible computer can always be made reversible. Reversible logic circuits naturally take care of heating since in a reversible logic every](https://image.slidesharecdn.com/3612vlsics06-190416121734/75/DESIGN-OF-REVERSIBLE-MULTIPLIERS-FOR-LINEAR-FILTERING-APPLICATIONS-IN-DSP-1-2048.jpg)

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.6, December 2012 input vector can be uniquely recovered from its output vectors and therefore no information is lost. A reversible logic gate is an N input, N output logic device with one to one mapping. This helps to determine the outputs from the inputs and also the inputs can be uniquely recovered from the outputs. Extra inputs or outputs are added so that the number of i number of outputs whenever it is necessary. An important constraint present on the design of a reversible logic circuit using reversible logic gate is that fan circuit should be designed using min achieve optimization is that the designed circuit must produce minimum number of garbage outputs. They must use minimum number of constant inputs. The gate count should also be minimum in a given reversible logic design. This paper presents an archetypical design of multipliers using Row Bypassing and 2D Bypassing circuits using reversible logic in the literature. This paper is organized as follows; S discusses the prior work on both reversible logic and importance of bypass multipliers in linear filtering column bypass and 2-Dimenstional Row and column bypass technique Section 5 gives the comparison of performance parameters of the two multipliers and simulation results. Conclusions and references follow. 2. PRIOR WORK 2.1. Parallel Multiplier V/s Bypass Multiplier Consider the multiplication of tw produce the product P=p2n-1 p2n....p The multiplicand ai is added to the incoming partial product bit based on the value of the multiplier bit bj and each row now adds the multiplicand to the incoming partial product (PP) PPi to generate the outgoing partial product PP(i+1) if bj is 1, else passed unchanged vertically downwards. Conventional 4X4 Braun Multiplier array consists of 3 rows of carry sav (CSAs) in which each row contain 3 full adders (FAs). Each FA in turn has 3 inputs and 2 outputs- the sum and the carry. To design a low power multiplier is to reduce the switching activity [12] and literature supports this statement by providing a direct approach of designing a low power full adder. This can be achieved through architectural modifications such as row, column or 2 dimensional bypassing. The technique of bypassing the columns of the adders has an upper hand on the technique of bypassing the rows of the adders in two aspects: Firstly it eliminates the extra correcting circuits that may be needed [7]. Secondly, the modified full adder in column bypassing multiplier is much simpler than that used in row bypassing multiplier [7]. Since all the partial productsaibj addition operation in the (i+j)th column can be bypassed. In column bypass multiplier the modified full adder is simpler than that in the row bypass multiplier. In the carry save array, the full adder is replaced by a modi multiplexer. If the bit, ai in the multiplicand is 0, the inputs in the (i+1) th column will be disabled and the carry output in the column must be set to 0 to produce the correct output. Thi protecting process can be done by adding an AND gate at the output of the last row of the CSA. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.6, December 2012 input vector can be uniquely recovered from its output vectors and therefore no information is eversible logic gate is an N input, N output logic device with one to one mapping. This helps to determine the outputs from the inputs and also the inputs can be uniquely recovered from the outputs. Extra inputs or outputs are added so that the number of inputs is made equal to the number of outputs whenever it is necessary. An important constraint present on the design of a reversible logic circuit using reversible logic gate is that fan-out is not allowed. A reversible circuit should be designed using minimum number of reversible gates. One key requirement to achieve optimization is that the designed circuit must produce minimum number of garbage outputs. They must use minimum number of constant inputs. The gate count should also be rsible logic design. This paper presents an archetypical design of multipliers using Row Bypassing and 2D Bypassing circuits using reversible logic in the literature. This paper is organized as follows; S discusses the prior work on both reversible logic and bypass multipliers. Section 3 importance of bypass multipliers in linear filtering, Section 4 gives the proposed design of the Dimenstional Row and column bypass techniques using reversible logic. gives the comparison of performance parameters of the two multipliers and simulation results. Conclusions and references follow. Parallel Multiplier V/s Bypass Multiplier of two unsigned n-bit numbers, A=an-1an-2....a0 and B=b ....p0. The product can be written as: The multiplicand ai is added to the incoming partial product bit based on the value of the nd each row now adds the multiplicand to the incoming partial product (PP) PPi to generate the outgoing partial product PP(i+1) if bj is 1, else passed unchanged vertically downwards. Conventional 4X4 Braun Multiplier array consists of 3 rows of carry sav (CSAs) in which each row contain 3 full adders (FAs). Each FA in turn has 3 inputs and 2 To design a low power multiplier is to reduce the switching activity [12] and literature supports a direct approach of designing a low power full adder. This can be achieved through architectural modifications such as row, column or 2 dimensional bypassing. The technique of bypassing the columns of the adders has an upper hand on the technique of ssing the rows of the adders in two aspects: Firstly it eliminates the extra correcting circuits that may be needed [7]. Secondly, the modified full adder in column bypassing multiplier is much simpler than that used in row bypassing multiplier [7]. j, 0 ≤ j ≤ n-1 are zeroes, if bit ai in the multiplicand is zero, the addition operation in the (i+j)th column can be bypassed. In column bypass multiplier the modified full adder is simpler than that in the row bypass multiplier. In the carry save array, the full adder is replaced by a modified full adder which consists of a full adder attached to a 2:1 multiplexer. If the bit, ai in the multiplicand is 0, the inputs in the (i+1) th column will be disabled and the carry output in the column must be set to 0 to produce the correct output. Thi protecting process can be done by adding an AND gate at the output of the last row of the CSA. International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.6, December 2012 68 input vector can be uniquely recovered from its output vectors and therefore no information is eversible logic gate is an N input, N output logic device with one to one mapping. This helps to determine the outputs from the inputs and also the inputs can be uniquely recovered from the nputs is made equal to the number of outputs whenever it is necessary. An important constraint present on the design of a out is not allowed. A reversible imum number of reversible gates. One key requirement to achieve optimization is that the designed circuit must produce minimum number of garbage outputs. They must use minimum number of constant inputs. The gate count should also be This paper presents an archetypical design of multipliers using Row Bypassing and 2D Bypassing circuits using reversible logic in the literature. This paper is organized as follows; Section 2 bypass multipliers. Section 3 shows the gives the proposed design of the s using reversible logic. gives the comparison of performance parameters of the two multipliers and simulation and B=bn-1 bn-2...b0 to The multiplicand ai is added to the incoming partial product bit based on the value of the nd each row now adds the multiplicand to the incoming partial product (PP) PPi to generate the outgoing partial product PP(i+1) if bj is 1, else passed unchanged vertically downwards. Conventional 4X4 Braun Multiplier array consists of 3 rows of carry save adders (CSAs) in which each row contain 3 full adders (FAs). Each FA in turn has 3 inputs and 2 To design a low power multiplier is to reduce the switching activity [12] and literature supports a direct approach of designing a low power full adder. This can be achieved through architectural modifications such as row, column or 2 dimensional bypassing. The technique of bypassing the columns of the adders has an upper hand on the technique of ssing the rows of the adders in two aspects: Firstly it eliminates the extra correcting circuits that may be needed [7]. Secondly, the modified full adder in column bypassing multiplier is much in the multiplicand is zero, the addition operation in the (i+j)th column can be bypassed. In column bypass multiplier the modified full adder is simpler than that in the row bypass multiplier. In the carry save array, the fied full adder which consists of a full adder attached to a 2:1 multiplexer. If the bit, ai in the multiplicand is 0, the inputs in the (i+1) th column will be disabled and the carry output in the column must be set to 0 to produce the correct output. This protecting process can be done by adding an AND gate at the output of the last row of the CSA.](https://image.slidesharecdn.com/3612vlsics06-190416121734/75/DESIGN-OF-REVERSIBLE-MULTIPLIERS-FOR-LINEAR-FILTERING-APPLICATIONS-IN-DSP-2-2048.jpg)

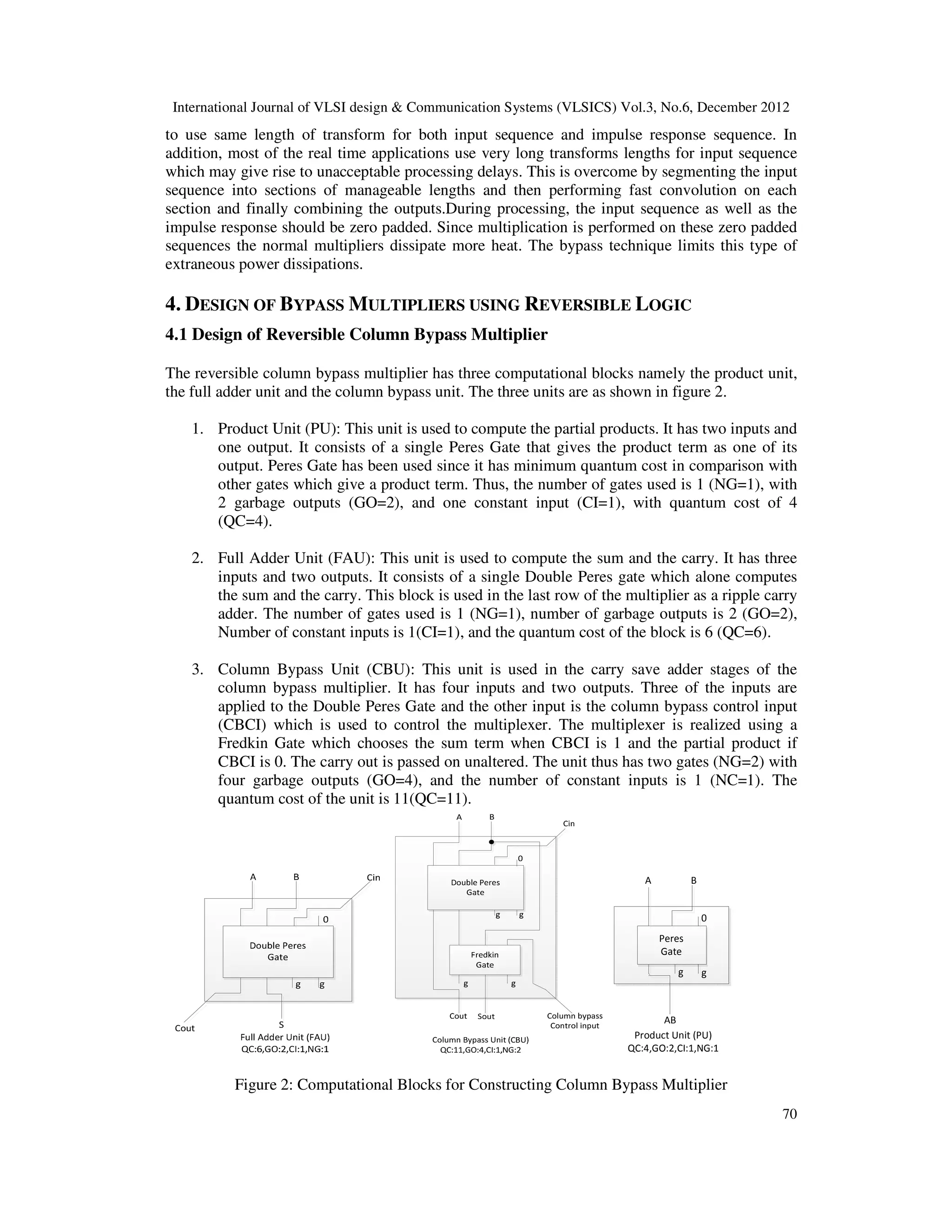

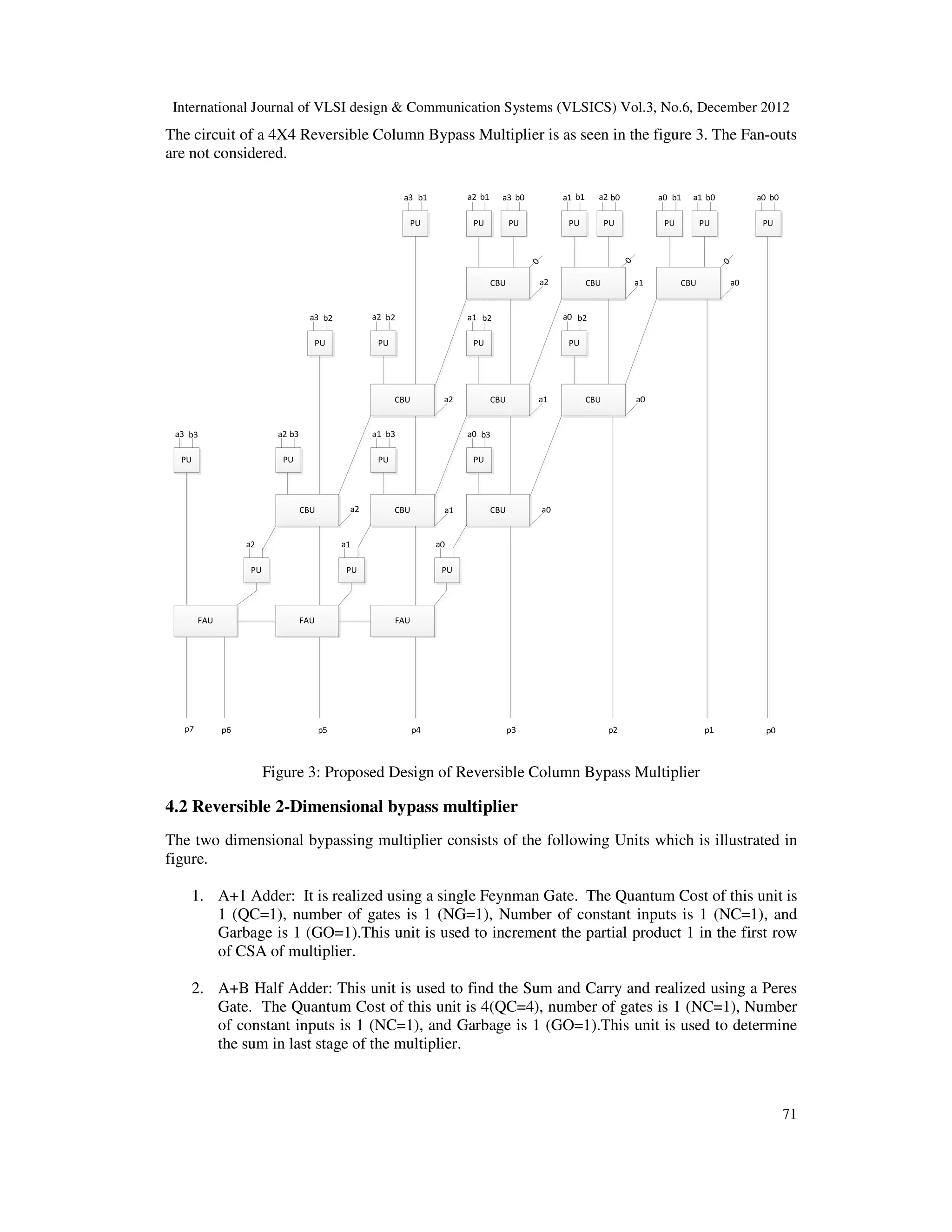

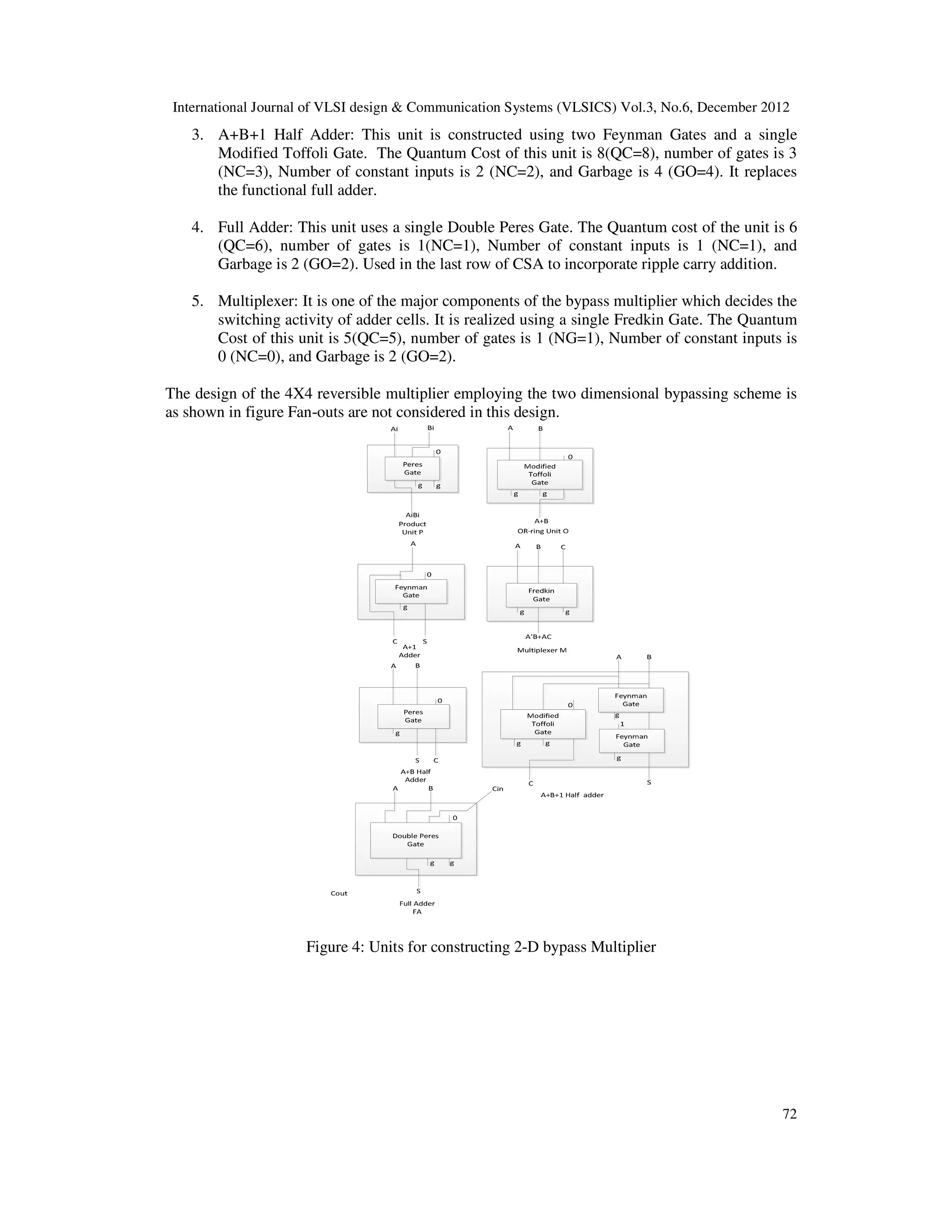

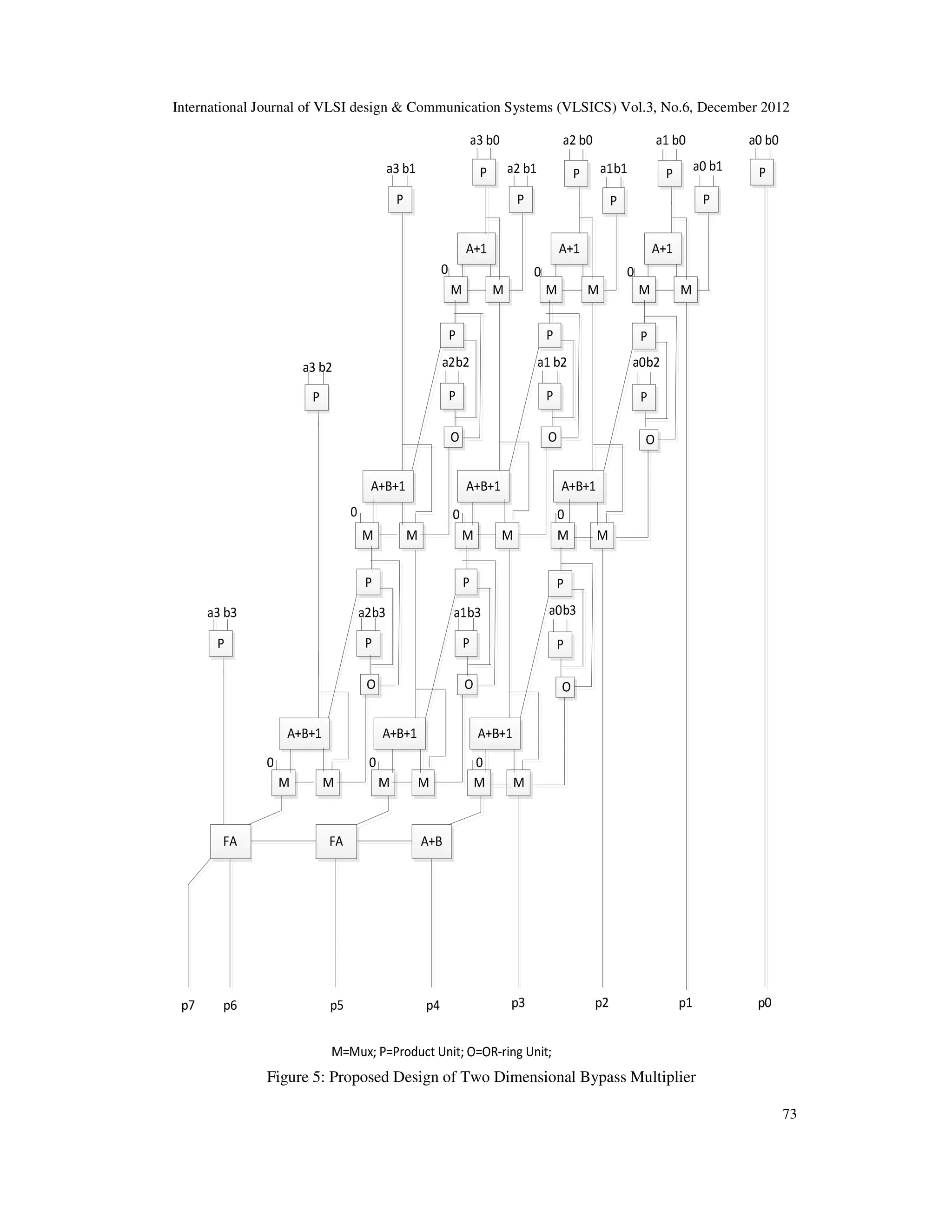

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.6, December 2012 69 There can be Power reduction in a multiplier if bit ai, in the multiplicand is 0 or bit bj, in the multiplier is 0. The addition operations in the (i + 1) th or the jth row can be bypassed if the above conditions are satisfied. Normally, the extra correcting circuits in the row bypassing multiplier are used to add the bypassed carry results to the multiplication result. [6] Proposed two dimensional bypassing multiplier circuit designs in order to eliminate the extra correcting circuits. Here, the carry result in the previous row is integrated in the 2 dimensional bypassing process, which in turn causes the addition operations in the ( i+1, j)Full Adders (FA) to be by passed, if the product, aibj , is 0 and carry bit ci,j-1, is 0. This in turn implies that the addition operation in the (i+1, j) FA will be executed if the product aibj, is 1, or bit ci, j-1, is 1. 2.2. Reversible Logic A Boolean function is reversible if each of the values in the input set can be mapped with a unique value in the output set. A number of reversible logic gates have been proposed till date. The most important and fundamental ones are the Feynman Gate, Fredkin Gate, Peres Gate, Toffoli Gate to name a few. Other gates related to the discussion are the Double Peres Gate [10] and Modified Toffoli Gate [11]. The symbols of all the gates are as shown in the figure1. The inputs and the outputs are named on the respective I/O lines. The quantum cost of Feynman Gate is 1, Fredkin Gate is 5[4], Peres Gate is 4[5], Toffoli Gate is 4[3], Double Peres Gate is 6[10] and that of the Modified Toffoli Gate is 6[11]. Figure 1: Basic Reversible Gates 3. FFT AND BYPASS MULTIPLIERS Vital operation of any Digital signal processor is the FFT computation. When the input sequence length does not match with the filter coefficient size while performing circular convolution, zero padding becomes inevitable. In case of linear filtering using overlap-add or overlap-save methods, it becomes mandatory to pad zeroes to the input sequence as well as the impulse response sequence, so that their block sizes match. Zero padding in time domain is used extensively in practice to compute a heavily interpolated spectra; aliter, when we take DFT of a zero padded signal we get a smoother looking frequency resolution. As already stated in the previous section, the bypass multiplier reduces the power dissipation by avoiding those carry save adders which are unnecessarily being used when the input bit coefficient is zero. To appreciate the bypass technique in the proposed multiplier, consider the following scenario. When linear convolution is performed digitally by fast convolution, a practical difficulty often arises. If the signal has several hundred of samples but an impulse response has less than 50 samples, it would be uneconomical in terms of computing time, storage and above all the power,](https://image.slidesharecdn.com/3612vlsics06-190416121734/75/DESIGN-OF-REVERSIBLE-MULTIPLIERS-FOR-LINEAR-FILTERING-APPLICATIONS-IN-DSP-3-2048.jpg)

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.6, December 2012 Figure 8: Comparison of Column Bypass and 2 The proposed design of column in the literature. Table 2 shows the [9], [13],[14], [15], [16] and [17]. design is better or at most comparable to those in the literature besides having bypass units overhead. A graph showing the comparison of quantum cost of bypass multiplier multipliers listed above is as shown in figure 9. Table 2: Comparison of column bypass multiplier with other multipliers Design Proposed design of Column Bypass Multiplier Design [9] Design [13] Design [14] Design [15] Design [16] Design [17] 6. CONCLUSIONS On the concluding lines, this paper boasts to present the first reversible multiplier that employs a bypassing scheme. Firstly the column bypassing scheme is taken for discussion as it has the advantage that it eliminates the extra correction circuits [7] needed and has a simpler modified full adder as compared to the row 0 50 100 150 200 250 300 Q C G O International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.6, December 2012 : Comparison of Column Bypass and 2 Dimensional Bypass Multipliers' Parameters he proposed design of column multiplier is compared with other reversible multipliers available in the literature. Table 2 shows the comparison of column bypass multiplier with multipliers in [16] and [17].It is evident from the table that the proposed bypass multiplier design is better or at most comparable to those in the literature besides having bypass units A graph showing the comparison of quantum cost of bypass multiplier multipliers listed above is as shown in figure 9. on of column bypass multiplier with other multipliers Quantum Cost Percentage change Proposed design of Column Bypass 193 - 286 -48.18% 244 -26.42% 244 -26.42% 236 -22.27% 234 -21.24% 208 -7.77% On the concluding lines, this paper boasts to present the first reversible multiplier in the literature that employs a bypassing scheme. Firstly the column bypassing scheme is taken for discussion as it has the advantage that it eliminates the extra correction circuits [7] needed and has a simpler modified full adder as compared to the row bypass multiplier. Column Bypass 2 D Bypass N G C I Column Bypass 2 D Bypass International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.6, December 2012 75 Parameters is compared with other reversible multipliers available column bypass multiplier with multipliers in It is evident from the table that the proposed bypass multiplier design is better or at most comparable to those in the literature besides having bypass units A graph showing the comparison of quantum cost of bypass multiplier and other on of column bypass multiplier with other multipliers Percentage change in the literature that employs a bypassing scheme. Firstly the column bypassing scheme is taken for discussion as it has the advantage that it eliminates the extra correction circuits [7] needed and has a simpler Column Bypass 2 D Bypass](https://image.slidesharecdn.com/3612vlsics06-190416121734/75/DESIGN-OF-REVERSIBLE-MULTIPLIERS-FOR-LINEAR-FILTERING-APPLICATIONS-IN-DSP-9-2048.jpg)

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.6, December 2012 Figure 9: Comparison of Quantum Cost of Column Bypass with other multipliers The key variation of the proposed multiplier is the presence of Column Bypassing unit. This unit minimizes the switching activity of the multiplier when the reduced switching activity in turn yields two more appreciable results i.e. power reduction and delay reduction. The power reduction is already accomplished using reversible logic gates. The delay in this multiplier gets reduced which thereby produces the products faster than the normal multipliers. The design has more quantum cost and garbage outputs than some of the already proposed designs which is mainly due to the presence of bypass units that is not present in other multipliers. Next the 2-D bypass multiplier is considered. The 2 includes both row bypassing as well as column bypassing. Thus when the multiplicand has more number of zeros the column bypass unit efficiently reduces the switc the multiplier has more number of zeros the row bypass unit takes the charge of reducing the switching activity, combining effectiveness of both systems. ACKNOWLEDGEMENTS We would like to extend our gratitude to Prof. H R Bha Communication, BMSCE for guiding us. Geetishree Mishra (Asst. Prof) and K S Vasundara Patel (Asst. Prof) BMSCE, for their kind suggestions. We would also like to thank REFERENCES [1] R. Landauer,”Irreversibility and Heat Generation in the Computational Process”, IBM Journal of Research and Development, 5, pp.183 [2] C.H. Bennett, “Logical reversibility of 532, November 1973. [3] T.Toffoli,”Reversible Computing” Tech memo MIT/LCS/TM 1980. [4] E. Fredkin and T. Toffoli,”Conservative Logic”, Int’l J. Theoretical Physics Vo 1982. [5] A. Peres, Reversible logic and quantum computers, Phys. Rev. A 32 (1985) 3266 0 50 100 150 200 250 300 [13] [14] International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.6, December 2012 Figure 9: Comparison of Quantum Cost of Column Bypass with other multipliers The key variation of the proposed multiplier is the presence of Column Bypassing unit. This unit minimizes the switching activity of the multiplier when the binary word has zeros in it. This reduced switching activity in turn yields two more appreciable results i.e. power reduction and delay reduction. The power reduction is already accomplished using reversible logic gates. The reduced which thereby produces the products faster than the normal multipliers. The design has more quantum cost and garbage outputs than some of the already proposed designs which is mainly due to the presence of bypass units that is not present in other D bypass multiplier is considered. The 2-dimensional bypass multiplier includes both row bypassing as well as column bypassing. Thus when the multiplicand has more number of zeros the column bypass unit efficiently reduces the switching activity. Mean while if the multiplier has more number of zeros the row bypass unit takes the charge of reducing the switching activity, combining effectiveness of both systems. We would like to extend our gratitude to Prof. H R Bhagyalakshmi, Dept of Electronics and Communication, BMSCE for guiding us. We would like to thank Kiran Bailey (Asst. Prof), Geetishree Mishra (Asst. Prof) and K S Vasundara Patel (Asst. Prof) BMSCE, for their kind We would also like to thank our parents for all their encouragement. R. Landauer,”Irreversibility and Heat Generation in the Computational Process”, IBM Journal of Research and Development, 5, pp.183-191, 1961. C.H. Bennett, “Logical reversibility of Computation”, IBM J. Research and Development, pp.525 T.Toffoli,”Reversible Computing” Tech memo MIT/LCS/TM-151, MIT Lab for Computer Science E. Fredkin and T. Toffoli,”Conservative Logic”, Int’l J. Theoretical Physics Vol 21, pp.219 A. Peres, Reversible logic and quantum computers, Phys. Rev. A 32 (1985) 3266–3276. [15] [16] [17] QC of other designs QC of Proposed Design International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.6, December 2012 76 Figure 9: Comparison of Quantum Cost of Column Bypass with other multipliers The key variation of the proposed multiplier is the presence of Column Bypassing unit. This unit binary word has zeros in it. This reduced switching activity in turn yields two more appreciable results i.e. power reduction and delay reduction. The power reduction is already accomplished using reversible logic gates. The reduced which thereby produces the products faster than the normal multipliers. The design has more quantum cost and garbage outputs than some of the already proposed designs which is mainly due to the presence of bypass units that is not present in other dimensional bypass multiplier includes both row bypassing as well as column bypassing. Thus when the multiplicand has more hing activity. Mean while if the multiplier has more number of zeros the row bypass unit takes the charge of reducing the gyalakshmi, Dept of Electronics and We would like to thank Kiran Bailey (Asst. Prof), Geetishree Mishra (Asst. Prof) and K S Vasundara Patel (Asst. Prof) BMSCE, for their kind R. Landauer,”Irreversibility and Heat Generation in the Computational Process”, IBM Journal of Computation”, IBM J. Research and Development, pp.525- 151, MIT Lab for Computer Science l 21, pp.219-253, 3276. QC of other designs QC of Proposed Design](https://image.slidesharecdn.com/3612vlsics06-190416121734/75/DESIGN-OF-REVERSIBLE-MULTIPLIERS-FOR-LINEAR-FILTERING-APPLICATIONS-IN-DSP-10-2048.jpg)

![International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.6, December 2012 77 [6] Alvin Joseph J. Tang and Joy Alinda Reyes “Comparative Analysis of Low Power Multiplier Architectures” 2011 Fifth Asia Modelling Symposium. [7] Jin-Tai Yan and Zhi-Wei Chen “Low-Power Multiplier Design with Row and Column Bypassing”, 2009 IEEE. [8] Tushar V. More Dr.R.V.Kshirsagar, “Design of Low Power Column Bypass Multiplier using FPGA”, 2011 IEEE. [9] H. Thapliyal, M.B. Srinivas, Novel reversible multiplier architecture using reversible TSG gate, Proceedings of the IEEE International Conference on Computer Systems and Applications, 2006, pp. 100–103. [10] H R Bhagyalakshmi and M.K. Venkatesha “An improved design of multiplirs using reversible logic gates” IJEST Vol. 2(8) 2010. [11] H Thapliyal and A Vinod, Design of Reversible Sequential Elements with Feasibility of Transistor Implementation, IEEE ISCAS 2007. [12] V.G. Moshnyaga and K. Tamaru, “The comparitivestude of switching activity resuction techniques for design of low power multipliers”, IEEE ISCAS 1995. [13] Shams, M., M. Haghparast and K. Navi, 2008. Novel reversible multiplier circuit in nanotechnology. World Appl. Sci. J., 3(5): 806-810. [14] Somayeh Babazadeh and Majid Haghparast, “Design of a Nanometric Fault Tolerant Reversible Multiplier Circuit” Journal of Basic and Applied Scientific Research, 2012. [15] Thapliyal, H., M.B. Srinivas and H.R. Arabnia, 2005, A Reversible Version of 4×4 Bit Array Multiplier with Minimum Gates and Garbage Outputs, Int. Conf. Embedded System, Applications (ESA‟05), Las Vegas, USA, pp: 106 114. [16] H. Thapliyal and M.B. Srinivas, “Novel Reversible Multiplier Architecture Using Reversible TSG Gate”, Proc. IEEE International Conference on Computer Systems and Applications, pp. 100-103, March 20 06. [17] M. Haghparast et al., “Design of a Novel Reversible Multiplier Circuit using HNG Gate in Nanotechnology,” in World Applied Science Journal, Vol. 3, No. 6, pp. 974-978, 2008.](https://image.slidesharecdn.com/3612vlsics06-190416121734/75/DESIGN-OF-REVERSIBLE-MULTIPLIERS-FOR-LINEAR-FILTERING-APPLICATIONS-IN-DSP-11-2048.jpg)