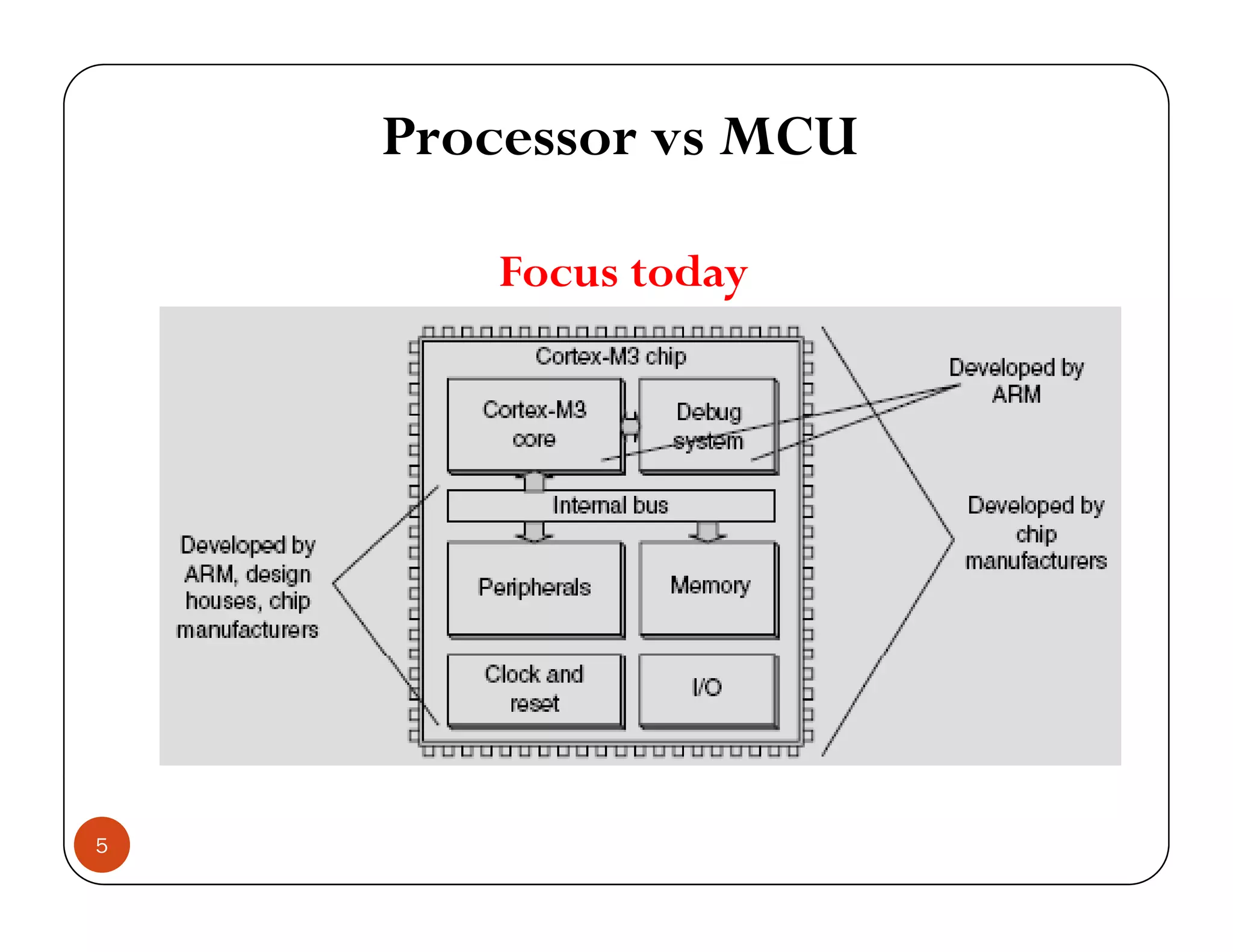

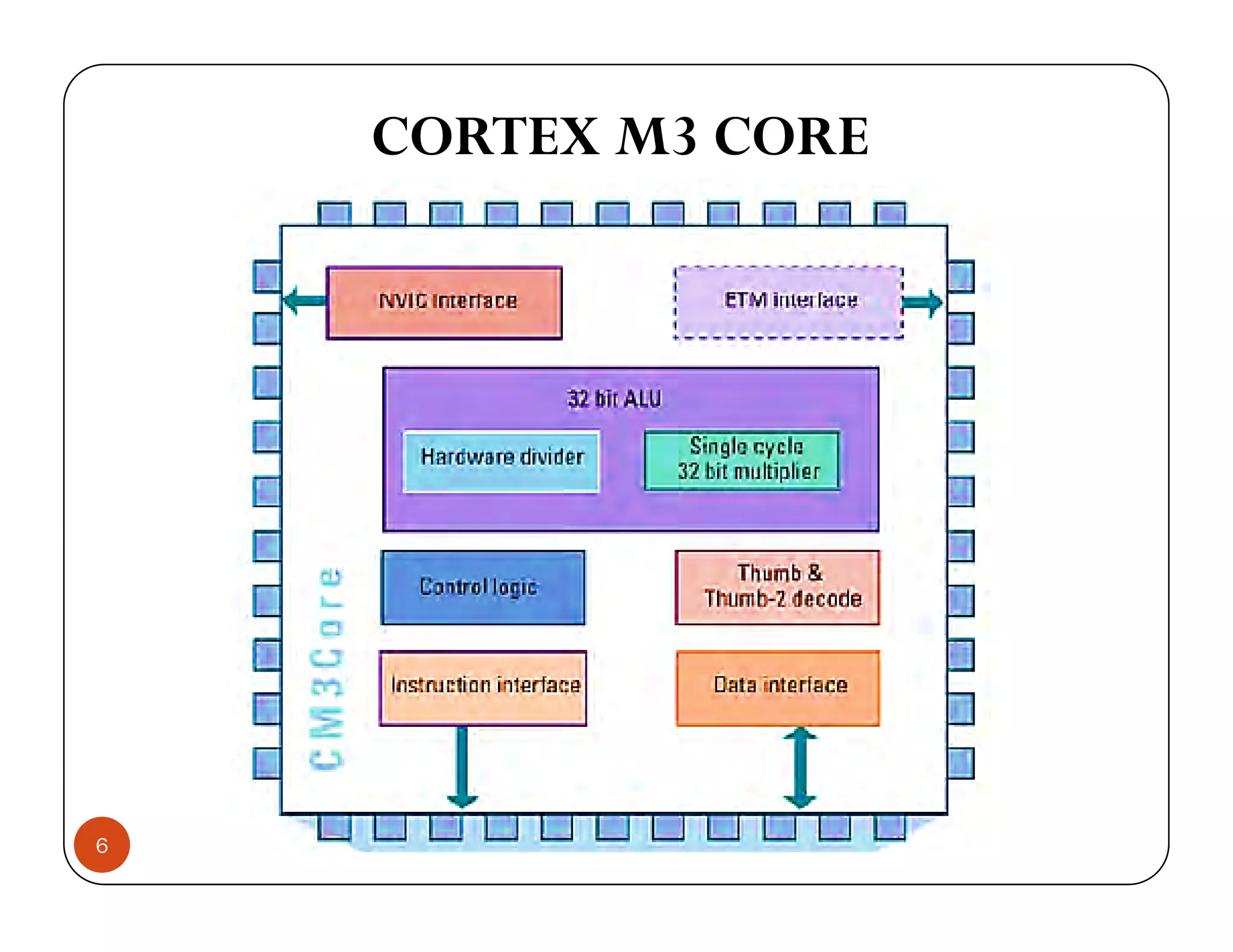

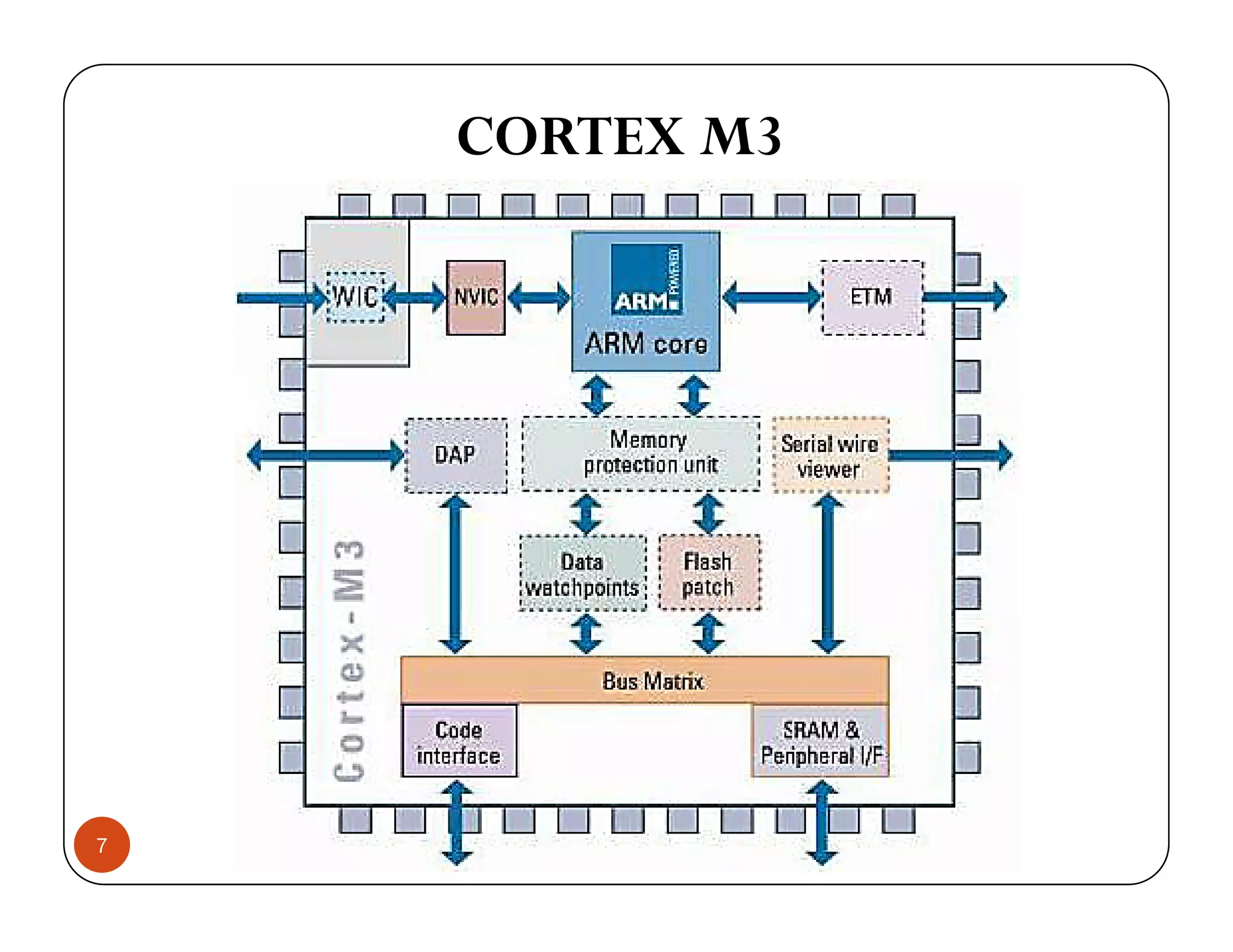

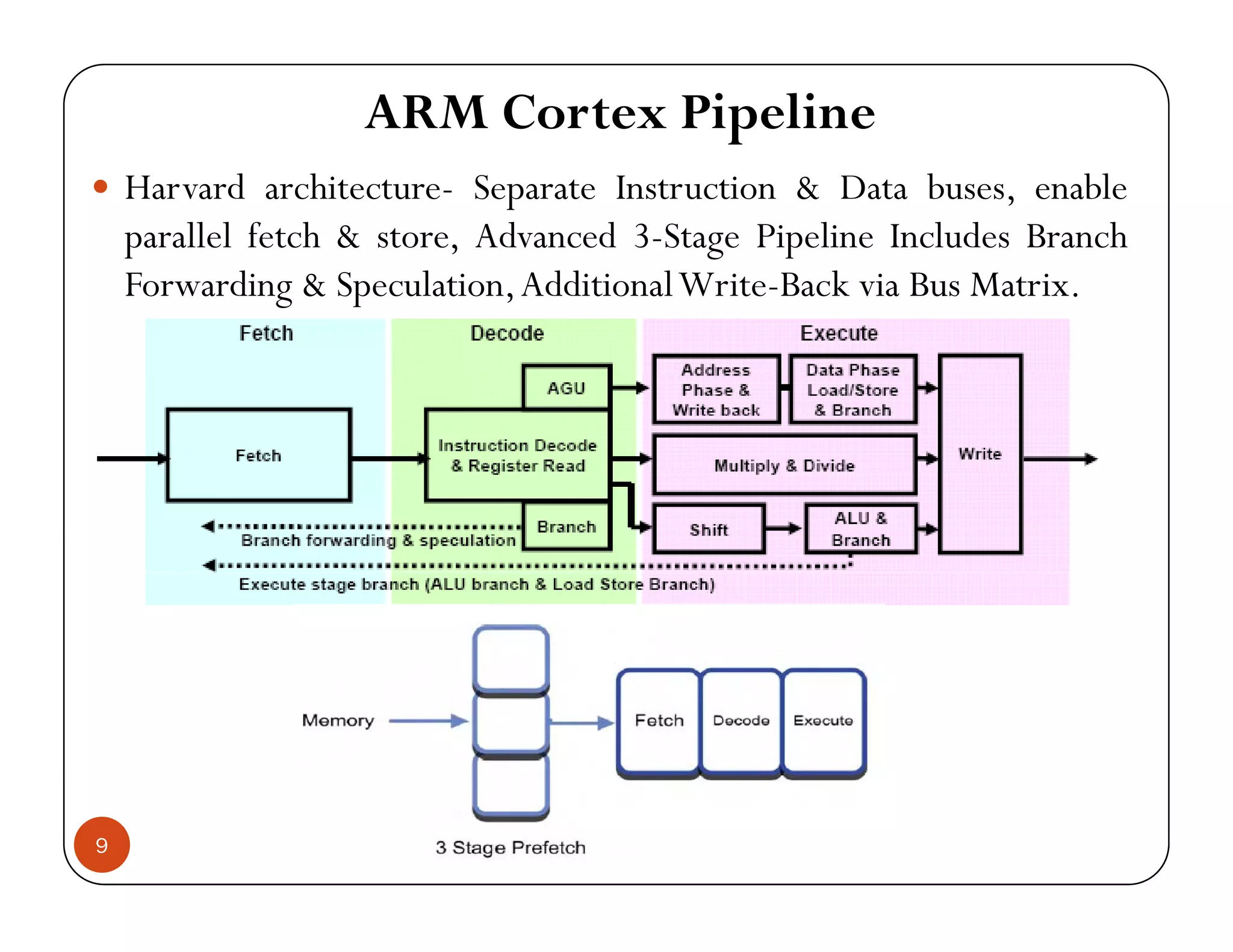

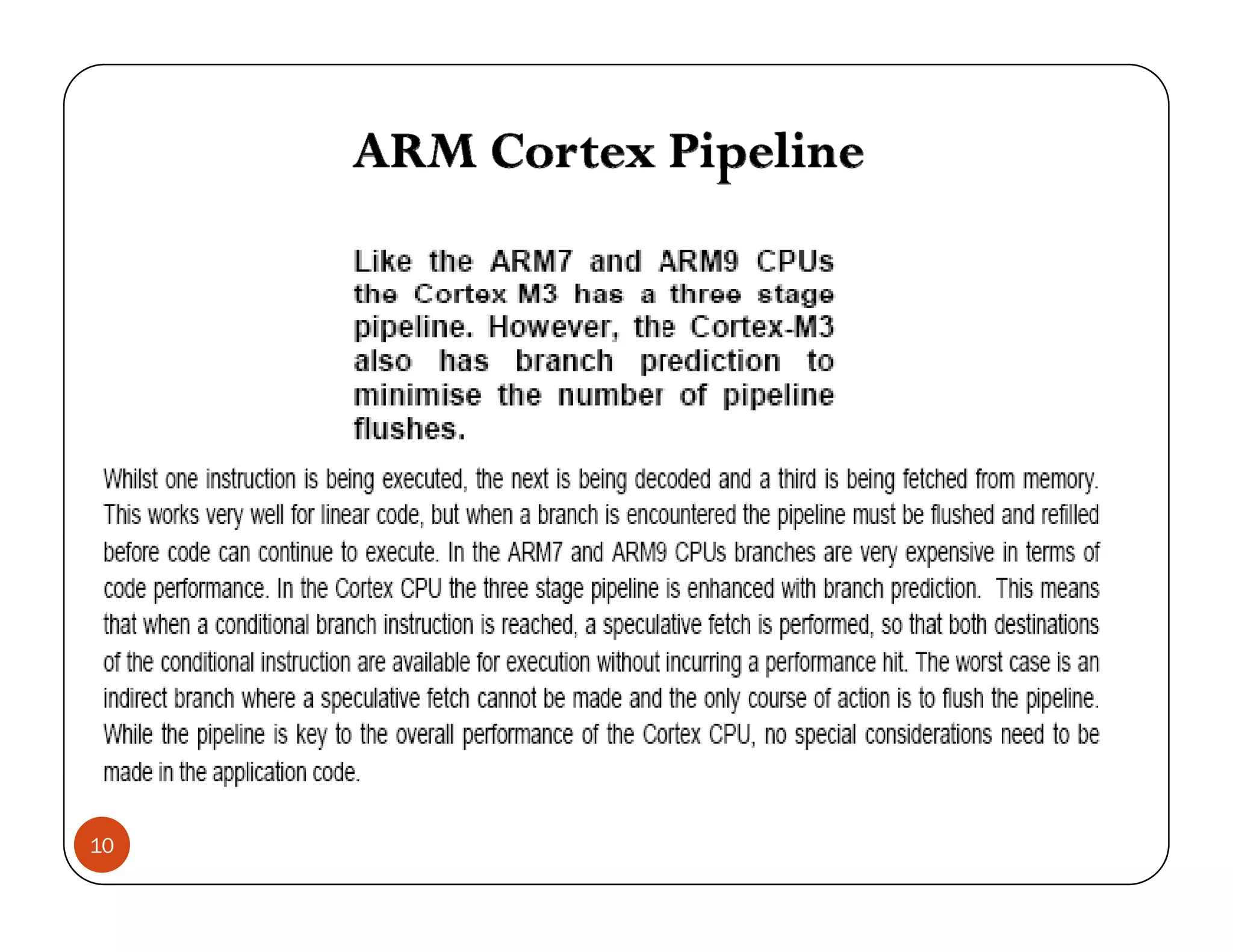

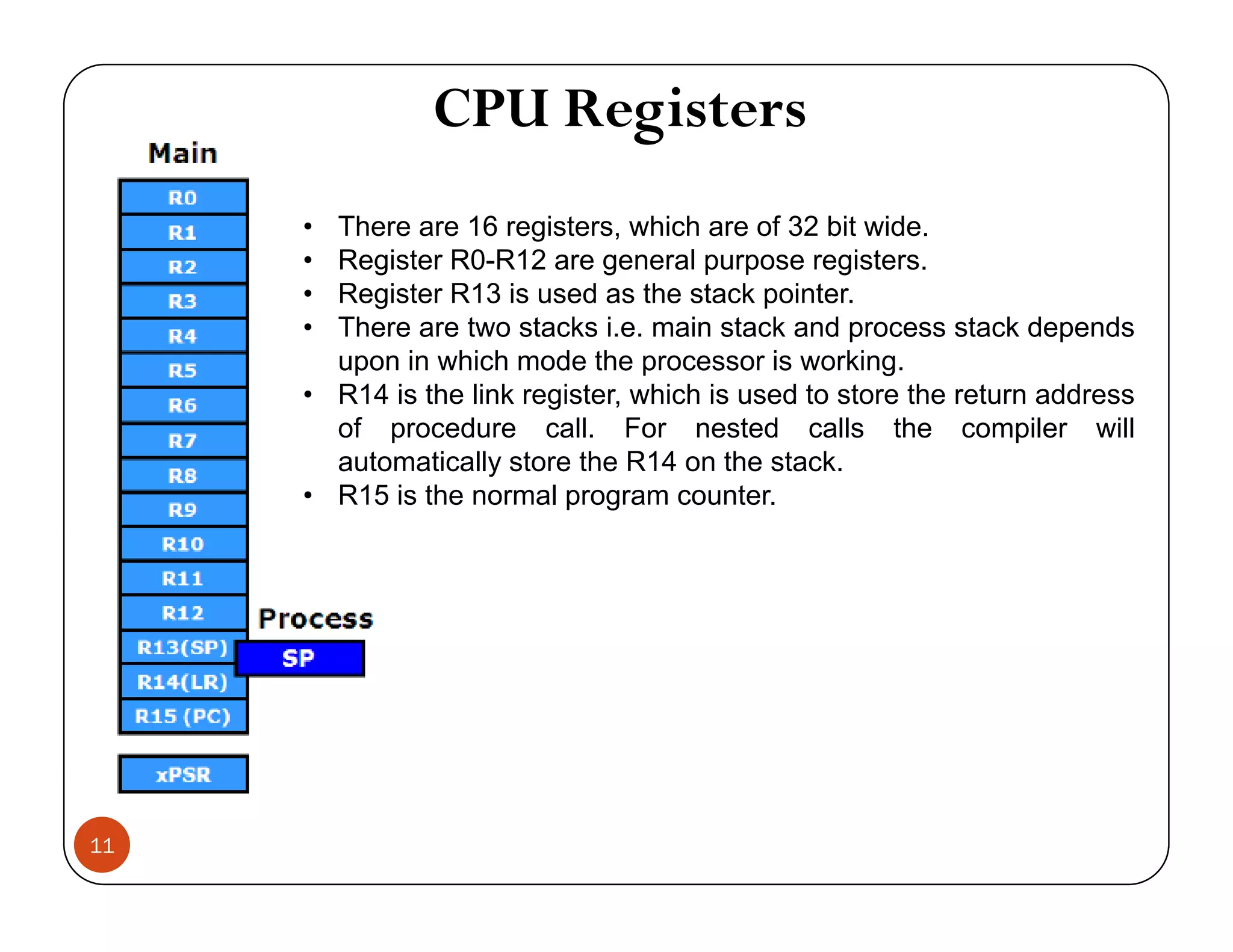

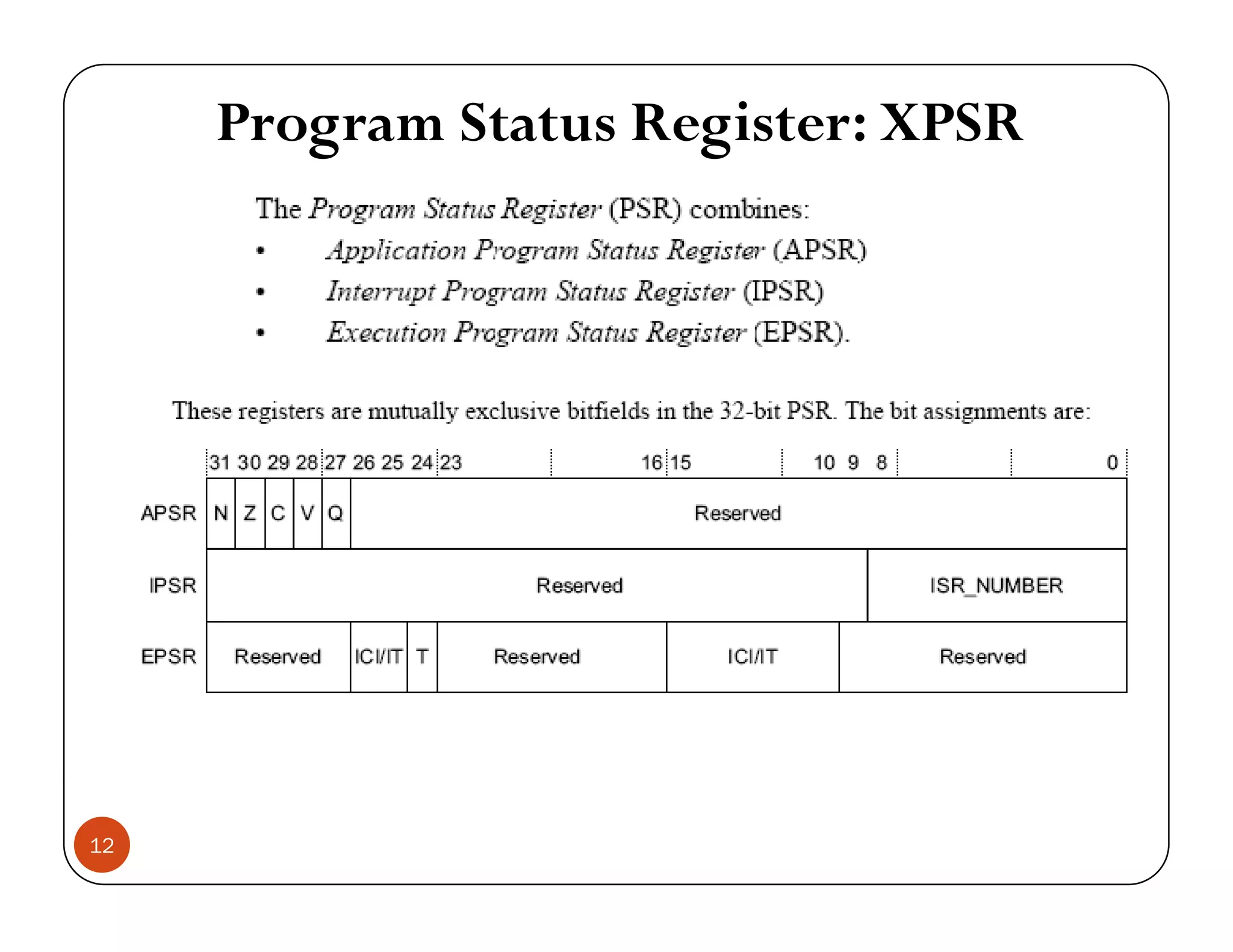

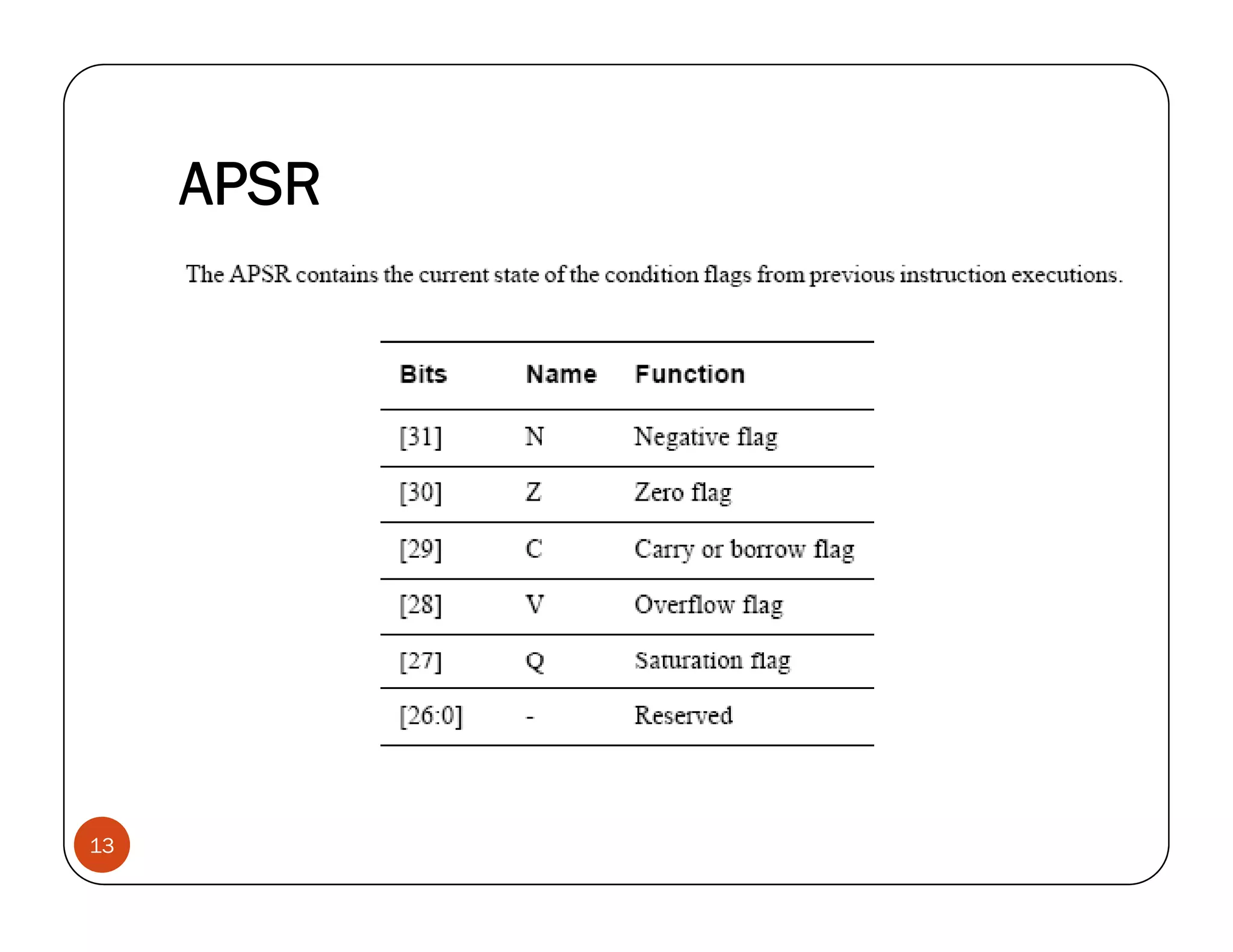

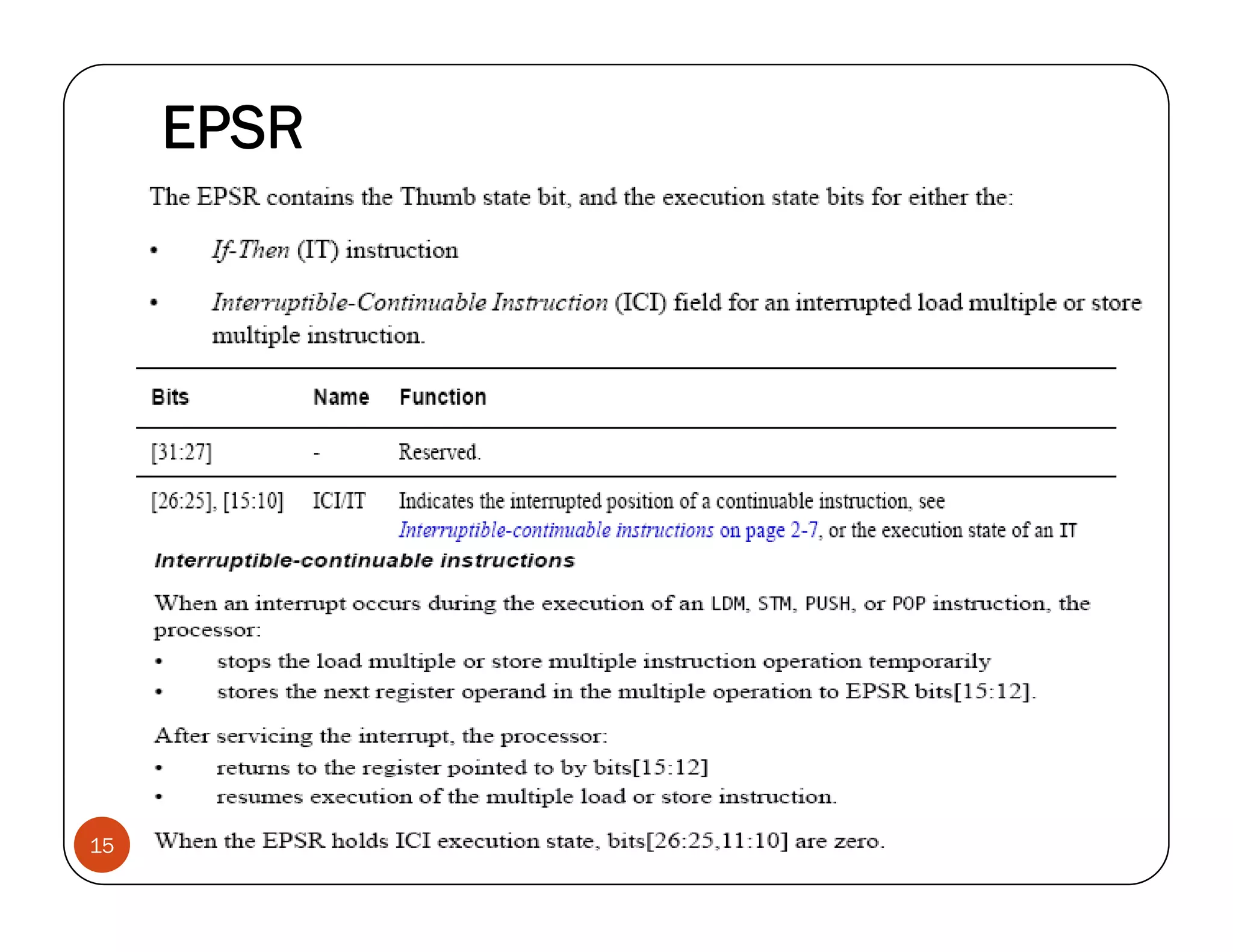

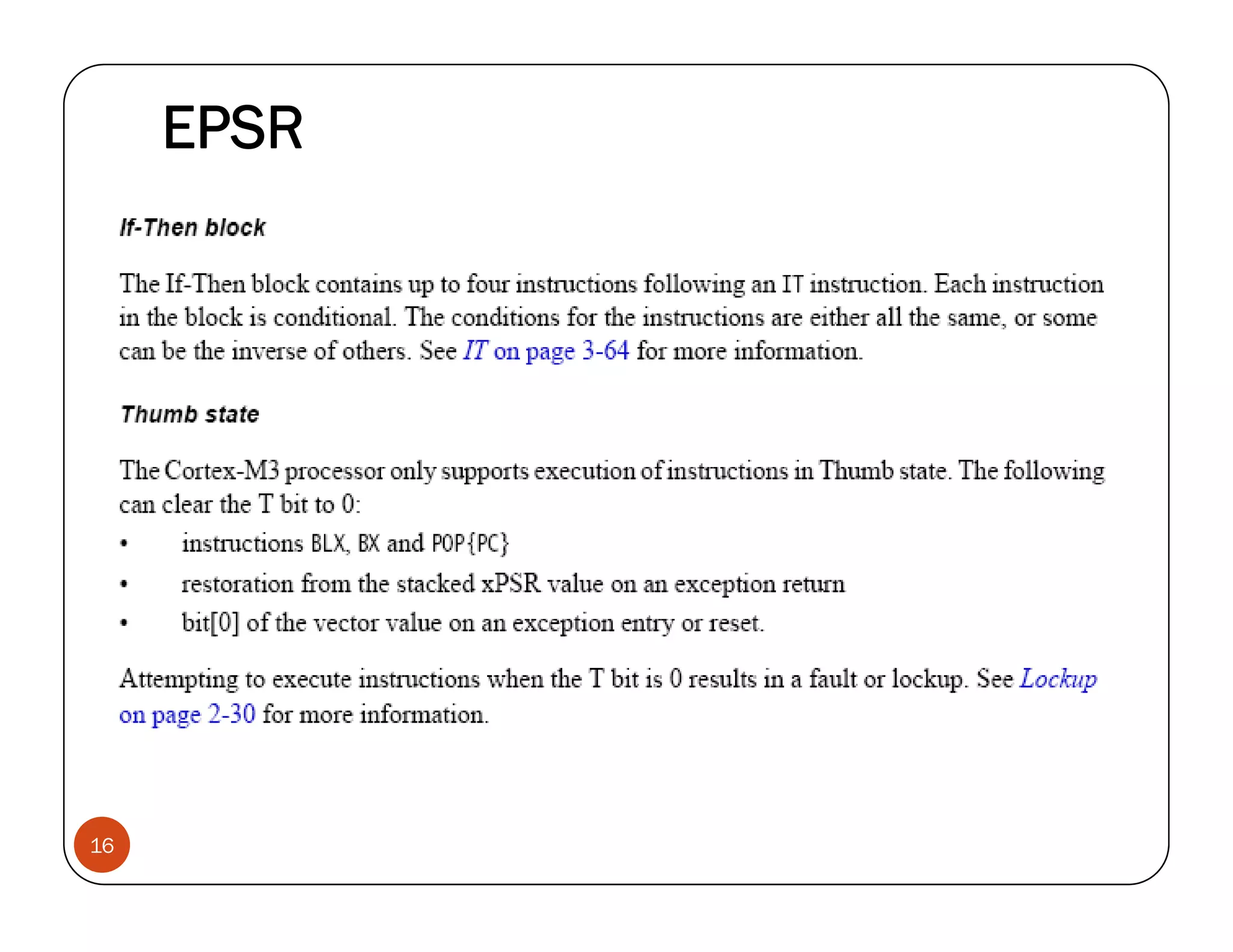

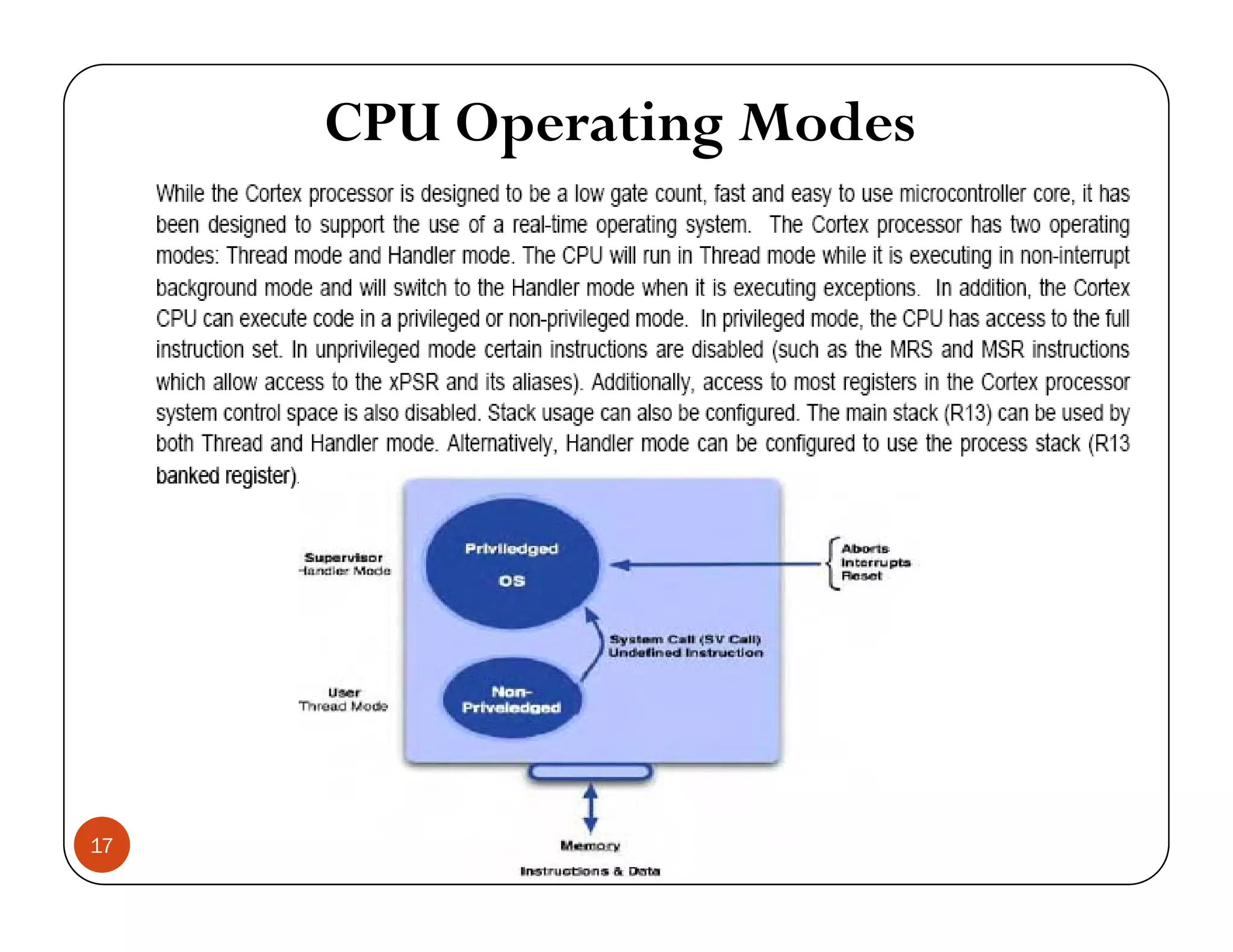

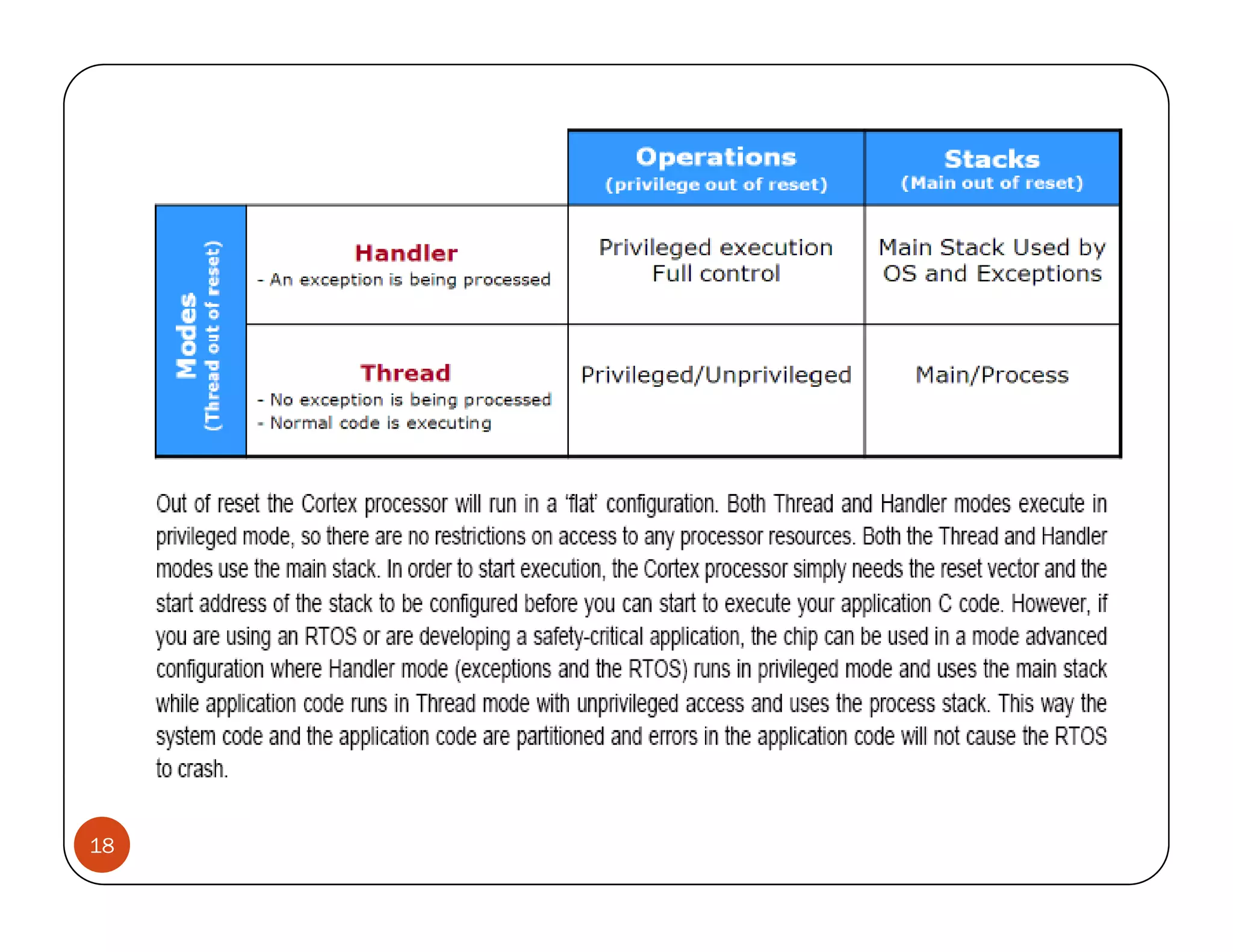

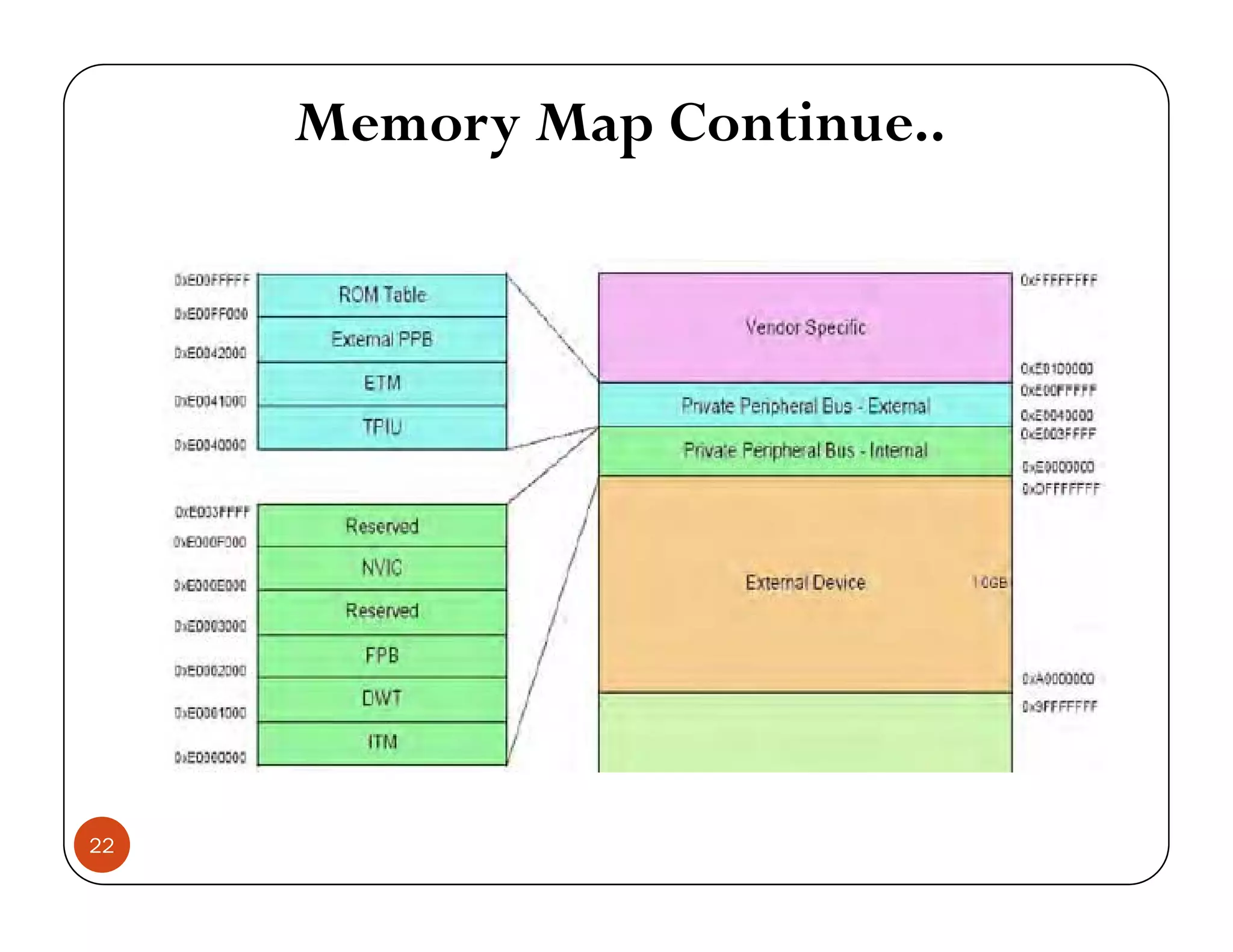

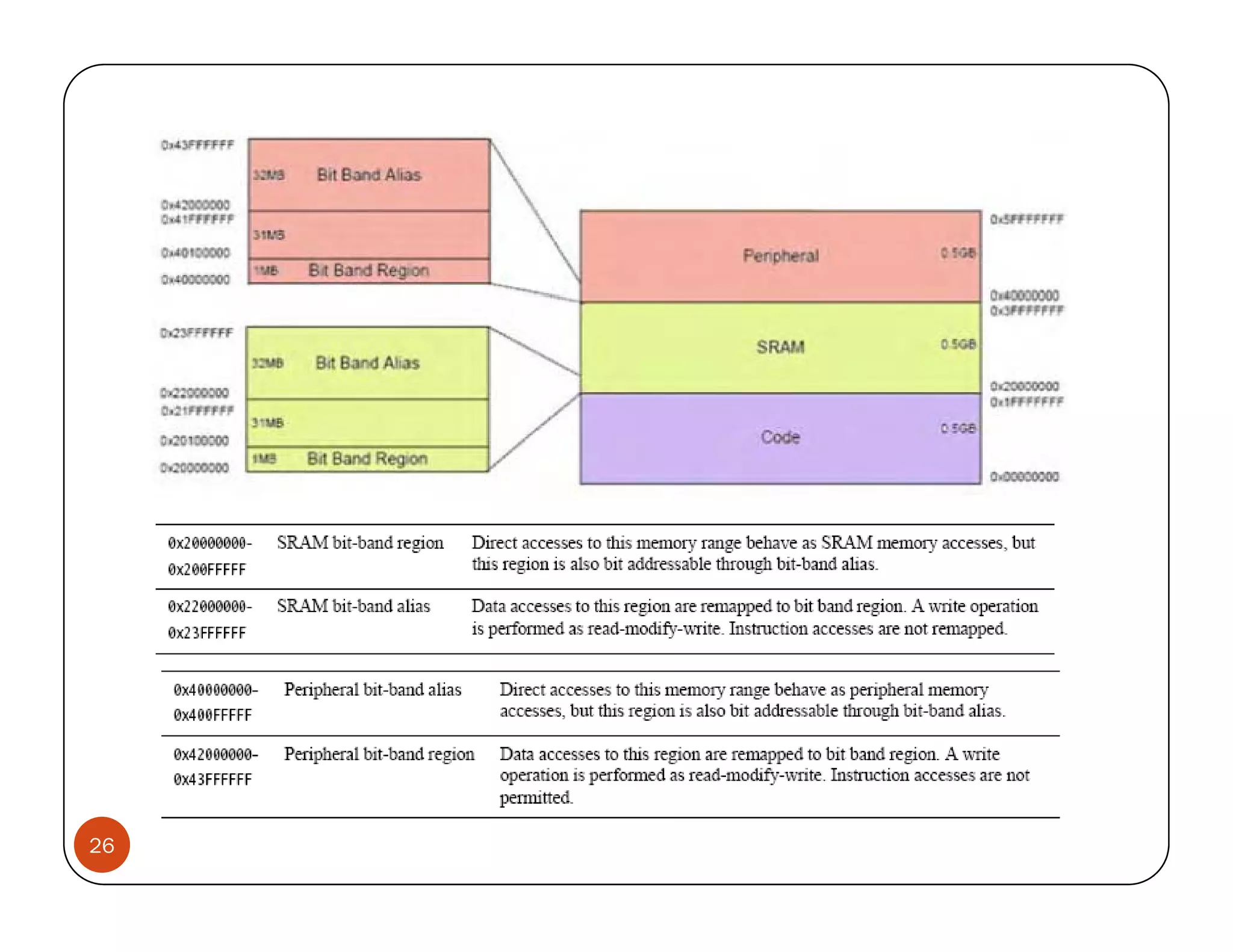

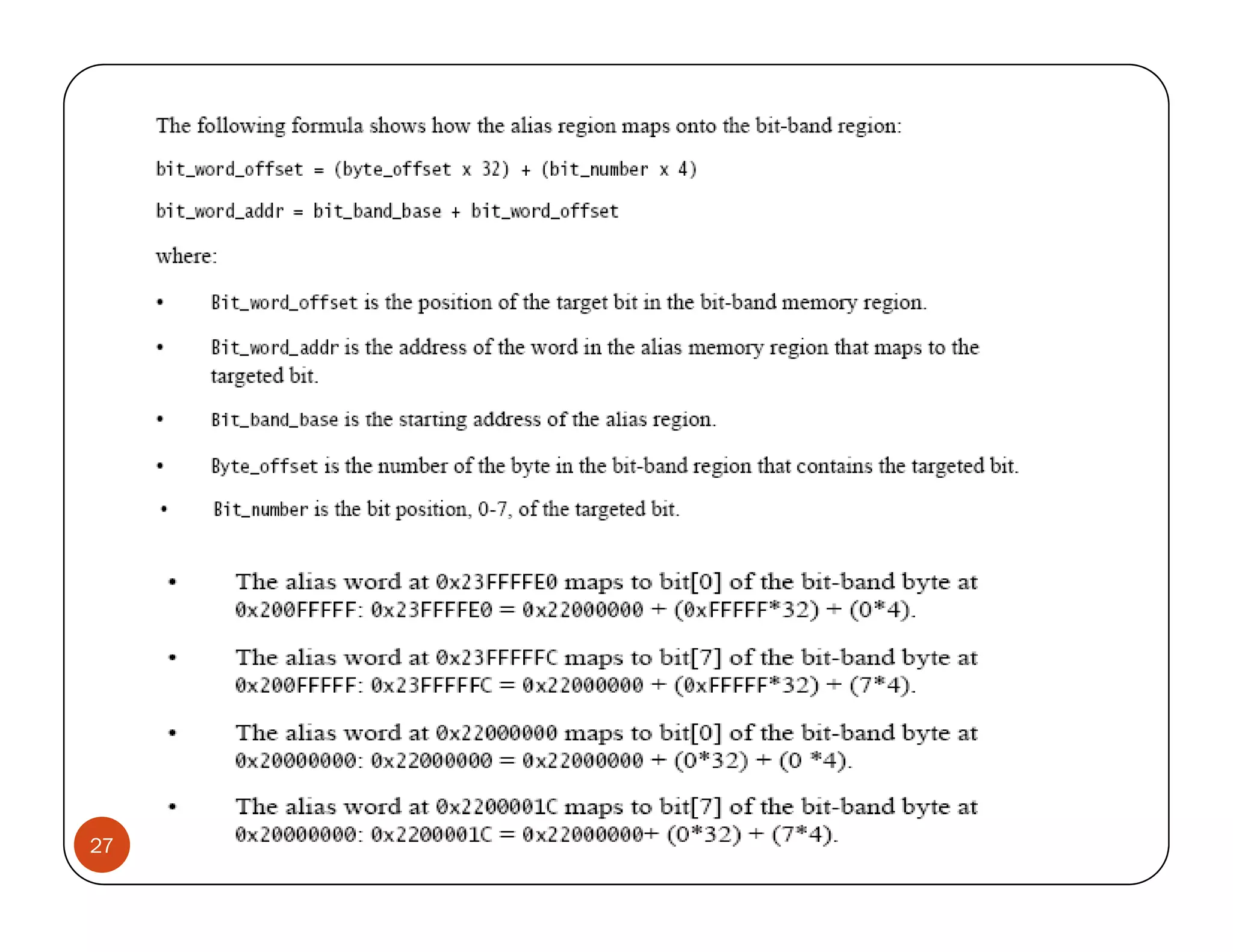

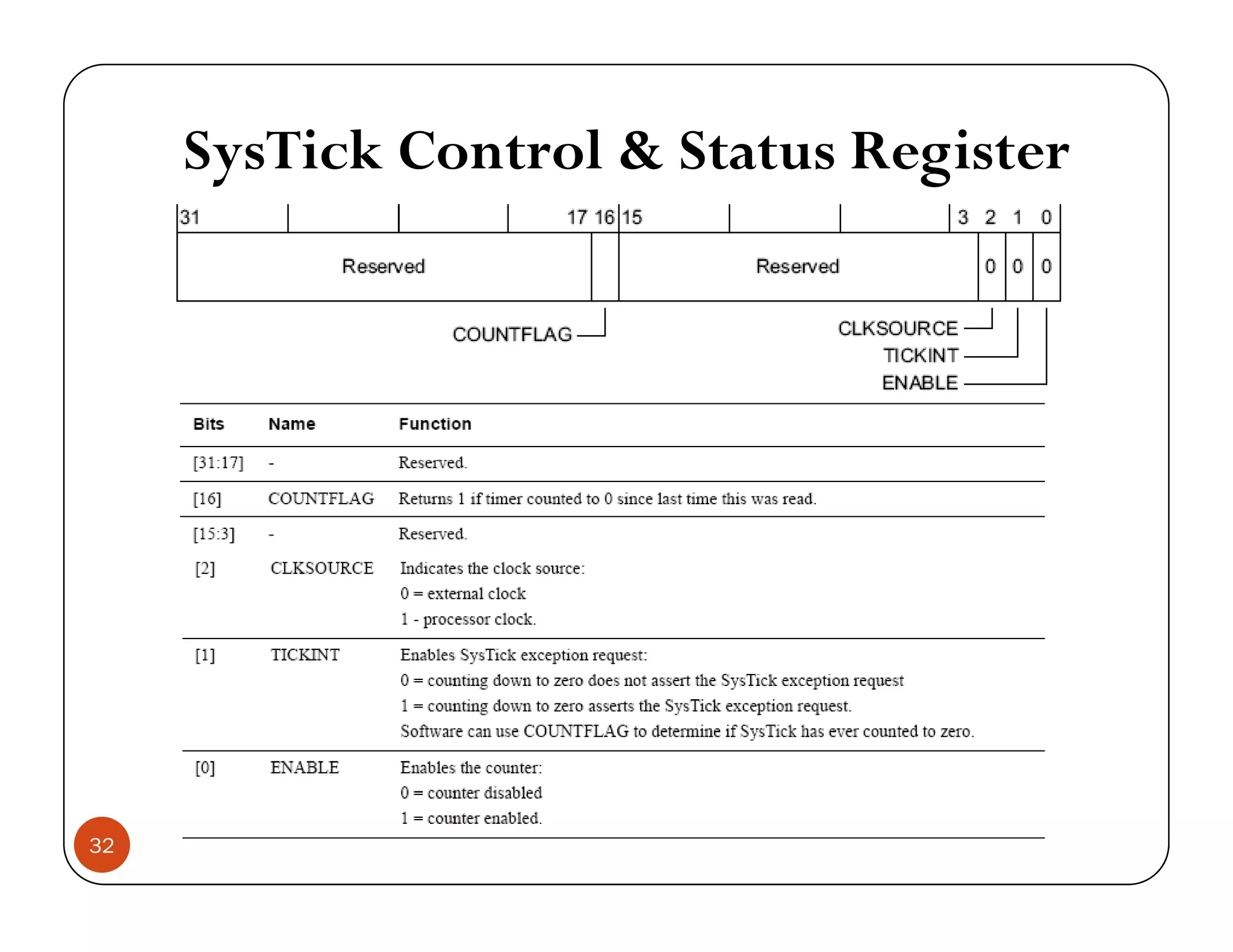

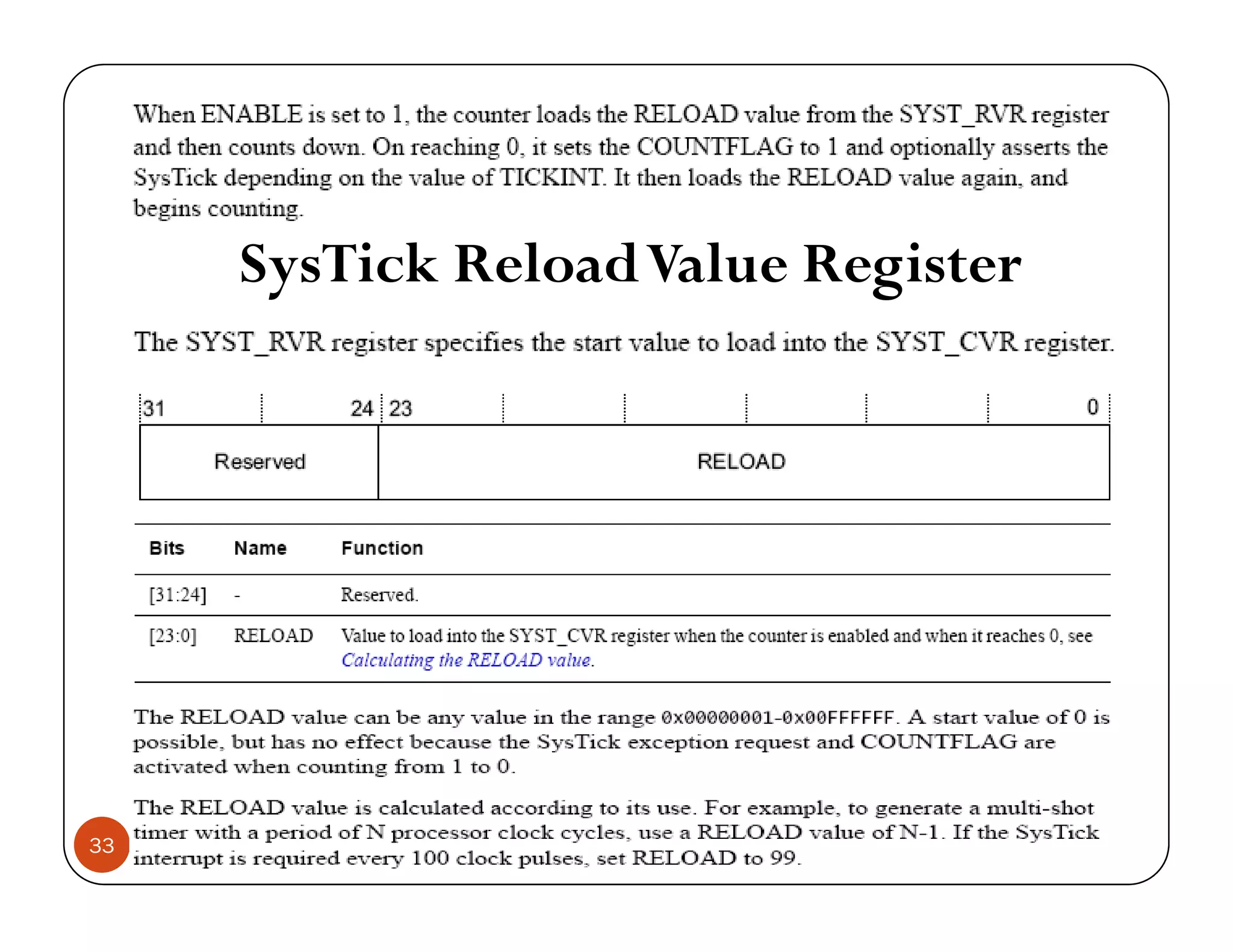

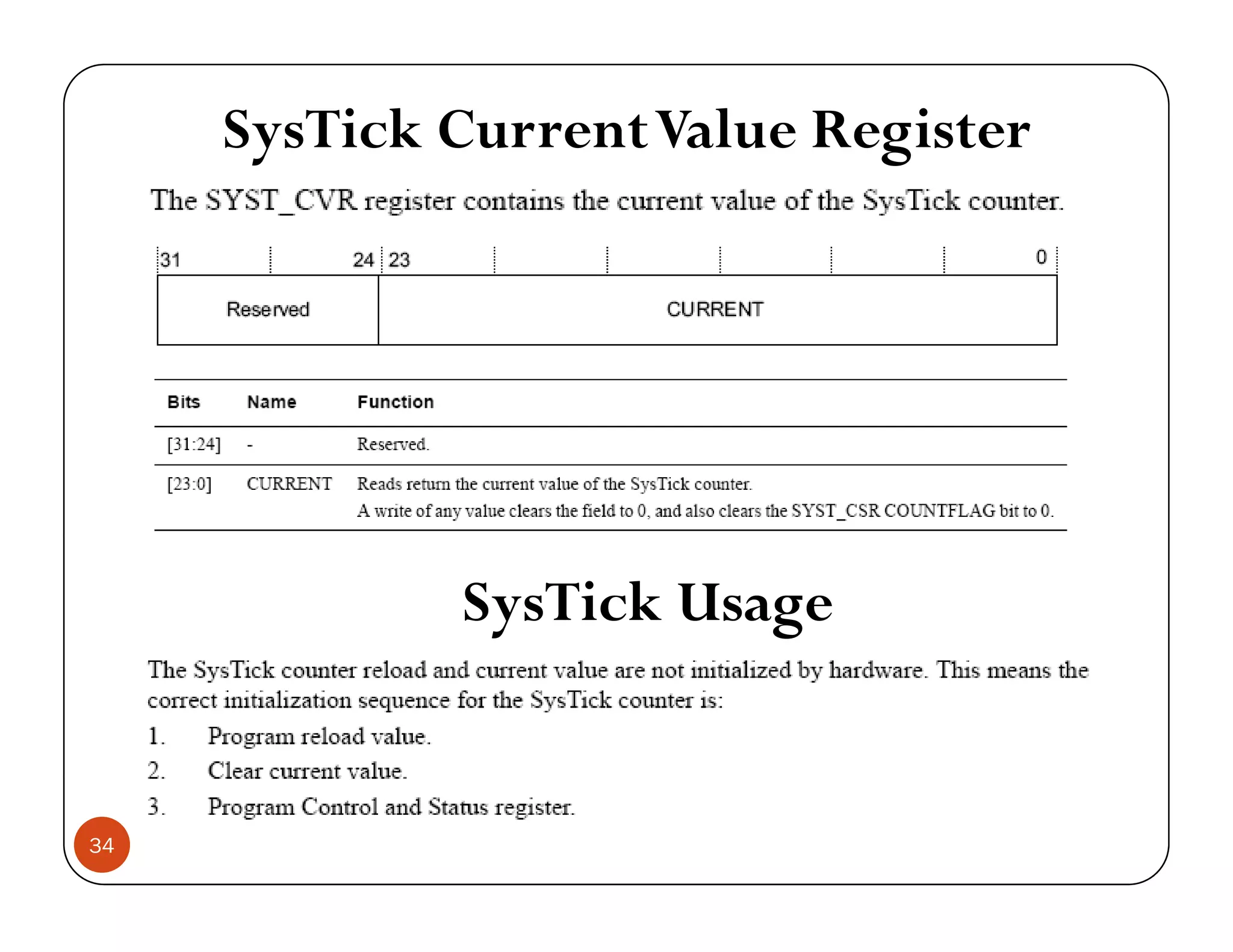

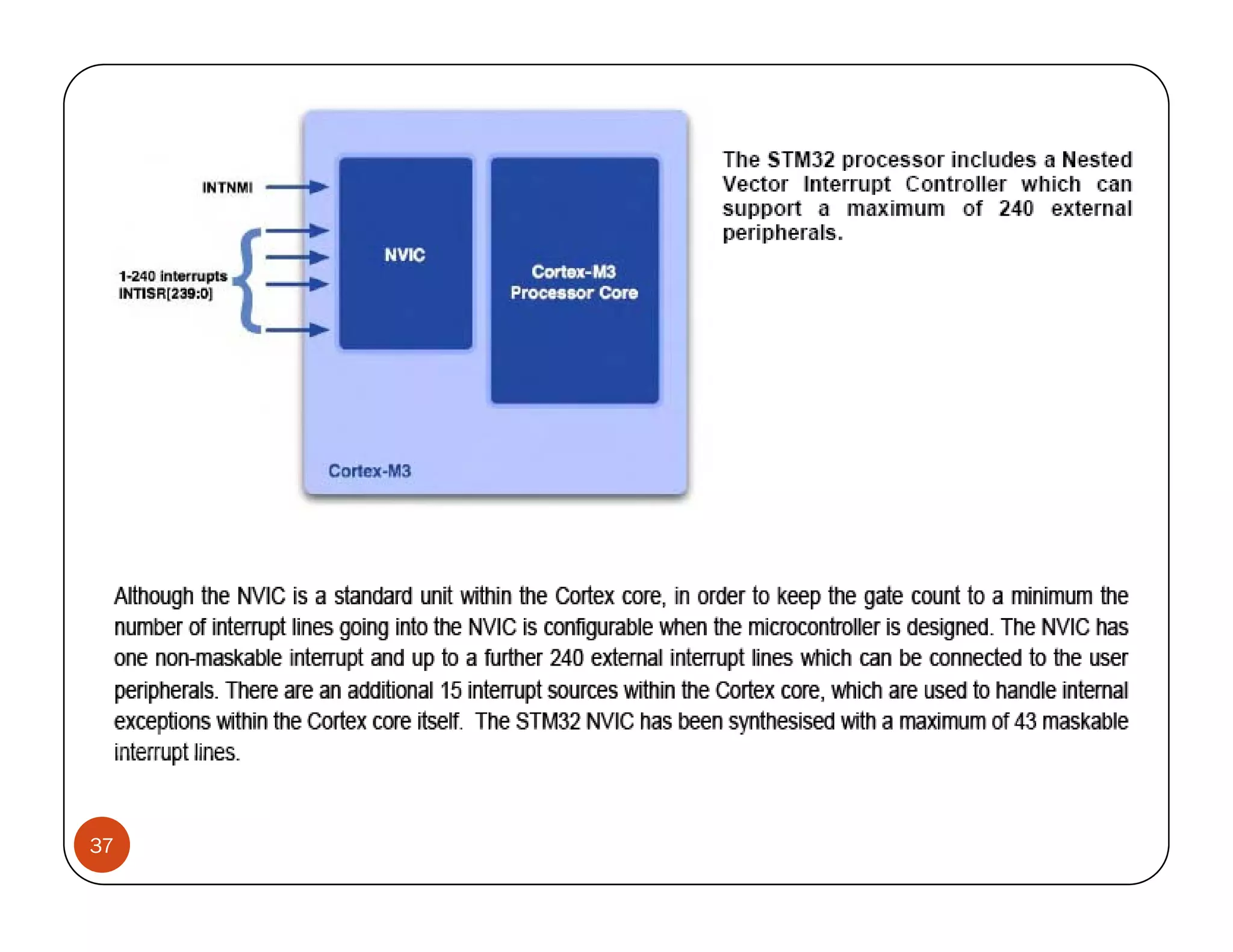

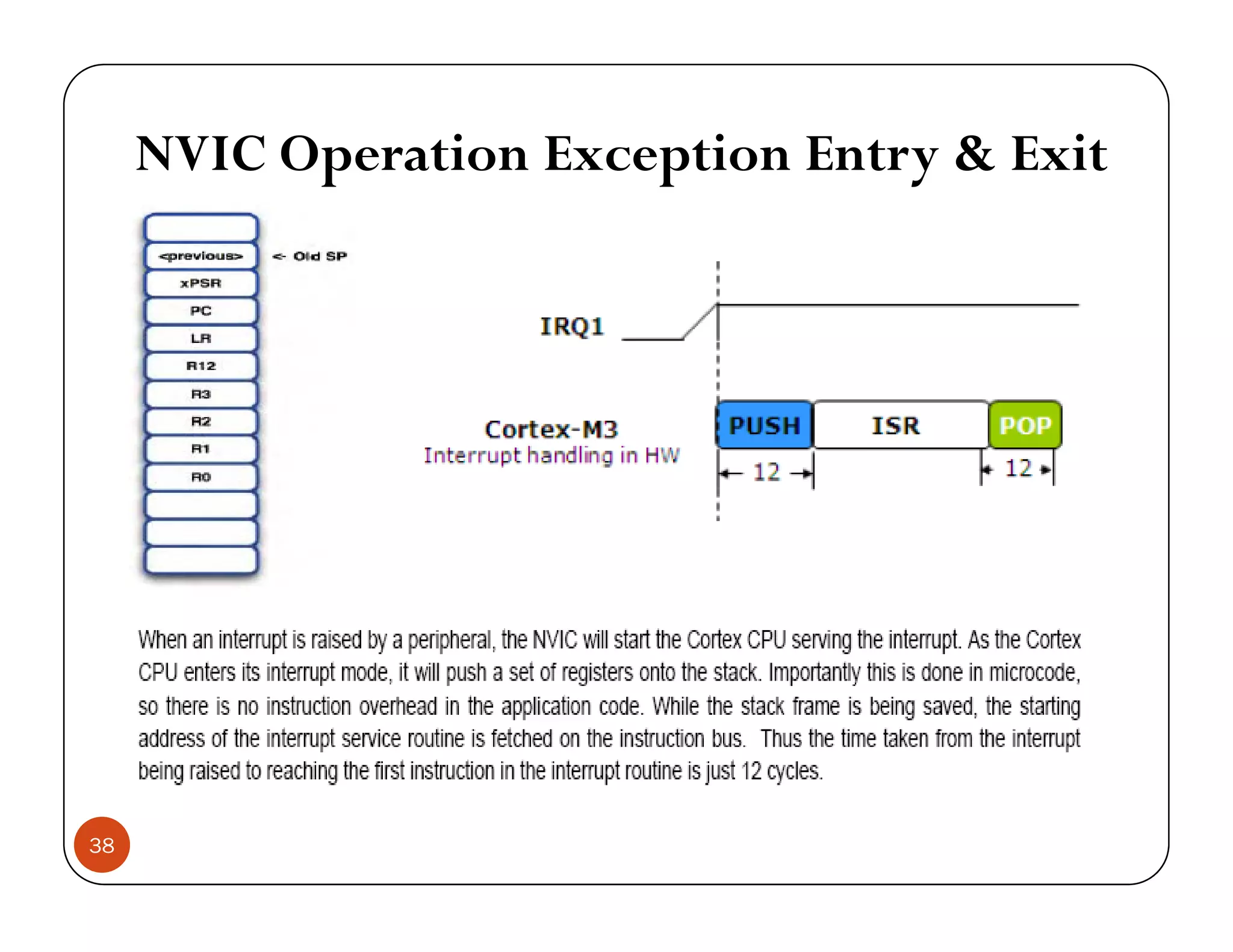

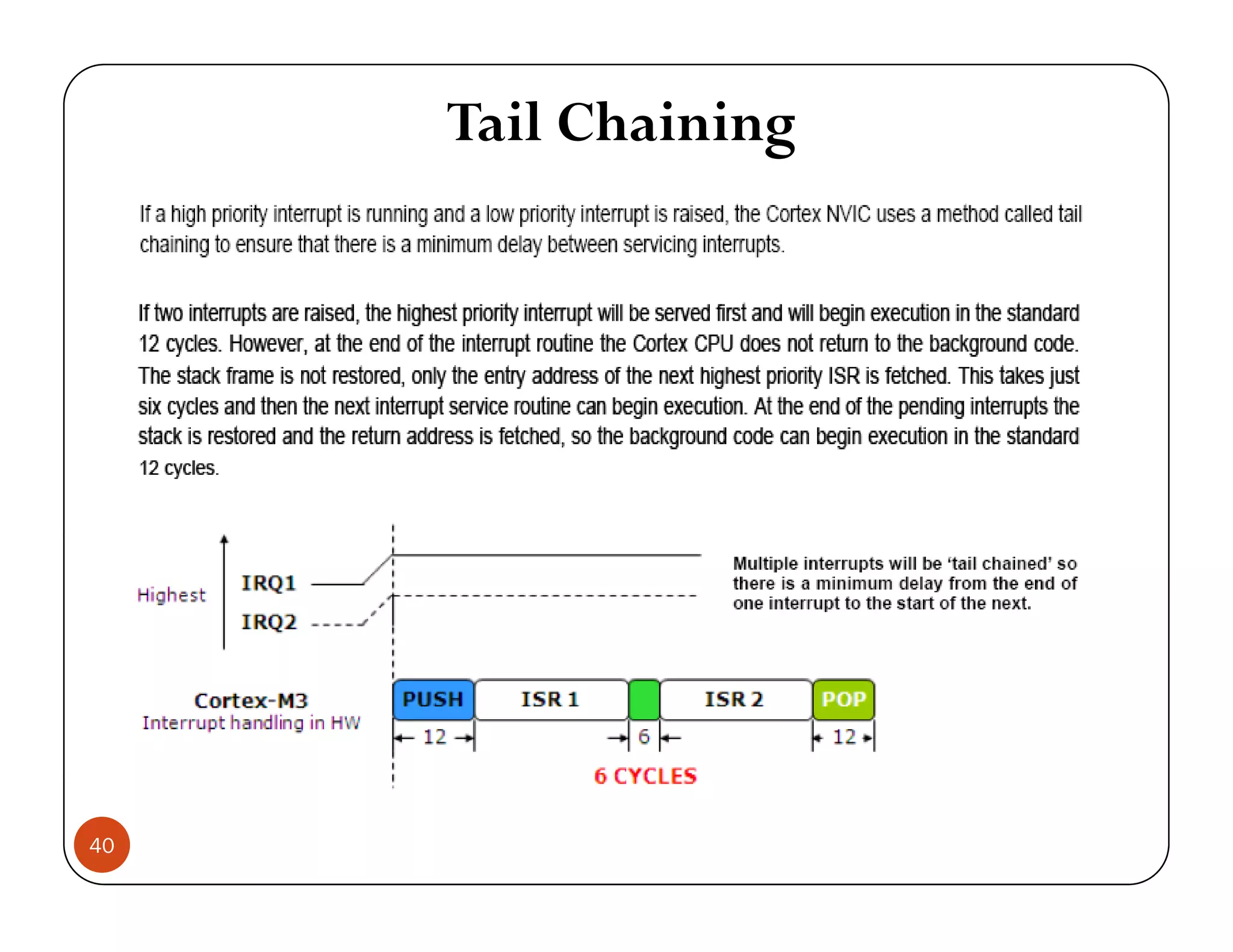

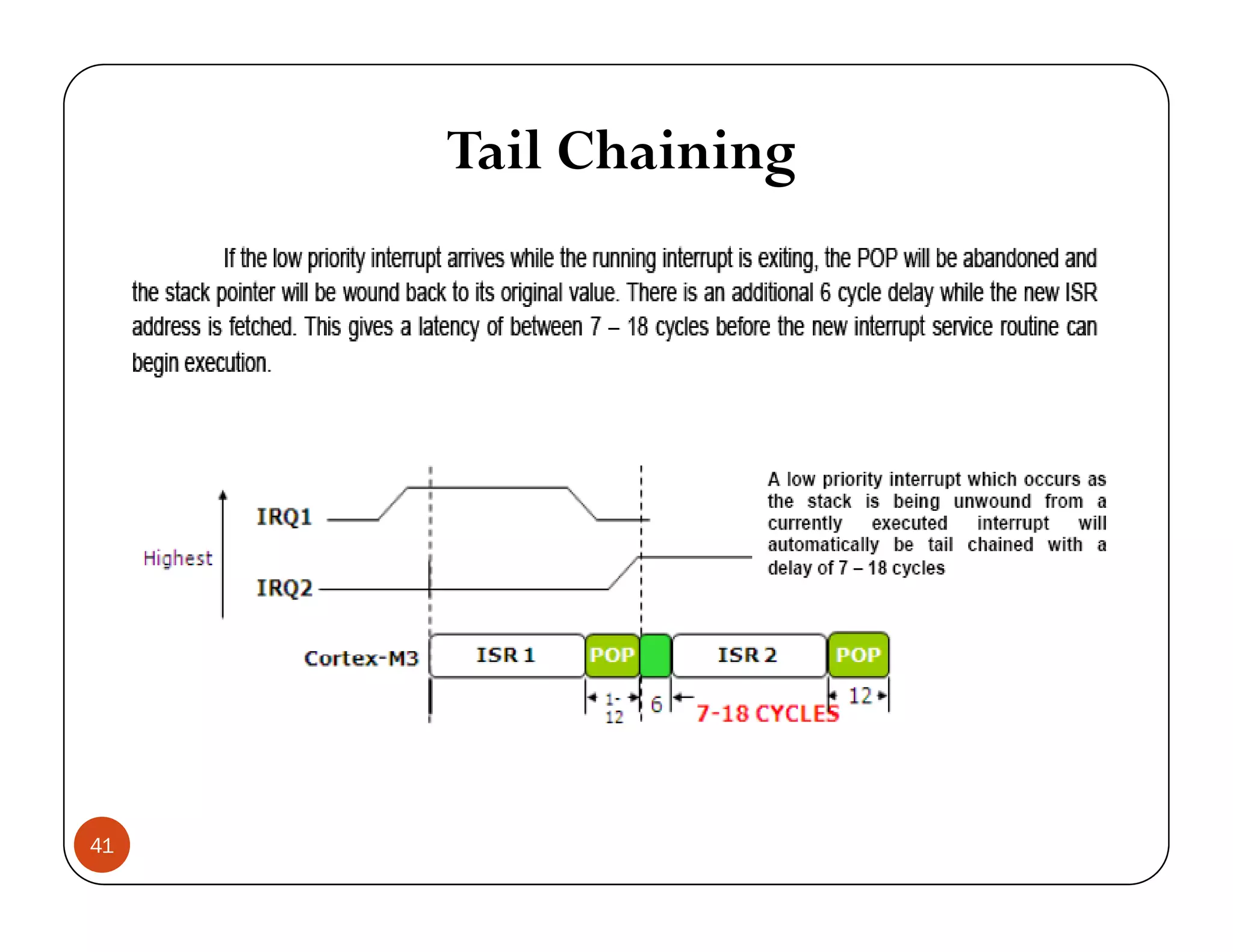

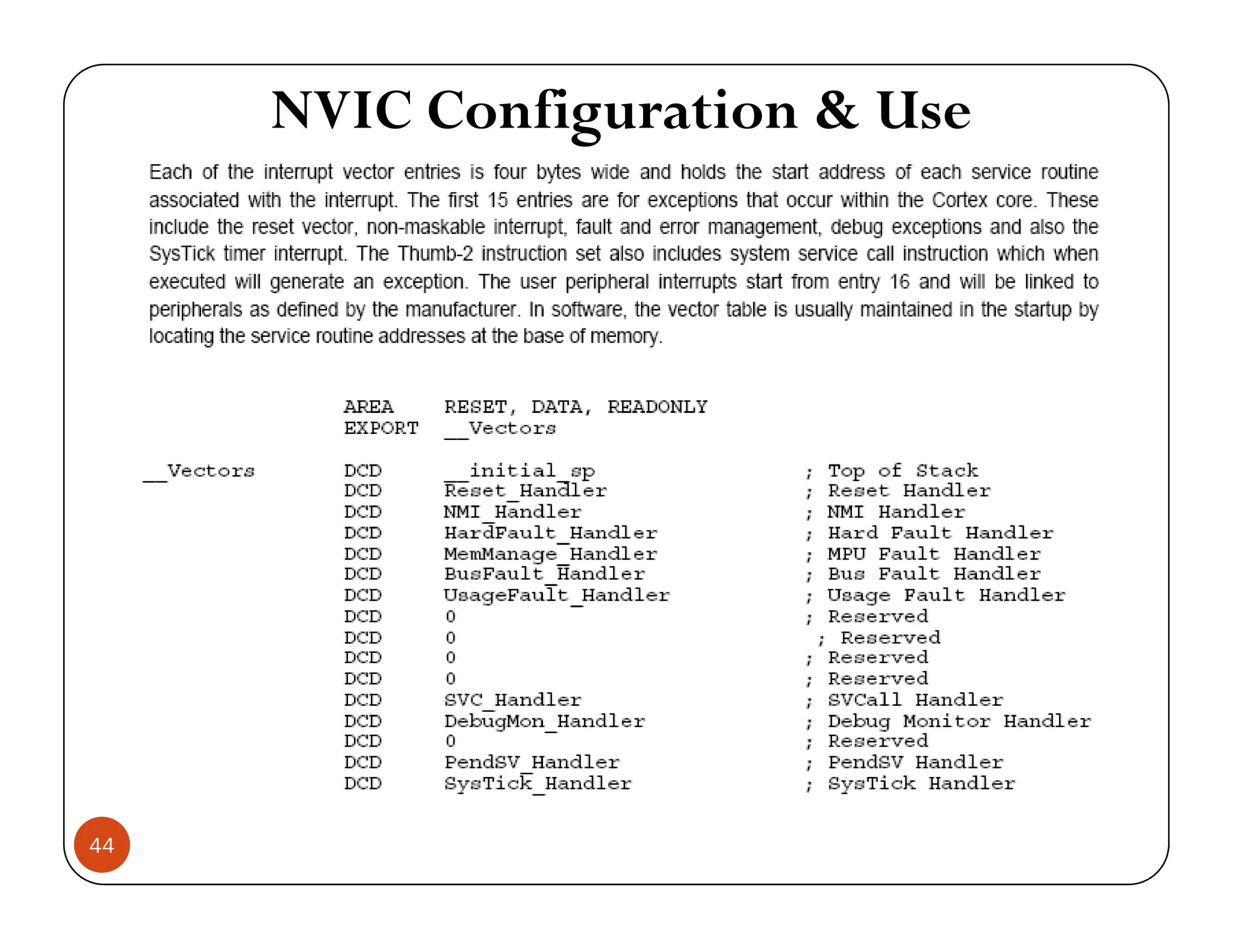

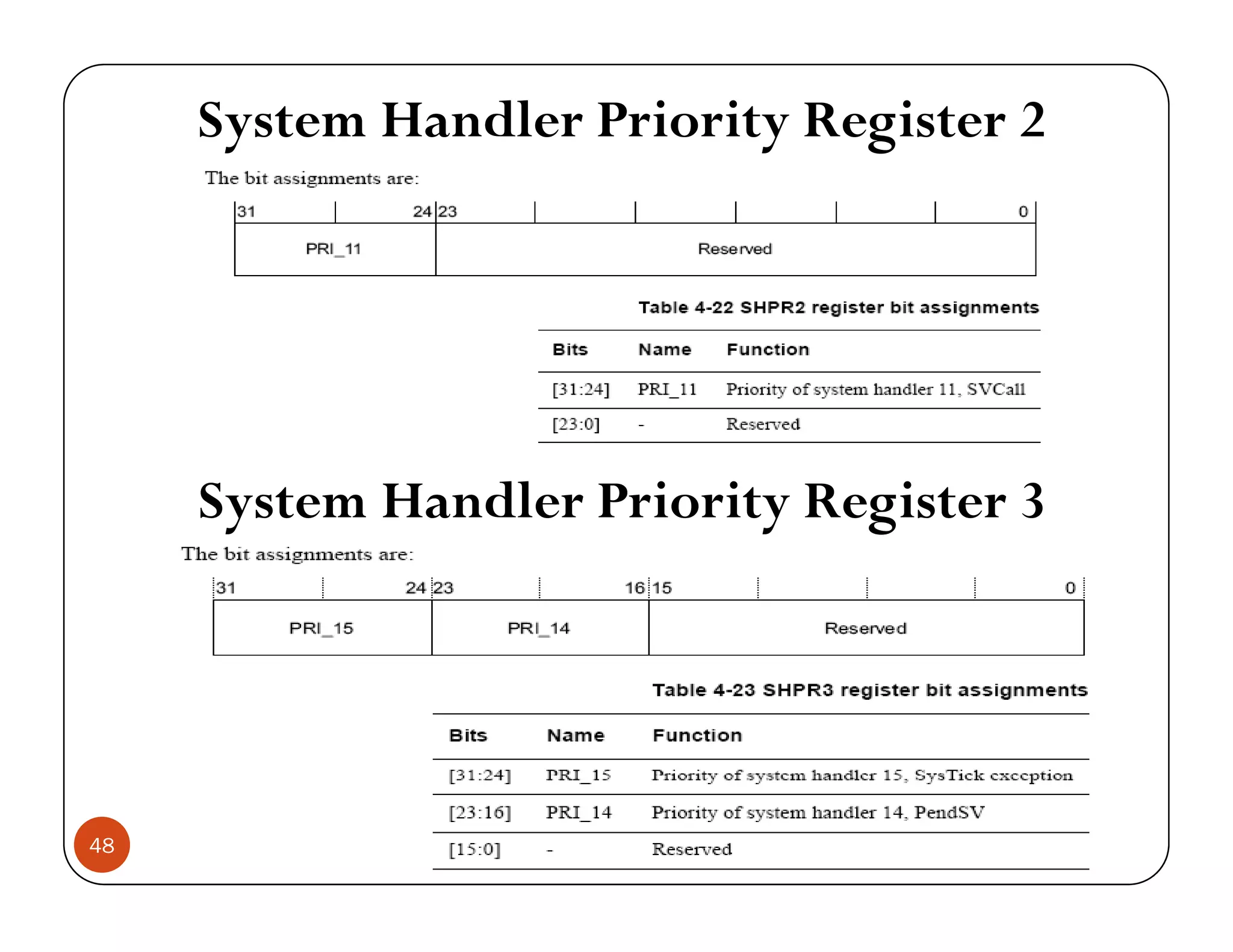

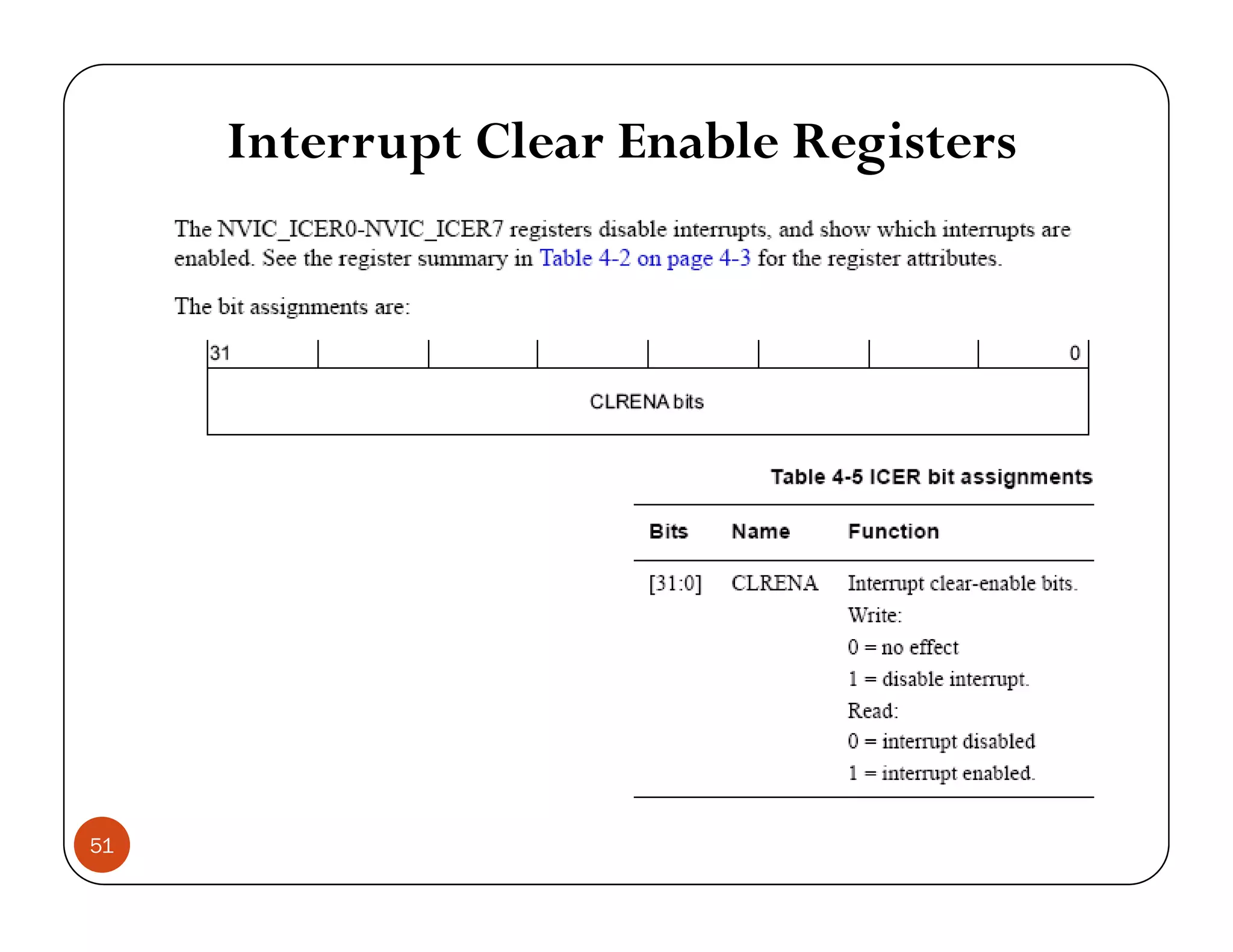

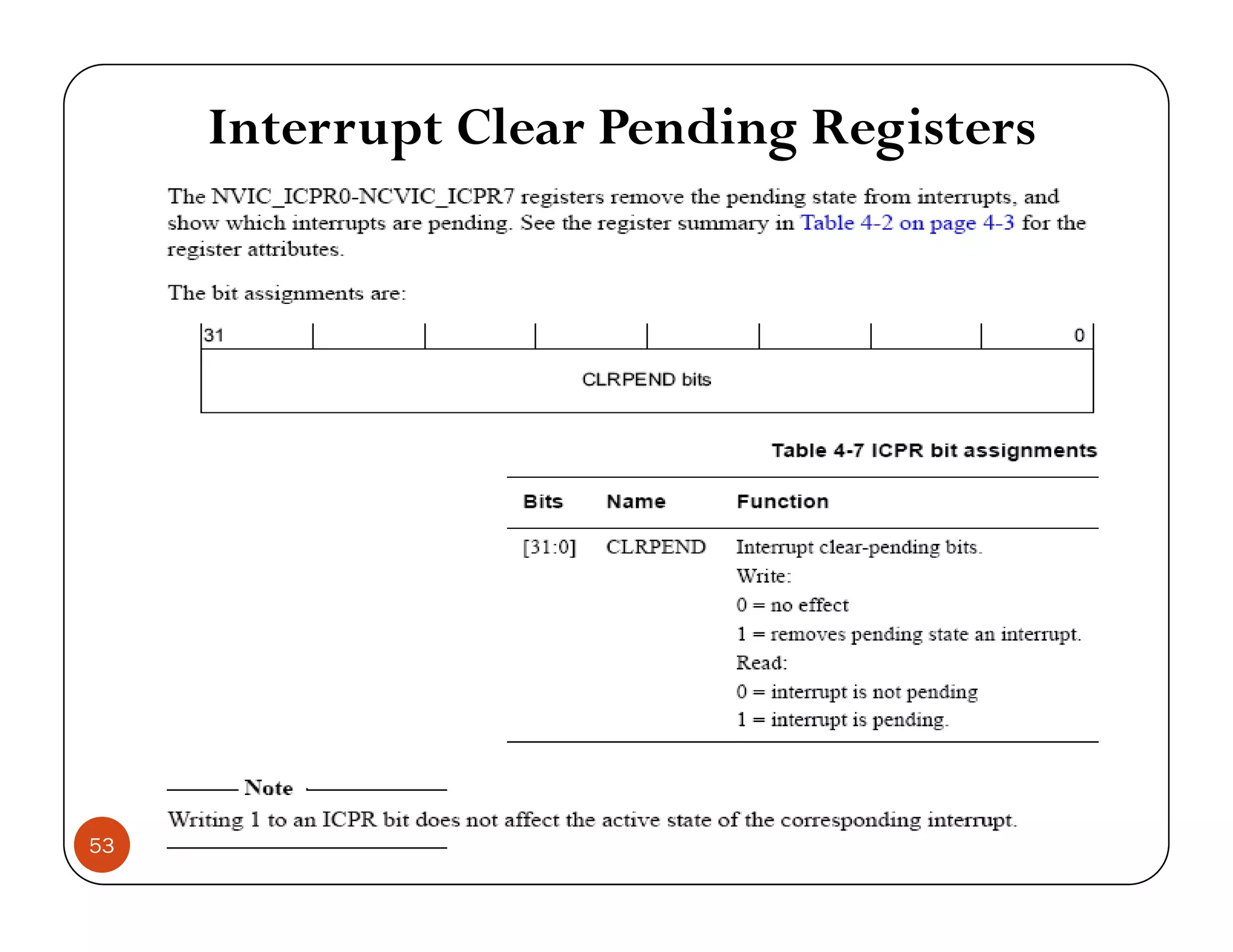

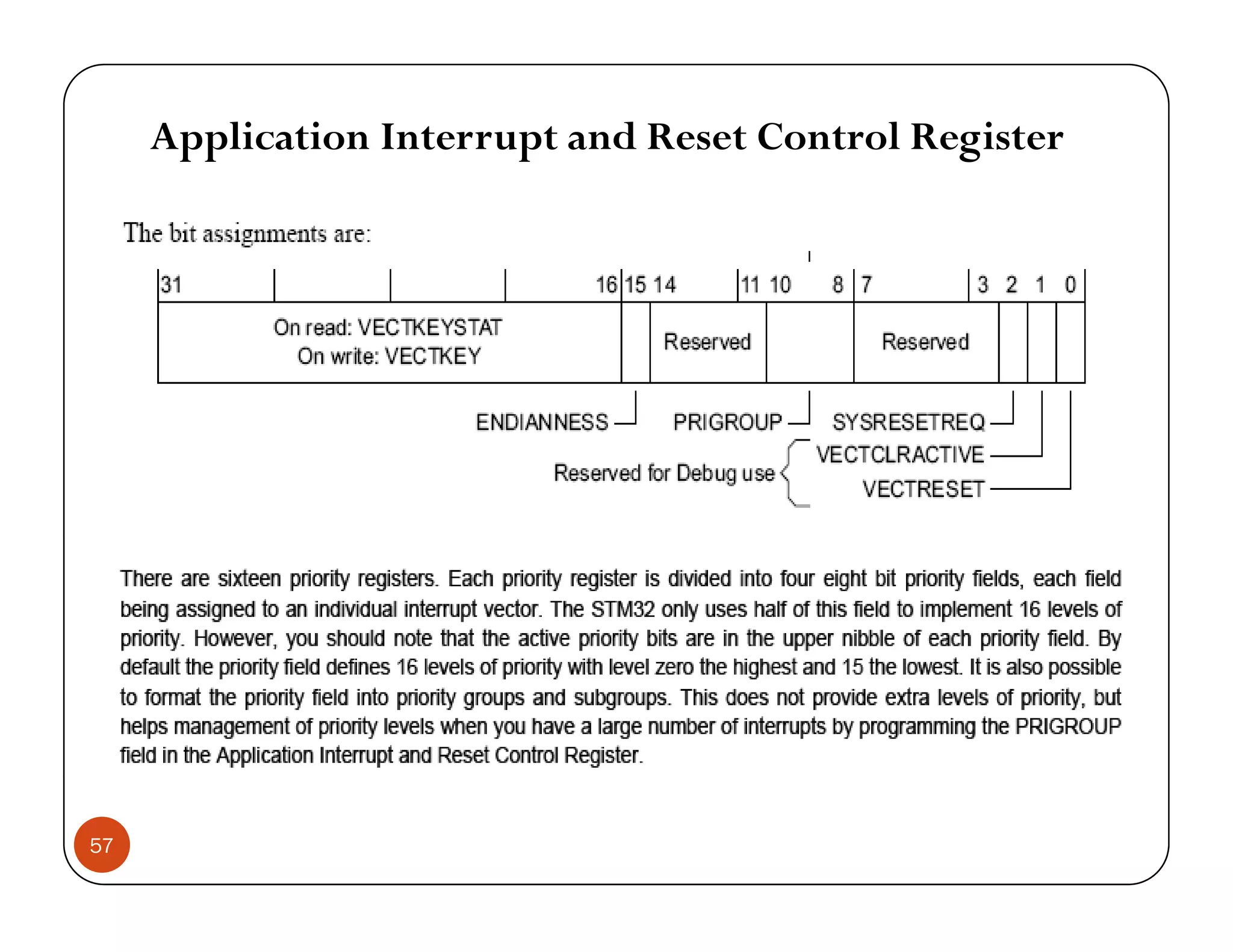

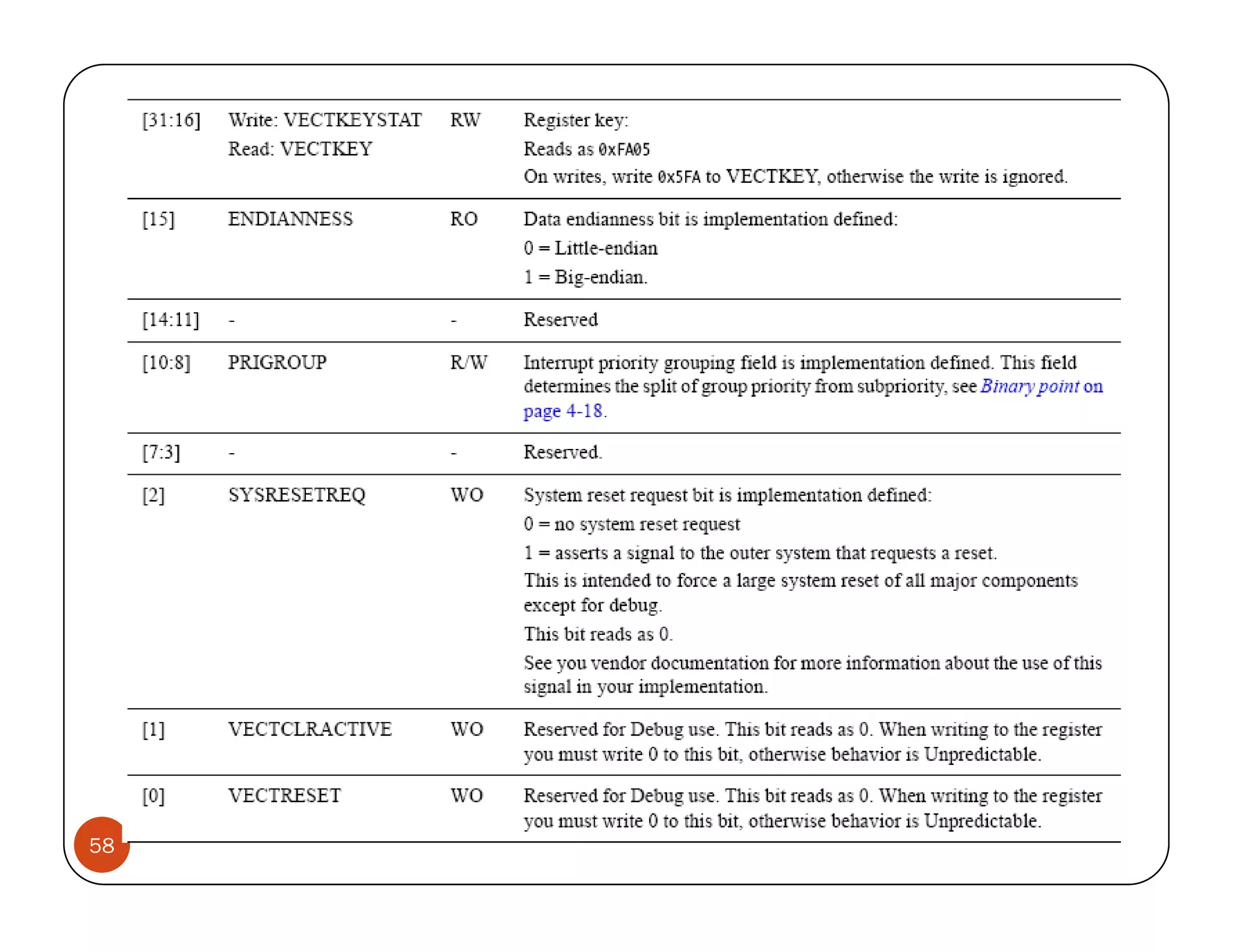

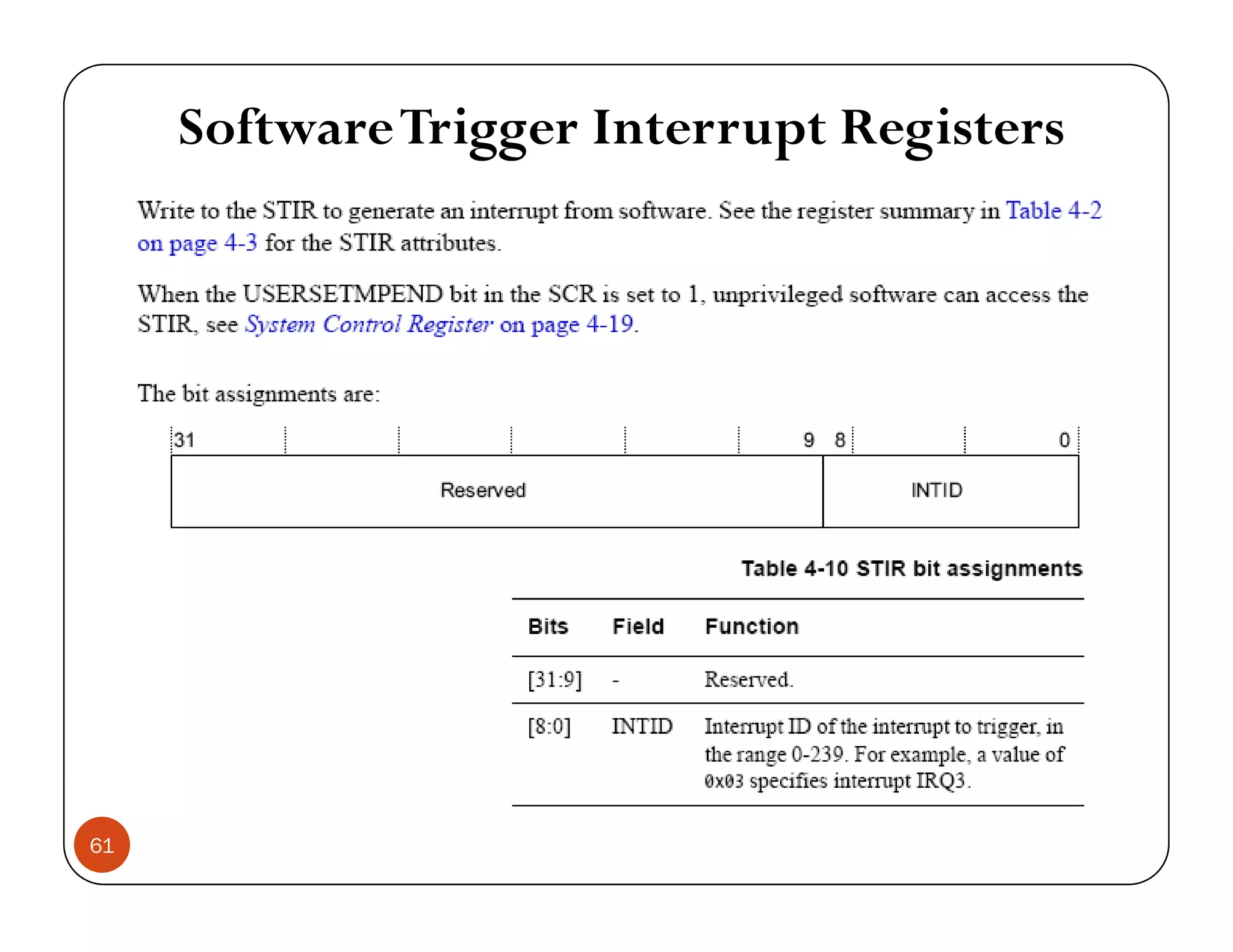

The document provides an overview of the ARM Cortex processor, highlighting its performance efficiency, low power consumption, and ease of use for 32-bit applications. It details the features of the Cortex M3 core, including its Harvard architecture, CPU registers, and the Nested Vectored Interrupt Controller (NVIC) for efficient interrupt handling. Additionally, it discusses memory management and various operational modes, emphasizing the benefits for both developers and end-users.