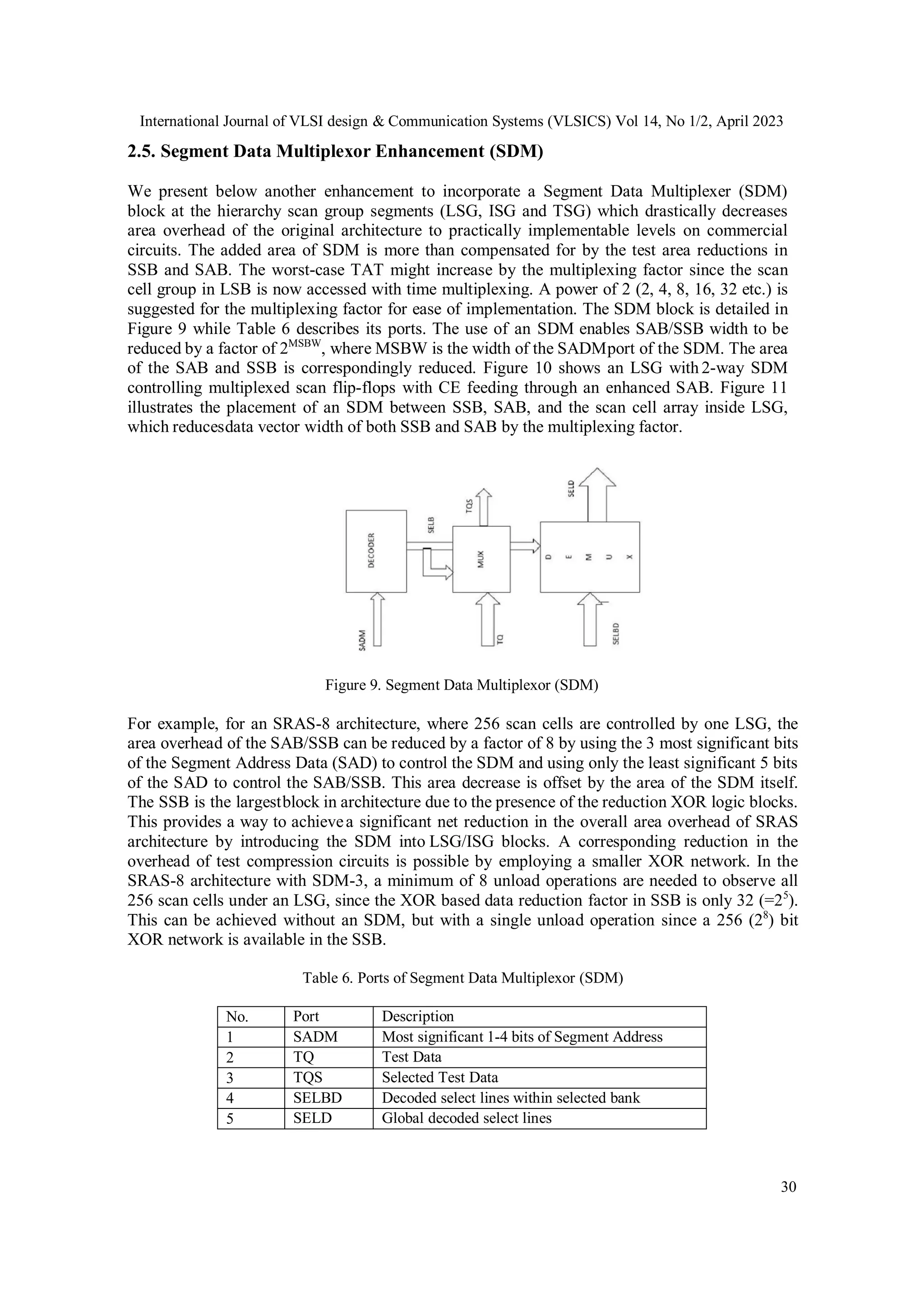

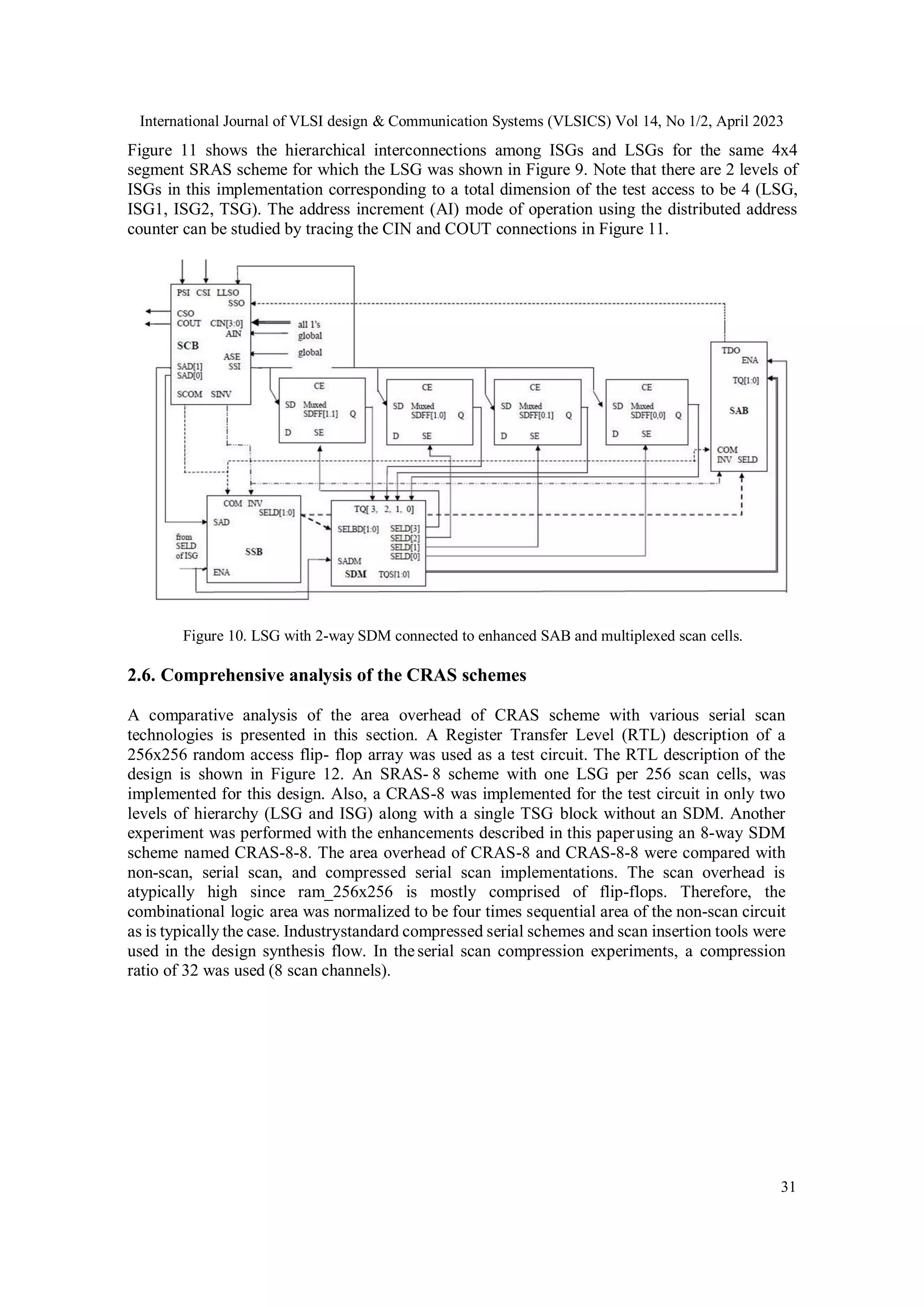

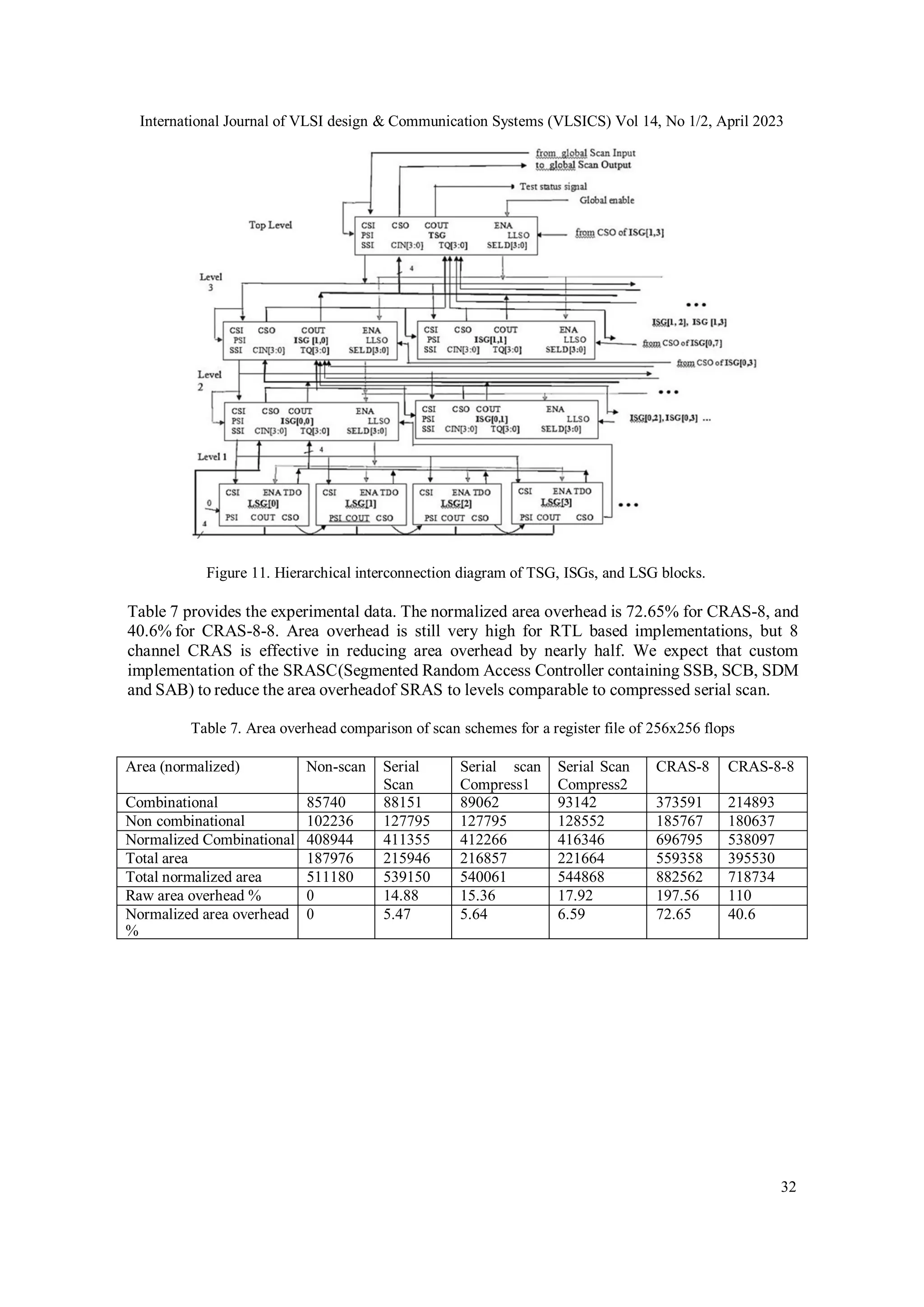

The document presents a detailed overview of the segmented random access scan (sras) architecture, which enhances integrated circuit testing by reducing area overhead and test application time through a combination of random access scan techniques and test compression. It discusses the limitations of traditional test methods and the efficiency gains achieved through hierarchical addressing, multiplexing, and improved data handling capabilities. Experimental results demonstrating the effectiveness of these enhancements in practical applications are also provided.

![International Journal of VLSI design & Communication Systems (VLSICS) Vol 14, No 1/2, April 2023 20 designing the power-delivery network. To mitigate such issues, various approaches have been proposed and practiced, such as loading constant values into serial scan cells that are not required in the current test pattern. However, all flops in the circuit under test (CUT) are clocked during shifting, and the clock network is a significant contributor to chip power. Therefore, tests can still dissipate high power even after mitigation. RAS [1~9] techniques reduce test power by clocking only the specific scan cells required for the current test pattern. Ando [1] first introduced the RAS technique, which was later adopted by others [2~3]. As thename implies, RAS allows access to any randomly chosen flip-flop in CUT, and changes only that element.Therefore, the power dissipation is extremely low relative to serial scan schemes. In attempts to lower overall TAT and data volume, additional techniques within RAS, such as test vector ordering based on pattern value distances and test output response compression using multiple-input signature registers (MISR) have been employed [4]. However, unknown, or unpredictable (X) data values would make MISRresults invalid and test coverage low. Total test time will still be high. Another team [5] describes a test vector compression combined with an iterative scan design technique while employing RAS row and column address decoding architecture. They employed two flavors of RAScells based on probability of having a 0 or 1 using ATPG vector data, along with compressing test data using coding schemes for adjacent 0’s against 1’s. However, their test flow may not be practical for largecommercial design teams that lack resources and time required to iterate design changes after ATPG has been performed before the design sign-off. Relying on a data driven DFT to achieve production level testcoverage may not be acceptable for such design teams. A cocktail approach on RAS to achieve low powerand overall high-test efficiency has been described [6] earlier. It incorporated the conventional RAS architecture and a cyclic random scan test scheme where output response of a scan cell group was taken as seed for the next random pattern. It is an overall test strategy with more efficient random test generation rather than improving RAS technique itself. Despite all the advantages, RAS schemes significantly increase IC chip area due to the additional logic circuitry and wiring to address each individual scan element. To mitigate routing overhead, one team [7] employed a scheme similar to static random-access memory in their progressive RAS architecture reducing both area and routing overhead compared to their previous work [4]. They progressively activated each row in the RAS grid structure by shifting the decoded row selection vector, while the decoded column selection vector selected one column per write operation, but all columns for read operation with read data feeding a MISR. However, unknown, or unpredictable (X) values would make MISR results invalid and test coverage low. Another group [8] designed a toggle scanflip-flop (TRAS) eliminating two global signals (i.e. scan-in and scan-enable) required in typical RAS structures. Toggling the target flip- flop effectively loads the required value, while captured value is shifted out via a bus structure when subsequent flip-flops are accessed. Using a grid architecture, they have mitigated routing overhead of conventional RAS to some extent. However, with toggling being the only way to set a value, loading a test vector would require loading new row/column addresses or shifting those already loaded in both directions which drastically adds to test time. Another paper [9] introduces a layout-based design approach named localized random-access scan (LRAS)to eliminate the global test enable signal while localizing row and column enable signals. RAS scan cellsare clustered into blocks based on the estimated layout data gathered from initial design stages. Each block is organized into a RAS structure and selected by decoding a block access bus while smaller uneven row and column address bus lines are routed to all the clustered](https://image.slidesharecdn.com/14223vlsi021-230517060511-ee38387e/75/AN-EFFICIENT-SEGMENTED-RANDOM-ACCESS-SCANARCHITECTURE-WITH-TEST-COMPRESSION-2-2048.jpg)

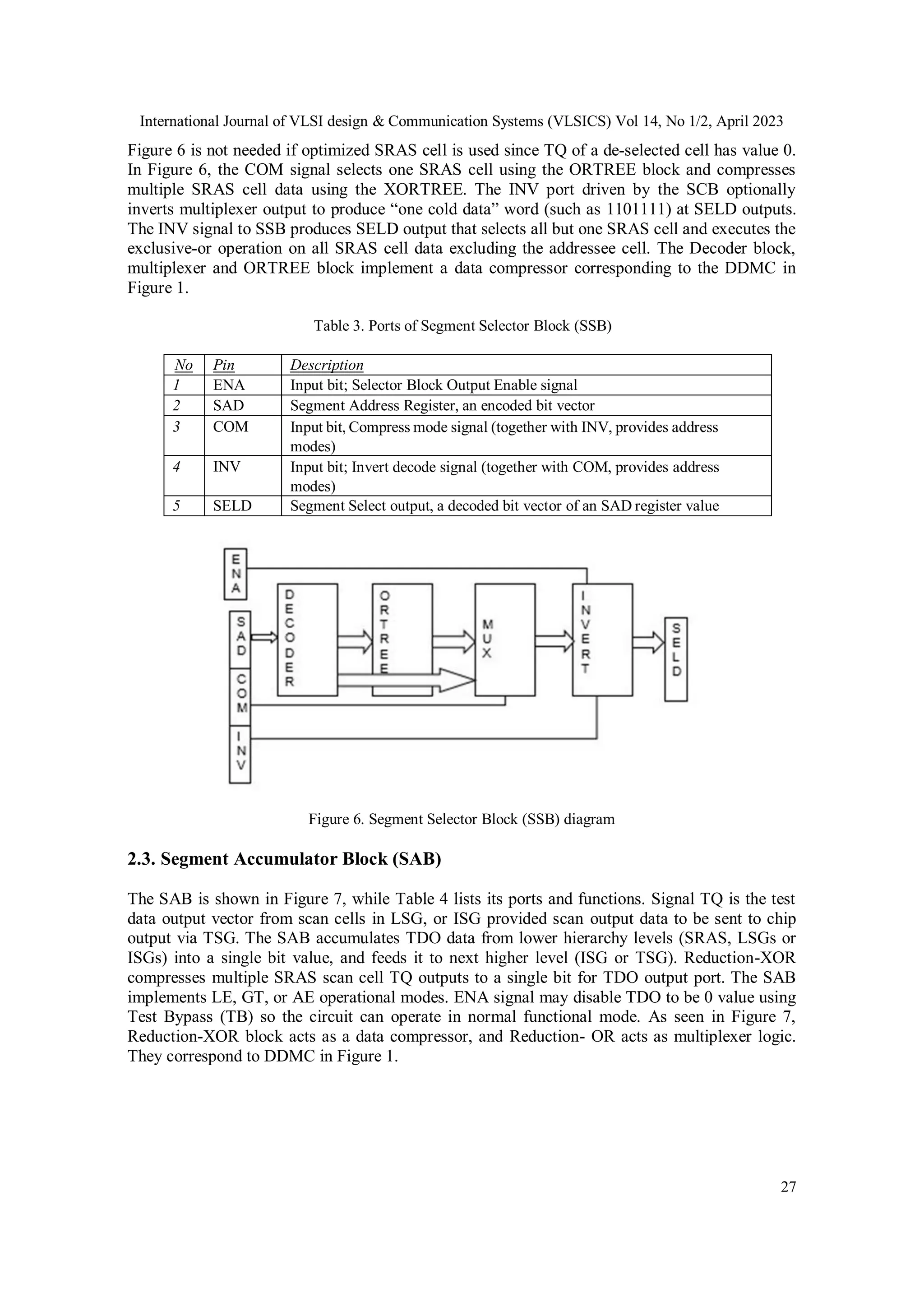

![International Journal of VLSI design & Communication Systems (VLSICS) Vol 14, No 1/2, April 2023 21 blocks for local decoding. The captured scan test results still need to be propagated out as conventional RAS does from each block which still makes the overall test time high and routing less than optimal. Compared to serial scan, RAS techniques reduce power dissipation during load and unload procedures. However, power reduction during capture procedures is not addressed. System-On- Chip (SOC) circuits are typically separated into several design blocks, each of which represent a physical block separately implemented to overcome capacity limitations of software tools for physical implementation. Some RAS techniques localize 2-D physical grid layouts to each physical block of the SOC. However, this approach does not fully mitigate the high wiring area overhead of large physical blocks. Use of MISR for compression without having a mechanism to observe individual capture data degrades test coverage in the presence of unknown (X) values for large circuits which typically contain a few circuit blocks that would need precise calculation/simulation of signal values. Test automation tools are incapable of providing such precision and thus unknown (X) values are inevitable on such blocks. The authors have introduced [10] hierarchical, compressed random access scan (CRAS-N) architecture, and a more constrained version named Segmented Random Access Scan (SRAS) which reduces test data volume (TDV), test application time (TAT) and routing overhead. In particular, the CRAS-N DFT technique provides a multi-dimensional addressing scheme without upper limits on the number of hierarchy levels in the test access structure of the design. SRAS simplifies the implementation of CRAS-N by keeping the number of scan cells or groups of scan cells addressed at each level of test hierarchy thesame. It also constrains the number of scan cells directly addressed to be a power of 2 for easy implementations. The rest of this paper is organized as follows. Section 2 presents the CRAS-N and SRAS architectures while individual subsections divulge details and block diagrams of individual components in those two architectures. Additionally, subsection 2.6 compares the area overhead of different SRAS schemes with commercially available serial scan compression scheme for a representative test circuit. Section 3 providesa brief conclusion. 2. COMPRESSED RAS-N AND SRAS DFT SCHEMES The CRAS-N scheme is described next having a 2-level hierarchy identified as a CRAS-2 scheme, wheredesign is partitioned as shown in Figure 1 with an example partition of 4 blocks. Each top and lower-level block contains its own Demultiplexer-Decompressor-Multiplexer- Compressor (DDMC) circuit block while the top level DDMC (marked #5 in Figure 1) interfaces chip level scan pins to lower level DDMC blocks. DDMC-2 decodes Row Address (RA) and generates signals to select one or more of DDMC circuit blocks in the four (4) quadrants. The Column Address (CA) is broadcast to DDMCs 1-4, and a Column Address Decoder (CAD) in each DDMC generates select signals for one or more scan cells in a respective quadrant. ATPG tools control CA and RA in each test pattern. Decoded CA lines are routed only within a single quadrant while decoded RA lines are routed from DDMC #5 to the quadrant level DDMC blocks thereby limiting the routing congestion. This CRAS-2 DFT technique reduces wiring area overheads of the CRAS DFT technique. Typically, RA, CA MODE signal, scan input (SI) and scan output(SO) are serially accessed to minimize the number of test pins at the top (i.e. IC chip) level. Figure 2 is an abstract block diagram of a design under CRAS-3 scheme with 3 levels of hierarchy wherethe circuit has been partitioned into 4 sub-circuits with each sub-circuit having its own DDMC block marked A - D in Figure 2. Each sub-circuit has been further partitioned into sub-sub-circuits with each sub-sub-circuit having its own DDMC block marked 00-03, 04-07, 08- 11 and 12-15 in Figure 2. A top level DDMC block marked “$” is used to interface at chip level](https://image.slidesharecdn.com/14223vlsi021-230517060511-ee38387e/75/AN-EFFICIENT-SEGMENTED-RANDOM-ACCESS-SCANARCHITECTURE-WITH-TEST-COMPRESSION-3-2048.jpg)

![International Journal of VLSI design & Communication Systems (VLSICS) Vol 14, No 1/2, April 2023 33 Figure 12. Verilog description of RTL circuit under test 3. CONCLUSION After thoroughly surveying different RAS architectures available in the published literature, a new CRAS-N/SRAS-N architecture to eliminate the high routing area overhead of traditional RAS was proposed. The implementation of SRAS-N architecture was described next in this paper. Finally, results comparing the area overhead of SRAS-8 architecture were presented after using commercially available scan compression tools on a simple experimental circuit. Careful selection of the segment size (256 in the experiment) and multiplexer width (8 in the experiment), along with custom implementation of SRASC was used to reduce area overhead of SRAS to levels comparable to compressed serial scan (about 20% overhead). The dream of providing the benefits of RAS (low test power and reduced test application time) to mainstream IC designers while keeping area overhead comparable to the latest compressed serial scan techniques is closer to reality with this work. REFERENCES [1] Ando, H, (1980) “Testing VLSI with Random Access Scan”, Digest of Computer Society International C o n f e r e n c e (COMPCON), pp. 50-52. [2] Wagner, K, (1983) “Design for Testability in the Amdahl 580”, Digest of Computer Society International C o n f e r e n c e (COMPCON), pp. 384-288. [3] Ito, N., (1991) “Automatic Incorporation of on-Chip Testability Circuits”, Proceedings of Design Automation Conference (DAC), pp. 529-534. [4] Baik, D, et al, (2004) “Random access scan: A solution to test power, test data volume and test time,” Proceedings of VLSI Design, pp. 883-888. [5] Hu, Y, et al,(2006) "Compression/Scan Co-Design for Reducing Test Data Volume, Scan-in Power Dissipation and Test Application Time", IEICE Transactions on Information and Systems, Vol. E89-D, No. 10, pp. 2616-2625. [6] Lin, C , e t a l , ( 2 0 0 5 ) “ A Cocktail Approach on Random Access Scan toward Low Power and High Efficiency Test,” Proceedings of International Conference on Computer-Aided-Design (ICCAD), pp. 94-99. [7] Baik, D, and Saluja, K, (2005) “Progressive Random Access Scan: A simultaneous solution to test power, test data volume and test time”, Proceedings of International Test Conference (ITC), no. 15.2, pp. 1-10. [8] Mudlapur, A, et al, (2005) “A Random Scan Architecture to Reduce Hardware Overhead”, Proceedings of International Test Conference (ITC), no. 15.1, pp. 1-9. [9] Hu, Y, (2008) “Localized Random Access Scan: Towards Low Area and Routing Overhead,” Proceedings of Design Automation Conference (ASPDAC), pp 565-569. [10] Oomman, B, and Karunaratne, M (2016) “Design-for-test techniques for a digital electronic circuit,” US patent #9423455, August](https://image.slidesharecdn.com/14223vlsi021-230517060511-ee38387e/75/AN-EFFICIENT-SEGMENTED-RANDOM-ACCESS-SCANARCHITECTURE-WITH-TEST-COMPRESSION-15-2048.jpg)

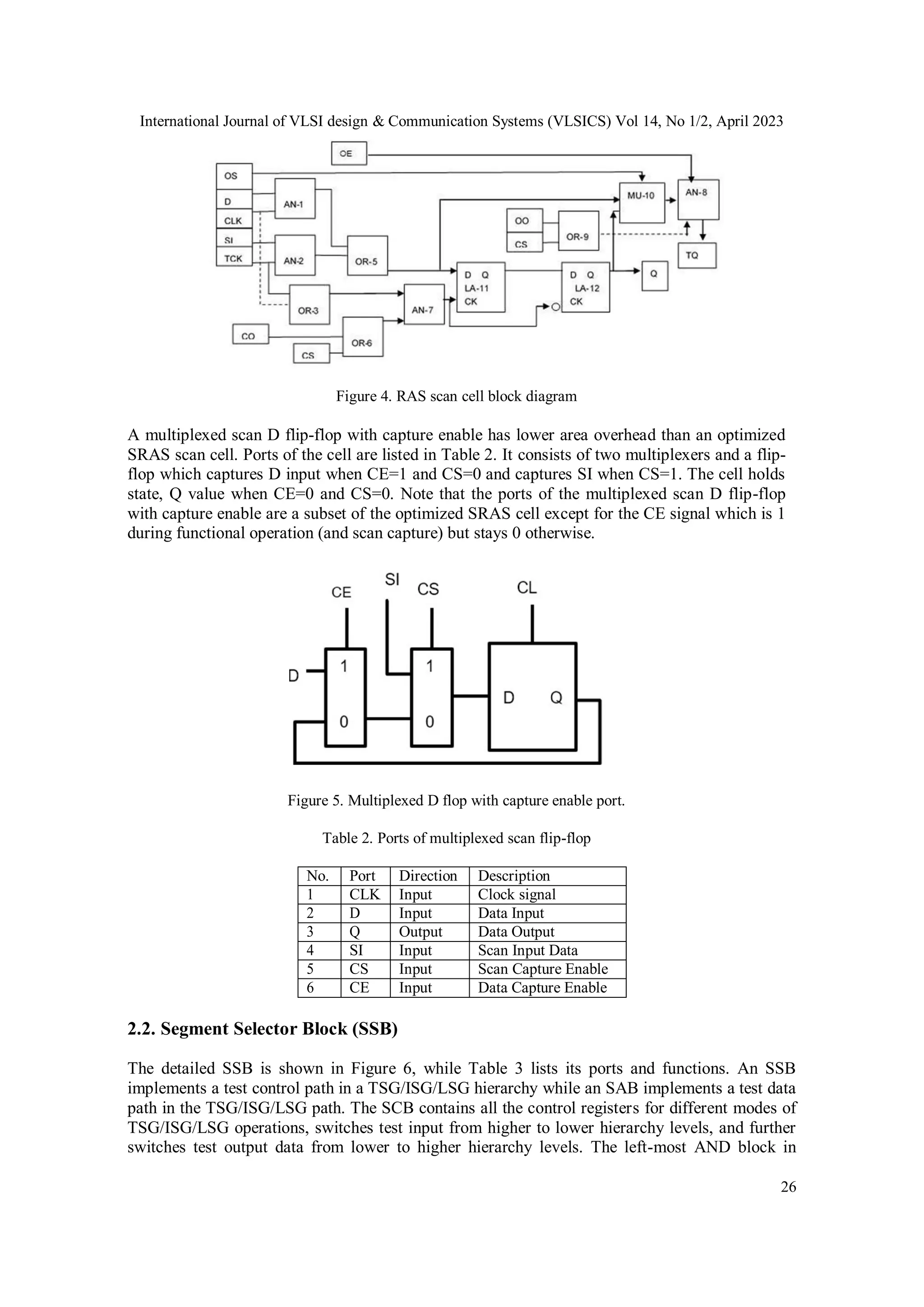

![International Journal of VLSI design & Communication Systems (VLSICS) Vol 14, No 1/2, April 2023 34 [11] Johnson, S, (1967) “Hierarchical Clustering Schemes”, Psychometrika, Vol. 32, No. 2, pp. 241-254. [12] Van de Goor, A (1991) “Testing Semiconductor Memories: Theory and Practice”, Chichester, UK: John Wiley & Sons, Inc., AUTHORS Maddumage Karunaratne earned his Ph.D. degree in electrical engineering from the University of Arizona, Tucson, AZ. Before joining Pitt-Johnstown in 2004, he gained fourteen years of industry experience working in the semiconductor industry performing software development, application engineering, design, testing and verification of digital integrated circuits. His research interests are in design and test automation, power analysis, and software development. He has authored numerous publications and holds several US patents. He can be reached at maddu@pitt.edu. Bejoy Oomman founded Genesys Testware test automation and consulting firm specializing in embedded memory test and self-repair. Over 30 years, he has been working in engineering and management positions in various test automation and systems design companies as a design and test engineer. Mr. Oomman has a MS in Computer Engineering from the University of Massachusetts. He can be reached at bejoygoomman@aim.com.](https://image.slidesharecdn.com/14223vlsi021-230517060511-ee38387e/75/AN-EFFICIENT-SEGMENTED-RANDOM-ACCESS-SCANARCHITECTURE-WITH-TEST-COMPRESSION-16-2048.jpg)