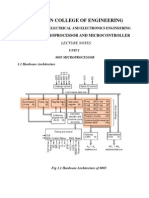

AVR CPUCore:

Block Diagram of A VR MCU Architecture:

(AVR Microcontroller is "Advanced Virtunl RISC" and MCU is the short tem of the Microcontroallen)

Data Bus B-bil

rop Blalu

Flash

Counter nd1Control

FrOgram

Momoy

2 x

ntorrupt

elio Gener

Purposo

Roginlrors

SPT

n

Instruction Walchdo

Decodor Timer

ALU Analog

Control Lines Compardtor

VO Module1

ala VO Module 2

pAM

VO Module n

w

EEPROM

VOLines

T o maximize the performance and parallelism, the AVR uses Harvard architecture (separate

memories and buses for program and data) with single level pipelining.

instruction is being executed, the next instruction is pre-

Single level pipelining: While one

etched irom the Program This concept enables instructions to be executed in

memory.

every clock cycle.

The Program memory is In-System Reprogrammable Flash memory.

There are 32, 8-bit GPRs are available R0-R31. 6 among this 32 registers used as three 16-

bit indirect address register pointers for Data Space addressing-enabling efficient address

calculations.

X,Y,Z: Indirect Address Register (X=R27:R26, Y=R29:R28 and Z=R31:R30).

One of these address pointers can also be used as an address pointer for look up tables in

Flash Program memory.

Fast-access Register File contains 32 x 8-bit general purpOse working registers with a single

clock cycle access time. This allows single-cycle Arithmetic Logic Unit (ALU) operation.

Every Program memory address contains a l6- or 32-bit instruction.

sections have dedicated

divided in two sections; both

space is

Program Flash memory

read/write protection.

Lock Bits for write and

section

o Boot program

o Application program section into the Application

writes

Flash memory

instruction:

SPM (Store Program Memory)) a page in the

SPM can be used to erase

reside in the Boot program section.

Section must write a page in the Program memory (that

is

already erased),

and to set

Togram memory, to

Boot Loader Lock bitsS.

the

general data Static RAM (SRAM), and consequently

is effcctively allocated in the

Stack size the usage of the SRAM.

Stack is limited

only the total SRAM size and

by

All must

Stack Pointer (SP) is read/write accessible in the V0 space.

user programs

initialize the SP in the reset routine (before subroutines or interrupts are executea.

stored on

During intemupts and subroutine calls, the return address Program Counter (PC) 15

the Stack.

A flexible interrupt module has its control registers in the /0 space with an additional

global interrupt enable bit in the Status Register.

All interTupts have a separate Intermupt Vector in the Interrupt Vector table. The intemupts

have priority in accordance with their Interrupt Vector position.

T h e lower the Interrupt Vector address, the

The O

higher the priority.

memory space contains 64 addresses for CPU peripheral functions as Control

Registers, SPI, and other 1/O functions,

SArithmetic Logic Unit - ALU: The high-performance AVR ALU operates in direct

connection with all the 32 general purpose working registers. Within a single clock cycle,

arithmetic operations between general

purpose registers or between a register and an immediate

are executed. The ALU

operations are divIded into three main categories arithmetic, logical,

and bit-functions. Some

implementations ot the architecture also provide a powertul multiplier

Supporting both signed/unsigned multiplication and fractional format. After an arithmetic

operation, the Status Register is also updated to reflect informmation about the result of the

operation.

Status Register:

I t contains information about the result of the most recently executed arithmetic instruction.

This information can be used for altering program flow in order to perform conditional

operations

NOTE: N's value is updated after all ALU operations, as specified in the Instruction Set

Reference

This register is not automatically stored when entering an interrupt routine and restored when

returning from an interrupt. This must be handled by software.

B 7

L C sREC

REG

Keaowe RUW

File:

General Purpose Register input/output

and flexibility, the following

I n order to achieve the required performance

schemes are supported by

the Register File:

and one 8-bit result input.

One 8-bit output operand

and one 8-bit result input.

Two 8-bit output operands

and result

one 16-bit input.

Two 8-bit output operands

and one 16-bit result input. in the C P .

One 16-bit output operand working registers

ofthe 32 general

purpose

the structure

below to all registers,

Figure showninstructions operating on the Register File have direct

access

Most of the

the

and single cycle

instructions. them directly into

are

a Data memory

address, mapping

is also assigned

Each register user Data Space. only work in

first 32 locations of the accessible. R16-R31 registers

RO-RI5 registers are

not immediately

immediate addressing mode.

Oxio

xmuur lew B

Onl

The X-register, Y register and Z-register:

added functions to their general purpose usage. These

R26..R3I have some

The registers DataSpace. The three

16-bit address pointes for

indirect addressing of the

registers are Z.

indirect address registers X, Y and

KH

15

7

KAegistar R26 (0x1A)

R27 (Ox1B)

15 YH

Y-Ogslor

7

R29 (01D) R28 (OxTC)

Z-1ogisler 7

R31 (0x 1F) R30 (01E)

Bit Name of the Description of the Bit

Bit

T h e 1-bit must be set for the interrupts to be enabled. The

1: Global

individual interrupt enable control is then performed in separate

Interrupt

Enable control registers.

I f 1-bit is cleared, none of the interrupts are enabled independent

of the individual interrupt enable settings.

has and

1-bit is cleared by after

hardware an interrupt occurred,

is set by the RETI instruction to enable subsequent interrupts.

I-bit can also be set and cleared by the application with the

SEI and CLI instructions.

6

T: Bit Copy The Bit Copy instructions BLD (Bit LoaD) and BST (Bit

Storage STore) the T-bit

use destination for the operated

as source or

bit

A bit from a register can be copied into T by the BST

A bit in T can be copied into a bit in a register by the BLD

H: Half Carry This flag H indicates a Halff Carry in some arithmetic operations.

Flag Carry at nibble (An auxiliary flag). It is useful in BCD arithmetic.

Ex:

S: Sign Bit S= N V (Ex-or between Negative FlagN and Two's

Complement Overflow Flag V)

V: Two's The Two's Complement Overflow Flag V supports two's

Complement complement arithmetic.

Overflow

Flag

N: Negative The Negative Flag N indicates a negative result in an arithmetic or

Flag Togic operation.

N=1; ifMSB of result is l; else N =0

Z: Zero Flag The Zero Flag Z indicates a zero result in an arithmetie or logic

operation.

Z= 1; if result =

00h; ese Z =

0

0 C: Carry Flag The Carry Flag C indicates a Carry in an arithmetie or logic

operation