Basic Electronics and Electrical

Engineering: ECE 249

UNIT V: Introduction to

Combinational Logic Circuits

Lecture No.: 20

Topic: Introduction to

Combinational Logic Circuits

Delivered By: Dr. Irfan Ahmad Pindoo

Head, Patent and Design Cell

Division of Research and Development

Intellectual Property Rights Cell

Introduction to Combinational Circuits

• Combinational logic is a type of digital logic which is implemented by Boolean

circuits, where the output is a pure function of the present inputs only.

• The combinational circuit do not use any memory.

• The previous state of input does not have any effect on

the present state of the circuit.

Prepared and Delivered By: Irfan Ahmad Pindoo 2

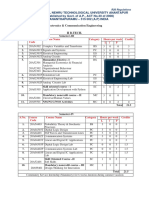

Design Procedure

Prepared and Delivered By: Irfan Ahmad Pindoo 3

Design Procedure:

BCD to Excess-3 Code Conversion

How many

Design of

inputs and

Truth Table

outputs

Simplification Design the

with K-map circuit

Prepared and Delivered By: Irfan Ahmad Pindoo 4

Design Procedure:

BCD to Excess-3 Code Conversion

STEP: 1 and 2

Prepared and Delivered By: Irfan Ahmad Pindoo 5

Design Procedure:

BCD to Excess-3 Code Conversion

Prepared and Delivered By: Irfan Ahmad Pindoo 6

Design Procedure:

BCD to Excess-3 Code Conversion

STEP: 3

Prepared and Delivered By: Irfan Ahmad Pindoo 7

Design Procedure:

BCD to Excess-3 Code Conversion

STEP: 3

Prepared and Delivered By: Irfan Ahmad Pindoo 8

Design Procedure:

BCD to Excess-3 Code Conversion

STEP: 4

Prepared and Delivered By: Irfan Ahmad Pindoo 9

Basic Electronics and Electrical

Engineering: ECE 249

UNIT V: Introduction to

Combinational Logic Circuits

Lecture No.: 21

Topic: Adder Circuits

Delivered By: Dr. Irfan Ahmad Pindoo

Head, Patent and Design Cell

Division of Research and Development

Intellectual Property Rights Cell

Half Adder

A combinational logic circuit with two inputs and two

outputs.

The half adder circuit add two single bits without any

carry.This circuit has two outputs carry and sum.

Prepared and Delivered By: Irfan Ahmad Pindoo 11

Half Adder

Prepared and Delivered By: Irfan Ahmad Pindoo 12

QUICK QUIZ (POLL)

If A and B are the inputs of a half adder, the sum is given by __________

a) A AND B

b) A OR B

c) A XOR B

d) A EX-NOR B

Prepared and Delivered By: Irfan Ahmad Pindoo 13

QUICK QUIZ (POLL)

Total number of inputs in a half adder is __________

a) 2

b) 3

c) 4

d) 1

Prepared and Delivered By: Irfan Ahmad Pindoo 14

Full Adder

A combinational logic circuit with 3 inputs and 2 outputs.

The Full adder circuit adds 3 bits including carry.

ABC ABC ABC ABC

A( BC BC ) A( BC BC )

A( B C ) A( BC )

Let B C D

AD AD

A D

A B C

Prepared and Delivered By: Irfan Ahmad Pindoo 15

Full Adder

Prepared and Delivered By: Irfan Ahmad Pindoo 16

Full Adder

Prepared and Delivered By: Irfan Ahmad Pindoo 17

QUICK QUIZ (POLL)

If A, B and C are the inputs of a full adder then the carry is given by

__________

a) A AND B OR (A OR B) AND C

b) A OR B OR (A AND B) C

c) (A AND B) OR (A AND B)C

d) A XOR B XOR (A XOR B) AND C

Prepared and Delivered By: Irfan Ahmad Pindoo 18

Implementation of Full Adder using Half Adders

Prepared and Delivered By: Irfan Ahmad Pindoo 19

Implementation of Ripple Carry Adder (RCA):4-bits

Prepared and Delivered By: Irfan Ahmad Pindoo 20

Basic Electronics and Electrical

Engineering: ECE 249

UNIT V: Introduction to

Combinational Logic Circuits

Lecture No.: 22

Topic: Subtractor Circuits

Delivered By: Dr. Irfan Ahmad Pindoo

Head, Patent and Design Cell

Division of Research and Development

Intellectual Property Rights Cell

Half Subtractor

Combinational circuit perform binary subtraction

accepts 2 inputs and provides two outputs: Difference

and Borrow

Prepared and Delivered By: Irfan Ahmad Pindoo 22

Full Subtractor

Performs subtraction of 3 bits

This circuit has three inputs and two outputs.

The three inputs A, B and C, denote the minuend, subtrahend, and

previous borrow, respectively.

The two outputs are: D and Bout

Sum(A, B,C) = ∑m (1, 2, 4, 7)

Bout(A, B,C) = ∑m (1,2,3,7)

Prepared and Delivered By: Irfan Ahmad Pindoo 23

Full Subtractor

Bout = A’B’C + A’BC’ + A’BC + ABC

= C(AB + A’B’) + A’B(C + C’)

= C( A XNOR B) + A’B

= C (A XOR B)’ + A’B

Prepared and Delivered By: Irfan Ahmad Pindoo 24

Implementation of Full Subtractor using Half

Subtractor

Prepared and Delivered By: Irfan Ahmad Pindoo 25

QUICK QUIZ (POLL)

The difference between half adder and full adder is __________

a) Half adder has two inputs while full adder has four inputs

b) Half adder has one output while full adder has two outputs

c) Half adder has two inputs while full adder has three inputs

d) All of the Mentioned

Prepared and Delivered By: Irfan Ahmad Pindoo 26

QUICK QUIZ (POLL)

How many AND, OR and EXOR gates are required for the configuration of full

adder?

a) 1, 2, 2

b) 2, 1, 2

c) 3, 1, 2

d) 4, 0, 1

Prepared and Delivered By: Irfan Ahmad Pindoo 27

Try Yourself

Design a 3 input digital circuit which produces high output for ODD decimal equivalent?

Prepared and Delivered By: Irfan Ahmad Pindoo 28

Decoder

What is a Decoder?

A combinational circuit that has ‘n’ input lines and maximum of 2𝑛 output lines.

One of these outputs will be active High based on the combination of inputs present, when

the decoder is enabled.

The outputs of the decoder are min terms of ‘n’ input variables lines when it is enabled

Prepared and Delivered By: Irfan Ahmad Pindoo 29

2x4 Decoder

Prepared and Delivered By: Irfan Ahmad Pindoo 30

2x4 Decoder

Delivered By: Irfan Ahmad Pindoo 31

2x4 Decoder

Therefore, the outputs of 2 to 4 decoder are nothing but

the min terms of two input variables A1 & A0, when enable,

E is equal to one. If enable, E is zero, then all the outputs of

decoder will be equal to zero.

Delivered By: Irfan Ahmad Pindoo 32

3x8 Decoder

Delivered By: Irfan Ahmad Pindoo 33

3x8 Decoder: Active High

Delivered By: Irfan Ahmad Pindoo 34

3x8 Decoder: Active Low

Delivered By: Irfan Ahmad Pindoo 35

Basic Electronics and Electrical

Engineering: ECE 249

UNIT V: Introduction to

Combinational Logic Circuits

Lecture No.: 23

Topic: Decoders and

Implementation of Boolean

Functions using Decoders

Delivered By: Dr. Irfan Ahmad Pindoo

Head, Patent and Design Cell

Division of Research and Development

Intellectual Property Rights Cell

Full Adder Design using 3:8 Decoder

Delivered By: Irfan Ahmad Pindoo 37

Full Subtractor Design using 3:8 Decoder

Delivered By: Irfan Ahmad Pindoo 38

3:8 Decoder using 2:4 Decoder

A2 A1 A0 HIGH OUTPUT

0 0 0 Y0

0 0 1 Y1

0 1 0 Y2

0 1 1 Y3

1 0 0 Y4

1 0 1 Y5

1 1 0 Y6

1 1 1 Y7

Delivered By: Irfan Ahmad Pindoo 39

4:16 Decoder

A3 Y0

A2

A1

4:16

Y15

Decoder

A0

EN

4:16 Decoder using 3:8 Decoder

4:16 Decoder using 2:4 Decoder

Basic Electronics and Electrical

Engineering: ECE 249

UNIT V: Introduction to

Combinational Logic Circuits

Lecture No.: 24

Topic: Multiplexers and

Implementation of Boolean

Functions using Multiplexers

Delivered By: Dr. Irfan Ahmad Pindoo

Head, Patent and Design Cell

Division of Research and Development

Intellectual Property Rights Cell

Multiplexer

The multiplexer, shortened to “MUX” or is a combinational logic circuit designed to switch one

of several input lines through to a single common output line by the application of a control

signal.

Multiplexers operate like very fast acting multiple position rotary switches connecting or

controlling multiple input lines called “channels” one at a time to the output.

Prepared and Delivered By: Irfan Ahmad Pindoo 44

Multiplexer

o Multiplexer is a combinational circuit that has maximum of 2n data inputs, ‘n’ selection lines

and single output line. One of these data inputs will be connected to the output based on the

values of selection lines.

o Since there are ‘n’ selection lines, there will be 2n possible combinations of zeros and ones. So,

each combination will select only one data input. Multiplexer is also called as Mux.

Prepared and Delivered By: Irfan Ahmad Pindoo 45

QUICK QUIZ (POLL)

Which combinational circuit is renowned for selecting a single input from multiple inputs &

directing the binary information to output line?

a) Data Selector

b) Data distributor

c) Both data selector and data distributor

d) DeMultiplexer

Prepared and Delivered By: Irfan Ahmad Pindoo 46

2:1 Multiplexer

Prepared and Delivered By: Irfan Ahmad Pindoo 47

QUICK QUIZ (POLL)

What is the function of an enable input on a multiplexer chip?

a) To apply Vcc

b) To connect ground

c) To active the entire chip

d) To active one half of the chip

Prepared and Delivered By: Irfan Ahmad Pindoo 48

4:1 Multiplexer

Selection Lines Output

S1 S0 Y

0 0 I0

0 1 I1

1 0 I2

1 1 I3

Prepared and Delivered By: Irfan Ahmad Pindoo 49

Boolean Function Implementation using Multiplexer

Implement f = 𝟏, 𝟑, 𝟓, 𝟔 using 4:1 MUX?

Prepared and Delivered By: Irfan Ahmad Pindoo 50

Boolean Function Implementation using Multiplexer

TRY YOURSELF

Implement f = 𝟎, 𝟐, 𝟒, 𝟓, 𝟔 using 4:1 MUX?

Prepared and Delivered By: Irfan Ahmad Pindoo 51

Full Adder Implementation using Multiplexer

TRY YOURSELF

Prepared and Delivered By: Irfan Ahmad Pindoo 52

Logic Gates Implementation using Multiplexer

AND GATE OR GATE

NOR GATE

NAND GATE

Prepared and Delivered By: Irfan Ahmad Pindoo 53

Logic Gates Implementation using Multiplexer

XNOR GATE

XOR GATE

NOT GATE

Prepared and Delivered By: Irfan Ahmad Pindoo 54

Multiplexer Trees

Multilplexers with higher number of inputs can be implemented by cascading

two or more multiplexers with less number of inputs.

Prepared and Delivered By: Irfan Ahmad Pindoo 55

4:1 MUX using 2:1 MUX

Prepared and Delivered By: Irfan Ahmad Pindoo 56

8:1 MUX using 4:1 MUX

Prepared and Delivered By: Irfan Ahmad Pindoo 57

8:1 MUX: Example

Question: Implement the Boolean function 𝒇(𝑨, 𝑩, 𝑪, 𝑫) = 𝟏, 𝟑, 𝟒, 𝟏𝟏, 𝟏𝟐, 𝟏𝟑, 𝟏𝟒, 𝟏𝟓 using Multiplexer?

Prepared and Delivered By: Irfan Ahmad Pindoo 58

8:1 MUX: Example

Question: Implement the Boolean function 𝒇(𝑨, 𝑩, 𝑪, 𝑫) = 𝟏, 𝟑, 𝟒, 𝟏𝟏, 𝟏𝟐, 𝟏𝟑, 𝟏𝟒, 𝟏𝟓 using Multiplexer?

Prepared and Delivered By: Irfan Ahmad Pindoo 59

Basic Electronics and Electrical

Engineering: ECE 249

UNIT V: Introduction to

Combinational Logic Circuits

Lecture No.: 25

Topic: Demultiplexers and

Encoder, Limitation of

conventional Encoder

Delivered By: Dr. Irfan Ahmad Pindoo

Head, Patent and Design Cell

Division of Research and Development

Intellectual Property Rights Cell

De-Multiplexer

De-Multiplexer is a combinational circuit that performs the reverse operation of Multiplexer.

It has single input, ‘n’ selection lines and maximum of 2𝑛 outputs.

The input will be connected to one of these outputs based on the values of selection lines.

Prepared and Delivered By: Irfan Ahmad Pindoo 61

De-Multiplexer

o The demultiplexer converts a serial data signal at the input to a parallel data at its output lines

as shown below.

Prepared and Delivered By: Irfan Ahmad Pindoo 62

1:4 De-Multiplexer

Prepared and Delivered By: Irfan Ahmad Pindoo 63

1:4 De-Multiplexer

Prepared and Delivered By: Irfan Ahmad Pindoo 64

1:8 De-MUX using 1:4 De-MUX

Prepared and Delivered By: Irfan Ahmad Pindoo 65

QUICK QUIZ (POLL)

To implement 1:8 de-mux how many 1:2 de-mux would be required?

a) 2

b) 4

c) 5

d) 6

Prepared and Delivered By: Irfan Ahmad Pindoo 66

Encoder

An encoder is a combinational circuit that performs the inverse operation of a decoder.

An encoder has 2𝑛 (or fewer) input lines and n output lines.

The output lines, as an aggregate, generate the binary code corresponding to the input value.

Prepared and Delivered By: Irfan Ahmad Pindoo 67

Encoder: Example

Qsn: Design an octal to binary encoder?

Prepared and Delivered By: Irfan Ahmad Pindoo 68

Encoder: Example

Qsn: Design an octal to binary encoder?

Prepared and Delivered By: Irfan Ahmad Pindoo 69

Encoder: Example

Qsn: Design an octal to binary encoder?

Prepared and Delivered By: Irfan Ahmad Pindoo 70

QUICK QUIZ (POLL)

How is an encoder different from a decoder?

a) The output of an encoder is a binary code for 1-of-N input

b) The output of a decoder is a binary code for 1-of-N input

c) The output of an encoder is a binary code for N-of-1 output

d) The output of a decoder is a binary code for N-of-1 output

Prepared and Delivered By: Irfan Ahmad Pindoo 71

QUICK QUIZ (POLL)

How many outputs will a decimal-to-BCD encoder have?

a) 4

b) 8

c) 12

d) 16

Prepared and Delivered By: Irfan Ahmad Pindoo 72

Limitations of Encoder

There is an ambiguity, when all outputs of encoder are equal to zero. Because, it could be the

code corresponding to the inputs, when only least significant input is one or when all inputs

are zero.

If more than one input is active High, then the encoder produces an output, which may not be

the correct code. For example, if both Y3 and Y6 are ‘1’, then the encoder produces 111 at the

output. This is neither equivalent code corresponding to Y3, when it is ‘1’ nor the equivalent

code corresponding to Y6, when it is ‘1’.

So, to overcome these difficulties, we should assign priorities to each input of encoder. Then,

the output of encoder will be the binary code corresponding to the active High inputs, which

has higher priority. This encoder is called as priority encoder.

Prepared and Delivered By: Irfan Ahmad Pindoo 73

Basic Electronics and Electrical

Engineering: ECE 249

UNIT V: Introduction to

Combinational Logic Circuits

Lecture No.: 26

Topic: Priority Encoder and

Magnitude Comparator (1-bit and

2-bits), Parity Circuit

Delivered By: Dr. Irfan Ahmad Pindoo

Head, Patent and Design Cell

Division of Research and Development

Intellectual Property Rights Cell

Priority Encoder

A priority encoder is an encoder circuit that includes the priority function. The operation of

the priority encoder is such that if two or more inputs are equal to 1 at the same time, the

input having the highest priority will take precedence.

In addition to the two outputs x and y, the circuit has a third output designated by V; this is a

valid bit indicator that is set to 1 when one or more inputs are equal to 1. If all inputs are 0,

there is no valid input and V is equal to 0.

The other two outputs are not inspected when V equals 0 and are specified as don’t-care

conditions.

Prepared and Delivered By: Irfan Ahmad Pindoo 75

Priority Encoder

Designing of 4X2 Priority Encoder

Prepared and Delivered By: Irfan Ahmad Pindoo 76

Priority Encoder

Designing of 4X2 Priority Encoder

Prepared and Delivered By: Irfan Ahmad Pindoo 77

Priority Encoder

Designing of 4X2 Priority Encoder

Prepared and Delivered By: Irfan Ahmad Pindoo 78

Magnitude Comparator

Another common and very useful combinational logic circuit is that of the Digital Comparator

circuit.

Digital or Binary Comparators are made up from standard AND, NOR and NOT gates that

compare the digital signals present at their input terminals and produce an output depending

upon the condition of those inputs.

Prepared and Delivered By: Irfan Ahmad Pindoo 79

1-Bit Magnitude Comparator

Another common and very useful combinational logic circuit is that of the Digital Comparator

circuit.

Digital or Binary Comparators are made up from standard AND, NOR and NOT gates that

compare the digital signals present at their input terminals and produce an output depending

upon the condition of those inputs.

Prepared and Delivered By: Irfan Ahmad Pindoo 80

2-Bit Magnitude Comparator

Step 1: Step 2 and 3:

Determine number of inputs and

outputs.

Prepared and Delivered By: Irfan Ahmad Pindoo 81

2-Bit Magnitude Comparator

Step 2 and 3: Step 4: K Maps

Prepared and Delivered By: Irfan Ahmad Pindoo 82

2-Bit Magnitude Comparator

Step 2 and 3: Step 4: K Maps

Prepared and Delivered By: Irfan Ahmad Pindoo 83

2-Bit Magnitude Comparator

Step 5: Logic Circuit

Prepared and Delivered By: Irfan Ahmad Pindoo 84

Parity Generation and Checking

Exclusive-OR functions are very useful in systems requiring error detection and correction

codes.

A parity bit is an extra bit included with a binary message to make the number of 1’s either

odd or even.

The message, including the parity bit, is transmitted and then checked at the receiving end

for errors.

The circuit that generates the parity bit in the transmitter is called a parity generator. The

circuit that checks the parity in the receiver is called a parity checker.

Prepared and Delivered By: Irfan Ahmad Pindoo 85

Parity Generation and Checking

Prepared and Delivered By: Irfan Ahmad Pindoo 86

Parity Generation and Checking

Prepared and Delivered By: Irfan Ahmad Pindoo 87