0% found this document useful (0 votes)

108 views2 pagesCMOS Analog VLSI Design Homework

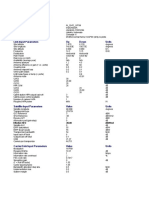

This document provides instructions for homework assignment 1 on CMOS analog VLSI design. It consists of 3 questions involving SPICE simulations of MOSFET circuits. Question 1 involves extracting transistor parameters from a test setup and comparing results for different geometries. Question 2 involves plotting ID-VG and ID-VD characteristics for a MOSFET. Question 3 involves designing a common source amplifier to meet gain and bandwidth specifications and performing DC, transient, and AC analyses to verify the design meets specifications. The homework is due on August 16th 2019 and must follow specific formatting and submission guidelines.

Uploaded by

Raja RamCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

108 views2 pagesCMOS Analog VLSI Design Homework

This document provides instructions for homework assignment 1 on CMOS analog VLSI design. It consists of 3 questions involving SPICE simulations of MOSFET circuits. Question 1 involves extracting transistor parameters from a test setup and comparing results for different geometries. Question 2 involves plotting ID-VG and ID-VD characteristics for a MOSFET. Question 3 involves designing a common source amplifier to meet gain and bandwidth specifications and performing DC, transient, and AC analyses to verify the design meets specifications. The homework is due on August 16th 2019 and must follow specific formatting and submission guidelines.

Uploaded by

Raja RamCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PDF, TXT or read online on Scribd

/ 2